# ENERGY AND AREA EFFICIENT MACHINE LEARNING ARCHITECTURES USING SPIN-BASED NEURONS

by

### HOSSEIN POURMEIDANI

M.S. University of Mississippi, 2018 M.S. Islamic Azad University, 2012 B.S. Islamic Azad University, 2010

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term

2021

Major Professor: Ronald F. DeMara

© 2021 Hossein Pourmeidani

#### **ABSTRACT**

Recently, spintronic devices with low energy barrier nanomagnets such as spin orbit torque-Magnetic Tunnel Junctions (SOT-MTJs) and embedded magnetoresistive random access memory (MRAM) devices are being leveraged as a natural building block to provide probabilistic sigmoidal activation functions for RBMs. In this dissertation research, we use the Probabilistic Inference Network Simulator (PIN-Sim) to realize a circuit-level implementation of deep belief networks (DBNs) using memristive crossbars as weighted connections and embedded MRAM-based neurons as activation functions. Herein, a probabilistic interpolation recoder (PIR) circuit is developed for DBNs with probabilistic spin logic (p-bit)-based neurons to interpolate the probabilistic output of the neurons in the last hidden layer which are representing different output classes. Moreover, the impact of reducing the Magnetic Tunnel Junction's (MTJ's) energy barrier is assessed and optimized for the resulting stochasticity present in the learning system. In p-bit based DBNs, different defects such as variation of the nanomagnet thickness can undermine functionality by decreasing the fluctuation speed of the p-bit realized using a nanomagnet. A method is developed and refined to control the fluctuation frequency of the output of a p-bit device by employing a feedback mechanism. The feedback can alleviate this process variation sensitivity of p-bit based DBNs. This compact and low complexity method which is presented by introducing the self-compensating circuit can alleviate the influences of process variation in fabrication and practical implementation.

Furthermore, this research presents an innovative image recognition technique for MNIST dataset on the basis of p-bit-based DBNs and TSK rule-based fuzzy systems. The proposed DBN-fuzzy system is introduced to benefit from low energy and area consumption of p-bit-based

DBNs and high accuracy of TSK rule-based fuzzy systems. This system initially recognizes the top results through the p-bit-based DBN and then, the fuzzy system is employed to attain the top-1 recognition results from the obtained top outputs. Simulation results exhibit that a DBN-Fuzzy neural network not only has lower energy and area consumption than bigger DBN topologies while also achieving higher accuracy.

To Sara and my dear parents.

### ACKNOWLEDGEMENTS

This work was supported in part by the Center for Probabilistic Spin Logic for Low-Energy Boolean and Non-Boolean Computing (CAPSL), one of the Nanoelectronic Computing Research (nCORE) Centers as task 2759.006, a Semiconductor Research Corporation (SRC) program sponsored by the NSF through CCF 1739635.

I would like to express my sincere gratitude to Dr. DeMara who provided an opportunity for me to join the CAL research team, and conduct my research under his supervision. He has kindly supported me during this dissertation research, and his insightful comments helped me to proceed my research along the right direction leading to several publications. I would also like to thank my committee members Dr. Vik Kapoor, Dr. Mingjie Lin, Dr. Rikard Ewetz, and Dr. Fan Yao for supporting me and my research.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                    | xii   |

|------------------------------------------------------------------------------------|-------|

| LIST OF TABLES                                                                     | xvi   |

| CHAPTER 1: INTRODUCTION AND MOTIVATION                                             | 1     |

| 1.1 Introduction And Related Works                                                 | 1     |

| 1.2 Need For In-Situ Adaptation For Process Variation Immunity                     | 3     |

| 1.3 Contributions Of The Dissertation                                              | 4     |

| 1.3.1 An Efficient Converter To Interpolate The Probabilistic Output Of The Neuron | s In  |

| DBNs                                                                               | 4     |

| 1.3.2 Mitigating The Effects Of Process Variation On The Performance And Accuracy  | cy Of |

| DBNs                                                                               | 5     |

| 1.3.3 High Accuracy DBN-Fuzzy Neural Networks using MRAM-based Stochastic          |       |

| Neurons                                                                            | 6     |

| CHAPTER 2: MAGNETIC TUNNEL JUNCTIONS (MTJ) CHARACTERISTICS AND                     |       |

| OPERATION                                                                          | 7     |

| 2.1 Spin Transfer Torque (STT) Switching                                           | 8     |

| 2.2 Voltage-Controlled Magnetic Anisotropy (VCMA) Switching                        | 9     |

| 2.3 Spin-Orbit Torque (SOT) Switching                                              | 11    |

| 2.4 Post-CMOS Roles Of Spin-Based Digital Circuits                                 | 12    |

| 2.4.1 MTJ-Based MRAM                                                               | 12    |

| 2.4.2 Non-Volatile Logic Gates                                                     | 15    |

| 2.4.3 Non-Volatile Clockless Look-Up Table (C-LUT)               | 18 |

|------------------------------------------------------------------|----|

| 2.4.4 Spin-MTJ Based Non-Volatile Flip-Flop                      | 19 |

| 2.4.4 Spin-MTJ Based Non-Volatile Full Adder                     | 20 |

| 2.5 Fabrication Of Magnetic Tunnel Junctions                     | 22 |

| 2.5.1 Junction Size                                              | 23 |

| 2.5.2 Growth Of Multilayer Structure                             | 24 |

| 2.5.3 Molecular Beam Epitaxy (MBE)                               | 24 |

| 2.5.3.1 E-Beam Evaporation                                       | 25 |

| 2.5.3.2 Sputtering Deposition                                    | 25 |

| 2.5.3.3 Ion Beam Sputtering Deposition                           | 26 |

| 2.5.4 Lithography                                                | 27 |

| 2.5.4.1 Photolithography                                         | 27 |

| 2.5.4.2 E-Beam Lithography                                       | 28 |

| 2.5.5 Patterning Of Fe/Mgo/Fe System                             | 29 |

| 2.5.6 Fabrication Of Device Using Pseudo/Metal Masking Procedure | 30 |

| CHAPTER 3: BACKGROUND                                            | 32 |

| 3.1 Deep Belief Network (DBN)                                    | 32 |

| 3.2 Embedded Mram-Based Neuron                                   | 34 |

| 3.3 Probabilistic Inference Network-Simulator (PIN-Sim)          | 38 |

| CHAPTER 4: PROBABILISTIC INTERPOLATION RECODER                   | 45 |

|    | 4.1 Sample And Count Based PIR (SC-PIR)                                 | 45 |

|----|-------------------------------------------------------------------------|----|

|    | 4.2 Sample And Shift Based PIR (SS-PIR)                                 | 48 |

|    | 4.3 PIR For Spiking Neural Networks                                     | 49 |

|    | 4.4 Simulation Results                                                  | 50 |

|    | 4.4.1 Accuracy Analyses                                                 | 52 |

|    | 4.4.2 Performance Analyses                                              | 54 |

|    | 4.4.3 Area Analysis                                                     | 56 |

|    | 4.4.4 Fault Analysis                                                    | 58 |

|    | 4.5 Recoder Based Conversion Circuit                                    | 61 |

|    | 4.6 Python-Driven Simulation Framework                                  | 63 |

|    | 4.7 MNIST Dataset Evaluation                                            | 64 |

| CI | HAPTER 5: ELECTRICALLY-TUNABLE STOCHASTICITY FOR SPIN-BASED             |    |

| NI | EUROMORPHIC CIRCUITS                                                    | 67 |

|    | 5.1 Effects Of Process Variation On The Probabilistic Behavior Of P-Bit | 67 |

|    | 5.2 Variation-Less P-Bit Based Dbn As The Baseline                      | 69 |

|    | 5.3 Proposed Variation-Immune P-Bit Implementation                      | 70 |

|    | 5.4 P-Bit With Temporal Redundancy                                      | 72 |

|    | 5.5 P-Bit With Feedback                                                 | 74 |

|    | 5.6 Process Variation Analysis Of SOT Perpendicular Nanomagnets In Dbns | 77 |

|    | 5.6.1 Individual Variation                                              | 79 |

| 5.6.1.1 Anisotropy Field Variation                             | 80    |

|----------------------------------------------------------------|-------|

| 5.6.1.2 Diameter Variation                                     | 81    |

| 5.6.1.3 Thickness Variation                                    | 82    |

| 5.6.2 Impact Of Multiple Sources Of Variation                  | 84    |

| 5.6.3 SOT P-Bit With Feedback                                  | 86    |

| CHAPTER 6: HIGH ACCURACY DBN-FUZZY NEURAL NETWORKS USING MRAM- | -     |

| BASED STOCHASTIC NEURONS                                       | 90    |

| 6.1 Fundamentals Of Fuzzy Systems                              | 90    |

| 6.2 Rule-Based Fuzzy Models                                    | 91    |

| 6.2.1 Linguistic Fuzzy Model                                   | 92    |

| 6.2.1.1 Relational Representation Of A Linguistic Model        | 93    |

| 6.2.1.2 Max-Min (Mamdani) Inference                            | 94    |

| 6.2.1.3 Multivariable Systems                                  | 95    |

| 6.2.1.4 Defuzzification                                        | 96    |

| 6.2.1.5 Singleton Model                                        | 97    |

| 6.2.2 Takagi-Sugeno-Kang Model                                 | 98    |

| 6.2.2.1 Inference Mechanism                                    | 99    |

| 6.2.2.2 TSK Model As A Quasi-Linear Systems                    | 99    |

| 6.2.3 Modeling Dynamic Systems                                 | . 100 |

| 6.3 Building Fuzzy Models                                      | 101   |

| 6.3.1 Structure And Parameters                        | 102 |

|-------------------------------------------------------|-----|

| 6.3.2 Knowledge-Based Design                          | 104 |

| 6.3.3 Data-Driven Acquisition/Tunning Of Fuzzy Models | 105 |

| 6.3.3.1 Least-Square Estimation Of Consequents        | 105 |

| 6.3.3.2 Temple-Based Modeling                         | 106 |

| 6.3.3.3 Neuro-Fuzzy Modeling                          | 107 |

| 6.3.3.4 Fuzzy Clustering                              | 108 |

| 6.4 Proposed Dbn-Fuzzy Neural Network                 | 109 |

| 6.5 Simulation Results                                | 112 |

| CHAPTER 7: CONCLUSION                                 | 118 |

| 7.1 Summary                                           | 118 |

| 7.2 Future Directions                                 | 120 |

| I IST OF REFERENCES                                   | 122 |

# LIST OF FIGURES

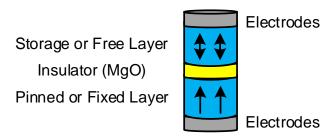

| Figure 1: Magnetic tunnel junction (MTJ).                                                    | 8  |

|----------------------------------------------------------------------------------------------|----|

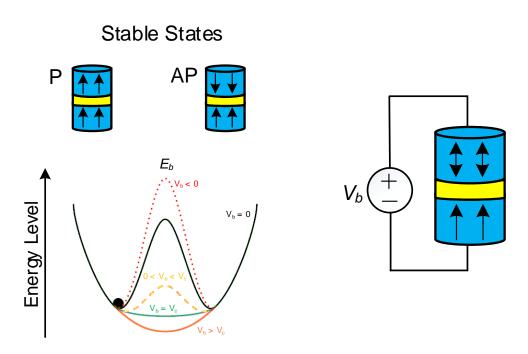

| Figure 2: Structure and stable states of VCMA-MTJ device                                     | 0  |

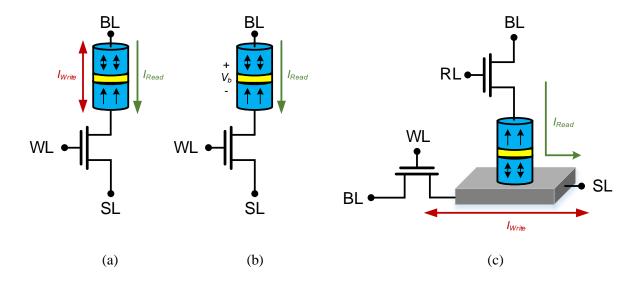

| Figure 3: Memories devices: (a) STT-MRAM (b) VCMA-MeRAM (c) SOT-MRAM                         | 3  |

| Figure 4: The structure of 4-bit NAND-SPIN.                                                  | 5  |

| Figure 5: The structure of NV-AND / NV-NAND.                                                 | 6  |

| Figure 6: the structure of NV-OR / NV-NOR                                                    | 7  |

| Figure 7: The structure of NV-XOR / NV-XNOR                                                  | 8  |

| Figure 8: Spin-MTJ based Non-Volatile Flip-Flop [69]                                         | 0  |

| Figure 9: The schematic of Single-bit full adder (FA)                                        | 1  |

| Figure 10: The structure of full adder: (a) SUM sub-circuit (b) CARRY sub-circuit            | 1  |

| Figure 11: An example of DBN structure including a visible layer                             | 3  |

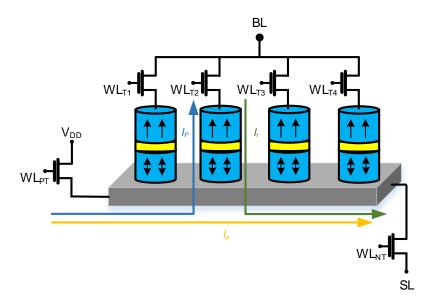

| Figure 12: The diagram of the embedded MRAM-based neuron                                     | 5  |

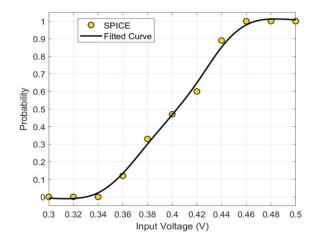

| Figure 13: Output probability of MRAM-based neuron vs. its input voltage                     | 6  |

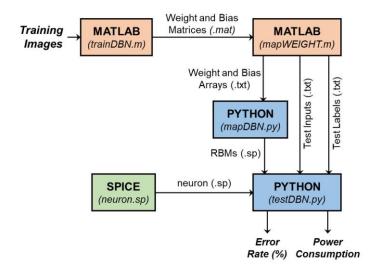

| Figure 14: The block diagram of PIN-Sim framework including five main modules [12] 4         | 0  |

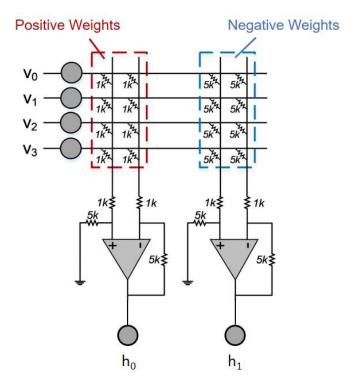

| Figure 15: An RBM hardware implementation. Two resistive arrays are leveraged along wit      | h  |

| differential amplifiers to implement both positive and negative weights. The embedde         | d  |

| MRAM-based neurons are used to evaluate the activation functions. The fluctuating output     | ıt |

| voltage of the neurons are integrated through an RC circuit to generate the output of the    | e  |

| proposed RBM structure                                                                       | 4  |

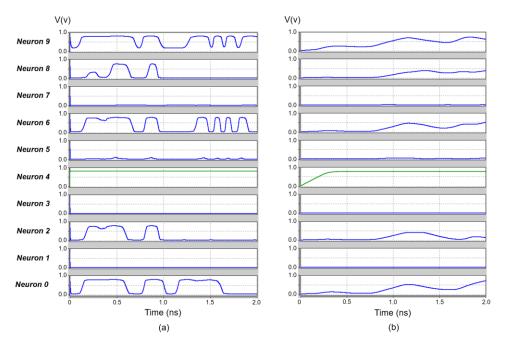

| Figure 16: Output voltages of a $784 \times 200 \times 10$ DBN for a sample digit of "4": (a | ı) |

| Probabilistic output of the p-bit devices, (b) Output of the integrator circuit [12]         | 5  |

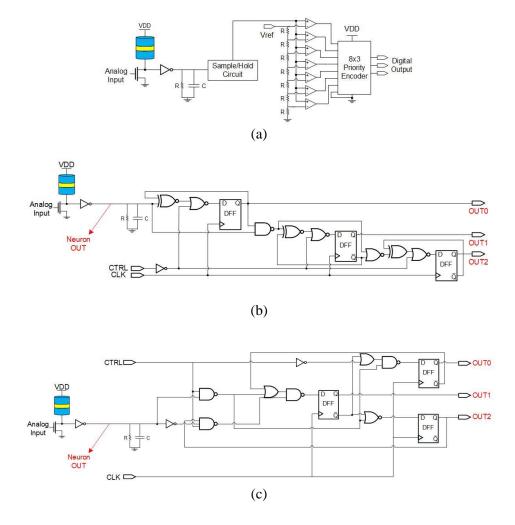

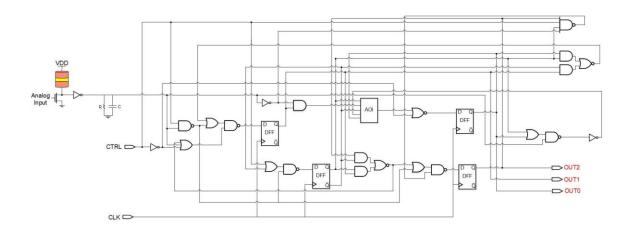

| Figure 17: (a) 3-bit ADC circuit, (b) 3-bit SC-PIR circuit, and (c) 3-bit SS-PIR circuit, 4  | 7  |

| Figure 18: Timing waveforms of (a) 3-bit SC-PIR circuit and (b) 3-bit SS-PIR circuit 48        |

|------------------------------------------------------------------------------------------------|

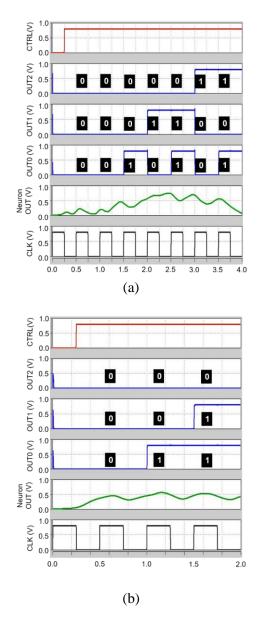

| Figure 19: Simulation framework utilized for application-level simulations. (a) subset of      |

| MNIST dataset with 100 test images, (b) a 784×200×10 DBN developed for MNIST pattern           |

| recognition application, (c) hardware implementation of the 784×200×10 DBN using PIN-Sim       |

| tool, (d) stochastic MRAM-based neuron (p-bit), and (e) PIR unit used to interpolate the       |

| probabilistic output of the p-bit based output neurons to digital output                       |

| Figure 20: Error Rate for 3-bit, 4-bit and 5-bit SC-PIR and SS-PIR                             |

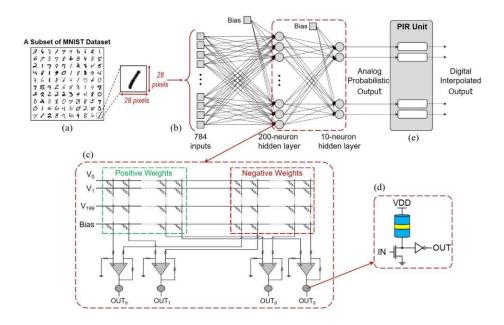

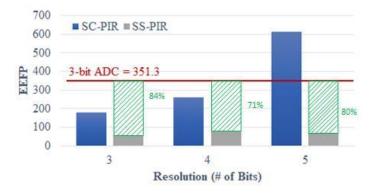

| Figure 21: EEP for 3-bit, 4-bit and 5-bit SC-PIR and SS-PIR                                    |

| Figure 22: EEFP for 3-bit, 4-bit and 5-bit SC-PIR and SS-PIR                                   |

| Figure 23: 3-bit recoder circuit. 61                                                           |

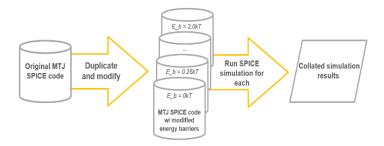

| Figure 24: MTJ Energy barrier simulation using Python scripting                                |

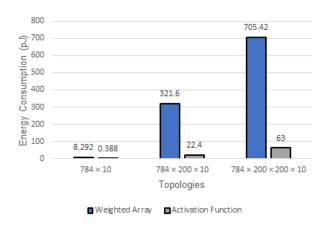

| Figure 25: Energy consumption of weighted array and activation function for several DBN        |

| topologies                                                                                     |

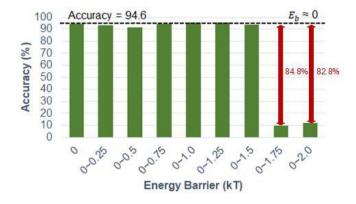

| Figure 26: Effects of neuron's energy barriers on the DBN accuracy                             |

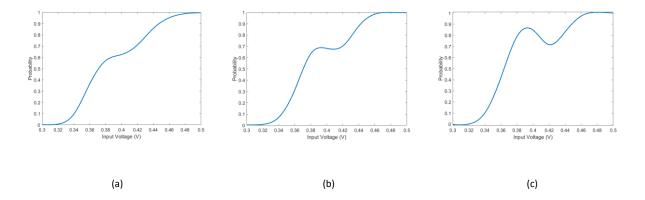

| Figure 27: (a) Output probability of MRAM-based neuron for (a) EB = 1.5 kT, (b) EB = 1.75      |

| kT, and (c) EB = 2.0 kT                                                                        |

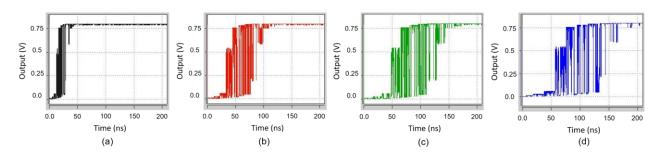

| Figure 28: Output of MRAM-based neuron vs. time for different energy barriers (a) $EB = 0.5$   |

| kT, (b) EB = 1.0 kT, (c) EB = 1.5 kT, and (c) EB = 2.0 kT                                      |

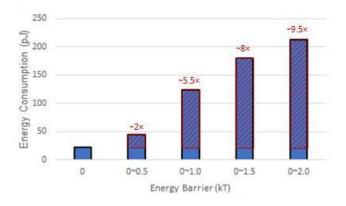

| Figure 29: Influence of increasing energy barrier on energy consumption for 784×200×10         |

| topology                                                                                       |

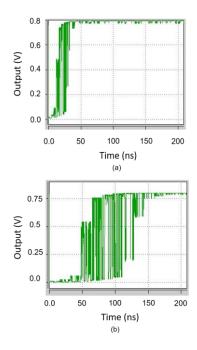

| Figure 30: Device configuration with feedback for the embedded MRAM-based p-bit 74             |

| Figure 31: Tuning the effective energy barrier through electrical feedback. (a) Measurement of |

| the output fluctuations of the device without feedback for EB = 1.5 kT. (b) Measurement of     |

| the output fluctuations of the device with the feedback implemented through a simple resistor                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| of value 100 K $\square$ for EB = 1.5 kT                                                                                                        |

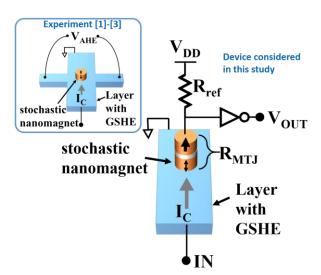

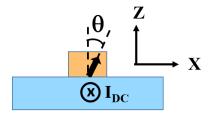

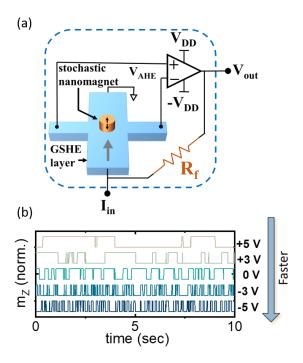

| Figure 32: The diagram of the probabilistic device (p-bit) with perpendicular magnetic                                                          |

| anisotropy (PMA) as a binary stochastic neuron for DBNs [222],[224],[226]. The experiments                                                      |

| in [222],[224],[226] used AHE to read the magnetization state. This read scheme can be                                                          |

| replaced by an MTJ. The magnetization state of the weak perpendicular anisotropy free layer                                                     |

| can be read through the resistance change of an MTJ as proposed in [194]                                                                        |

| Figure 33: Tunability of the average magnetization component in the Z-direction while the                                                       |

| magnetization lies in the ZX-plane                                                                                                              |

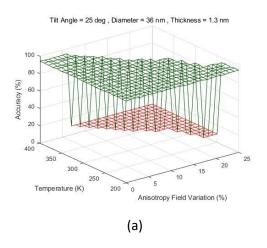

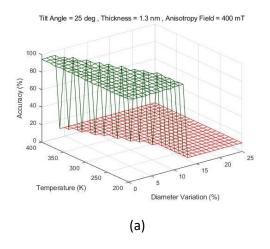

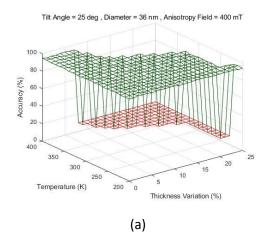

| Figure 34: Accuracy of p-bit based DBN versus $\sigma HM$ for: (a) Temperature of 200K to 400K,                                                 |

| (b) Tilt angles of 10 degrees to 30 degrees                                                                                                     |

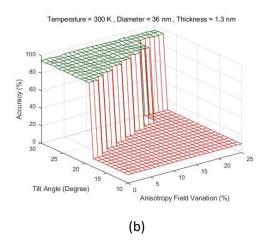

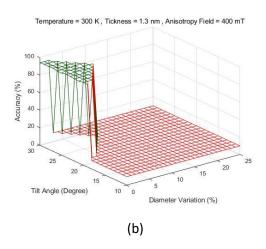

| Figure 35: Accuracy of p-bit based DBN versus $\sigma$ d for: (a) Temperature of 200K to 400K, (b)                                              |

| Tilt angles of 10 degrees to 30 degrees                                                                                                         |

| Figure 36: Accuracy of p-bit based DBN versus $\sigma$ tf for: (a) Temperature of 200K to 400K, (b)                                             |

| Tilt angles of 10 degrees to 30 degrees                                                                                                         |

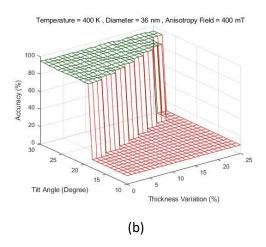

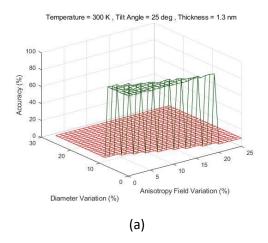

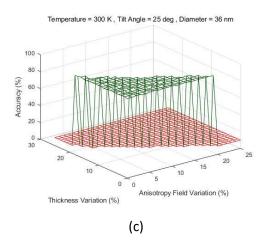

| Figure 37: Accuracy of p-bit based DBN for: (a) $\sigma d$ vs. $\sigma HK$ , (b) $\sigma tf$ vs. $\sigma d$ , (c) $\sigma tf$ vs. $\sigma HK$ . |

| 85                                                                                                                                              |

| Figure 38: Tuning the effective energy barrier through electrical feedback. (a) Measurement                                                     |

| configuration with the feedback implemented through a simple resistor of value 360 K $\square$ . (b)                                            |

| Measurement of the output fluctuations of the device for various feedback configurations 86                                                     |

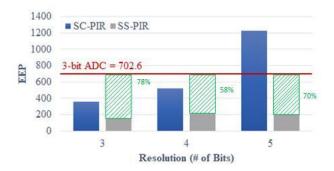

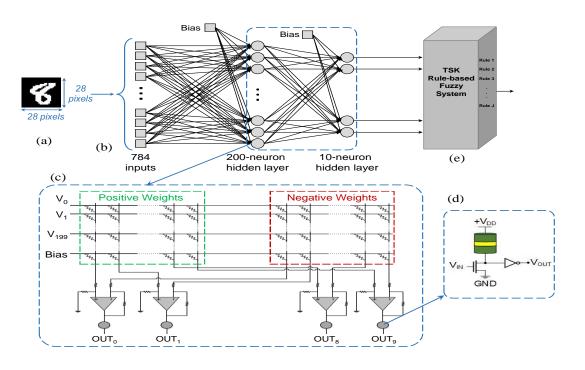

| Figure 39: The DBN-Fuzzy system used for application-level simulations. (a) an input image                                                      |

| from MNIST dataset (b) a 784×200×10 DBN developed for MNIST pattern recognition                                                                 |

| application, (c) hardware implementation of the 784×200×10 DBN using PIN-Sim tool, (d)        |

|-----------------------------------------------------------------------------------------------|

| stochastic MRAM-based neuron (p-bit), and (e) TSK rule-based fuzzy system 110                 |

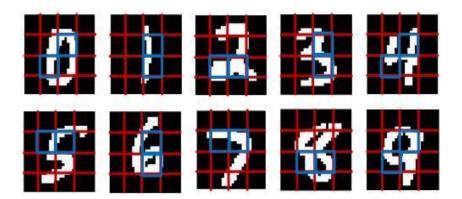

| Figure 40: Input image subregions and identified patterns for each input digit in MNIST       |

| dataset                                                                                       |

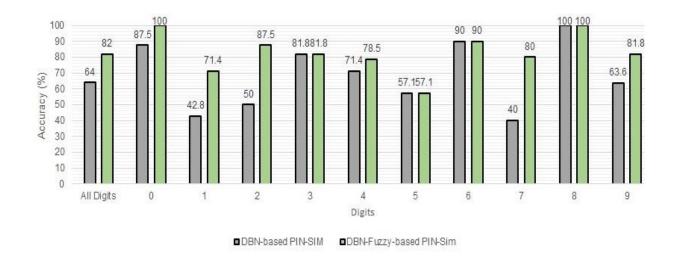

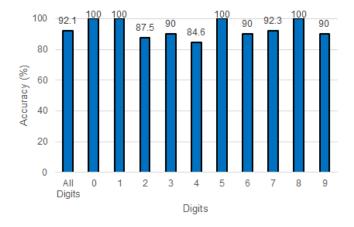

| Figure 41: PIN-Sim Top-1 Accuracy for MNIST dataset                                           |

| Figure 42: TSK Rule-based Fuzzy System Top-1 Accuracy for MNIST data set                      |

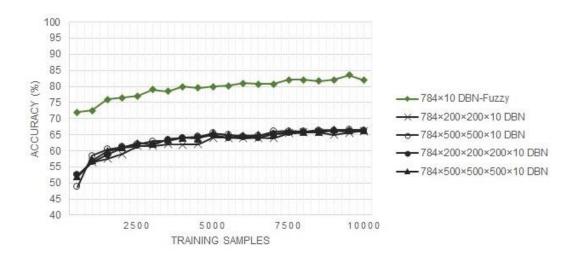

| Figure 43: Accuracy of 784 × 10 DBN-Fuzzy neural network and four different DBN               |

| topologies for various training samples.                                                      |

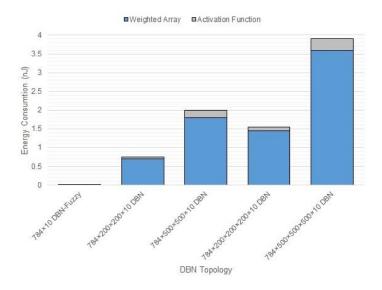

| Figure 44: Energy Consumption for $784 \times 10$ DBN-Fuzzy neural network and four different |

| DBN topologies                                                                                |

# LIST OF TABLES

| Table 1: Comparison between some MTJ-based memories                                          |

|----------------------------------------------------------------------------------------------|

| Table 2: Truth table of AND/NAND.                                                            |

| Table 3: Truth table of OR/NOR.                                                              |

| Table 4: Truth table of XOR/XNOR.                                                            |

| Table 5: Characteristics of LUT designs.                                                     |

| Table 6: Various hardware implementations for DBN architecture                               |

| Table 7: PIN-Sim Tunable Parameters and their default values                                 |

| Table 8: Parameters Use for Modeling and Simulation [13].                                    |

| Table 9: The binary outputs generated by ADC-based and PIR-based interpolation circuits for  |

| an input digit "2" from the MNIST dataset of handwritten digits.                             |

| Table 10: Various DBN hardware implementations with a focus on activation function           |

| structure                                                                                    |

| Table 11: Power and energy consumption of weighted array, activation function and            |

| interpolation circuits for several DBN topologies                                            |

| Table 12: Area of weighted array, activation function and interpolation circuits for several |

| DBN topologies relative to the area occupied by a single p-bit-based neuron                  |

| Table 13: Stuck-at fault table for 4-bit SC-PIR.                                             |

| Table 14: Stuck-at fault table for 5-bit SS-PIR                                              |

| Table 15: Performance comparison between 3-bit, 4-bit and 5-bit recoder circuits             |

| Table 16: Crisp and fuzzy information in systems                                             |

| based neur | on      |            |         |           |            |       |         |        |        |       |        | 117    |

|------------|---------|------------|---------|-----------|------------|-------|---------|--------|--------|-------|--------|--------|

| network ar | nd four | different  | DBN     | topologi  | es relativ | e to  | the are | ea occ | cupied | by a  | single | p-bit- |

| Table 17:  | Area of | f weighted | d array | y and act | ivation f  | uncti | on for  | 784    | × 10 I | DBN-I | Fuzzy  | neura  |

### **CHAPTER 1: INTRODUCTION AND MOTIVATION**

### 1.1 INTRODUCTION AND RELATED WORKS

The Restricted Boltzmann machine (RBM) is one of the well-known classes of unsupervised learning approach [1]. A set of RBMs connected hierarchically can be utilized to create deep belief networks (DBNs) with outstanding learning abilities such as natural language understanding for various applications [2]. Most of the research on RBM and DBN has focused on software implementations. Albeit the software implementation of DBNs on current von-Neumann-based platforms (e.g. CPU, GPU, FPGA) provides flexibility, it incurs significant power dissipation and high latency due to inherent data communication costs, a.k.a. the "memory wall" issue. There are various hardware implementations for RBMs such as FPGAs [3], [4] and CMOS multi-core processors [5] aiming to tackle existing software limitations.

Recently, processing-in-memory based solutions using emerging non-volatile memories (NVMs) such as resistive RAM (RRAM) [6], [7] and phase change memory (PCM) [8] are set forth to be used within the DBN architecture. NVMs provide the capability of performing logic beyond data storage by bringing an intrinsic computation parallelism alleviating the data transfer bottleneck. NVMs are typically used as weighted connections interconnecting building blocks in RBMs.

The existing FPGA-based acceleration solutions show 25- 145× speedup compared to software implementations [3], [4]. However, these designs have noticeable limitations such as constrained clock frequencies, routing congestion, and resource deficiencies due to the significant embedded memory utilization for weighted connections and activation functions. In [9] optimization methods to reduce memory requirements for weights and biases are proposed. However, in order to implement each of the activation functions, a random number generator (RNG), dedicated

piecewise linear approximator (PLA), and comparators are still required which increases area and energy consumption per neuron. As an alternative method, the stochastic CMOS-based RBM implementation have been set forth [10] that takes full advantage of low-complexity of the stochastic CMOS designs to improve area- and energy-efficiency. On the other hand, such implementation seeks extremely-long bit-stream that could lead to more energy consumption and longer latencies. Besides, it requires a significant amount of Linear Feedback Shift Registers (LFSRs) to generate the uncorrelated input and weight bit-streams. Both the FPGA and stochastic CMOS implementations leverage parallel Boolean circuits such as pseudo-random number generators, adder, and multipliers to improve the performance. Such designs impose significant area and energy overheads compared with leveraging the physical behaviors of emerging devices to perform the computation intrinsically.

Within the NVM domain, Bojnordi et al. [6] proposed to leverage resistive RAM (RRAM) devices to implement vectormatrix multiplication with up to 100× speedup and 10× energy savings over single-threaded cores. In the same way, Eryilmaz et al. [8] and Sheri et al. [7] have used resistive memories with CMOS activation function that ultimately imposes excessive area and power consumption overheads. Recently, spintronic devices with low energy barrier nanomagnets such as spin orbit torque-Magnetic Tunnel Junctions (SOT-MTJs) and embedded magnetoresistive random access memory (MRAM) devices are leveraged as a natural building block to provide probabilistic sigmoidal activation functions for RBMs, as studied in [11] and [12], respectively. These devices have realized significant energy and area improvements compared to previous RBM hardware implementations. Thus, we will investigate various circuit implementations to interpolate the stochastic output of the probabilistic spin logic devices (p-bit) proposed in [13]. In particular, inspired by a technique that is used to create an analog-to-digital

converter [14], we will develop two CMOS-based probabilistic interpolation recoder (PIR) circuits, which leverage a sampling methodology to provide a digital output corresponding to the probabilistic output of the p-bit based neurons. The proposed circuits achieve significant improvements in terms of resource utilization and energy consumption compared to conventional integration followed by analog-to-digital conversion methods.

### 1.2 NEED FOR IN-SITU ADAPTATION FOR PROCESS VARIATION IMMUNITY

Stochastic circuits play a significant role in the implementation of networks with probabilistic nodes. For instance, learning networks employing p-bits are worthwhile in realizing DBNs in a way that weights are trained offline by a learning algorithm in software and the hardware is utilized to repeatedly perform inference tasks effectively. Unstable low barrier nanomagnets present a direct mechanism to realize stochastic sigmoidal neurons in DBNs through leveraging the randomly fluctuating magnetization to produce a stochastic time varying output voltage. If these nanomagnets are designed to have as low energy barriers that are feasible, then many random outputs are produced in a short period of time. Under this strategy, a near-zero energy barrier nanomagnet has the capability of free magnetization layer flipping back and forth which can be tuned by modulated the voltage on the gate of p-bit's NMOS transistor.

The p-bit device is not entirely tolerant of defects and device-to-device variations even though is more error resilient than strictly digital computing devices [215]. The statistical distribution of the magnetization fluctuations, such as the power spectral density become affected by the presence of both localized and delocalized structural defects and moderate variations for the barrier height of the nanomagnet which is caused by small size variations [216]. It is investigated that the power spectral density is relatively insensitive to the presence of small localized defects

and moderate barrier height change. Nevertheless, the power spectral density is substantially affected by delocalized defects such as thickness variations over a significant fraction of the nanomagnet [217][218][219]. Delocalized defects can considerably change the fluctuation rate of the magnetization in low barrier nanomagnets. This will affect applications in p-bit-based neurons for neuromorphic architectures because the fluctuation rate is essential for stochastic computing applications. Thus, the defects caused by the fabrication imperfections are required to be addressed for neuromorphic applications using p-bit based neurons such as DBNs due to their significant impact on their performance and accuracy.

### 1.3 CONTRIBUTIONS OF THE DISSERTATION

# 1.3.1 AN EFFICIENT CONVERTER TO INTERPOLATE THE PROBABILISTIC OUTPUT OF THE NEURONS IN DBNS

The concept of using sampling and count operations to interpret the probabilistic output of a p-bit based neuron offers an intriguing approach to realize a CMOS-based probabilistic interpolation recoder (PIR) for a spin-based stochastic binary neuron. Herein, we proposed a PIR circuit as a replacement for an analog-based approach to interpolate the output of the p-bit based activation functions in the last layer of a DBN circuit. The conventional method involved: first, using an RC circuit to continuously integrate the analog output of the p-bit, next an op-amp based sample and holder is used to sample the output of the RC circuit, finally the analog sampled output is converted to a digital value through an op-AMP based ADC circuit and a priority encoder. Our proposed CMOS-based PIR circuit removes the need for all of area- and energy-consuming analog components existing in conventional circuits such as resistors, capacitors, and opamps, and performs the interpolation operation only by using MOS-transistor

based Boolean gates and flip-flops. In addition, the PIR circuits have an inherent single stuck-at fault tolerant features to tolerate either transient or permanent faults at the circuit's output without redundancy or active refurbishment overhead.

# 1.3.2 MITIGATING THE EFFECTS OF PROCESS VARIATION ON THE PERFORMANCE AND ACCURACY OF DBNS

We investigated two approaches to mitigate the effects of process variation on the energy barrier of the p-bit based neurons, and their consequent impact on the performance and accuracy of DBNs using p-bit devices as probabilistic sigmoidal neurons. In the first approach, it was shown that an increase in the energy barrier leads to decreased fluctuation speed in the magnetization direction of the p-bit' nanomagnet. It means that in order to observe the desired probabilistic sigmoidal behavior in the p-bit based neuron a temporal redundancy is required to be added to the sampling time of the p-bits output to give it enough time to have sufficient probabilistic fluctuations. While the temporal redundancy has shown to be an efficient mechanism, it was examined that it can lead to approximately 10-fold higher energy consumption in a 784×200×10 DBN which can tolerate maximum 2 kT of energy barrier variations compared to a variation-less DBN with similar topology. The second variation tolerance mechanism proposed herein involved implementing p-bit with a negative self-feedback, which could significantly increase the probabilistic fluctuation speed of the free layer. In this case, the drain of the NMOS transistor in the p-bit device tracks the magnetization direction of the free layer of the MTJ, and the inverter at the output of the device naturally generates the inverse voltage, hence realizing a negative feedback effect which successfully compensate the variation impacts with only ~10% energy consumption overheads.

# 1.3.3 HIGH ACCURACY DBN-FUZZY NEURAL NETWORKS USING MRAM-BASED STOCHASTIC NEURONS

In order to benefit from high-speed DBN hardware implementations, Probabilistic Inference Network-Simulator (PIN-Sim) has been developed and used to achieve up to 3× energy reduction and 20× area reduction in comparison with the prior DBN hardware implementations, however, this framework suffers from low accuracy in image classification. In order to improve the accuracy of MRAM-based DBN, we can increase the size of network but the accuracy will be improved only by 2.5% at the cost of  $\sim 10 \times$  higher energy consumption and significantly larger area overheads. We addressed this problem by utilizing a fast fuzzy algorithm in the interest of improving the accuracy of MRAM-based neural networks while we still can benefit from a high-speed hardware implementation. In this system, the MRAM-based DBN and the fuzzy system are working sequentially, which can be suboptimal in terms of energy as well as accuracy. In the first phase, the MRAM-based DBN is employed to identify the top recognition results with the highest probability. In the second phase, a fuzzy system is utilized to obtain the top-1 recognition results. Simulation results exhibit that a DBN-Fuzzy neural network not only has lower energy and area consumption than bigger DBN topologies but also has higher accuracy. Neuro-fuzzy systems based on spintronic devices may offer a compact and computationally-efficient architectural approach to machine-based image recognition tasks.

# **CHAPTER 2: MAGNETIC TUNNEL JUNCTIONS (MTJ)**

### CHARACTERISTICS AND OPERATION

The development of spintronics [15] was a direct result of the discovery of Giant Magnetoresistance (GMR) [16],[17], which in turn resulted in numerous significant advances. The demand for feasible alternatives to minimize power leakage rises with CMOS downscaling, and one of the most promising solutions is appeared to be spin-based devices [18].

In the spintronics development, Magnetic Tunnel Junction (MTJ) has an important role [19]. An insulator layer exists between ferromagnetic layers in the structure of an MTJ. In comparison to other technologies, MTJ has low power consumption, excellent scalability, and potentially infinite endurance. Moreover, MTJ devices can be entirely turned off without data loss resulting in saving energy which cause the MTJ appropriate for various applications [19] such as analog to digital converter and memory devices. MTJ-based non-volatile memories (NVMs) have shown excellent performance by considering its advantages such as endurance and energy efficiency [20]. At highly low energy levels, MTJ-based memories work with a ten-year retention time making them appropriate for low powered applications as internet of things (IoT) applications or batteries [21]. Other applications of MTJ devices are in storage and data processing [22],[25]. MTJs can be applied to mixed signals, such as analog to digital converters and comparators [24],[25] which can be useful in radio frequency. As an illustration, spectrum-optimizing applications based on compressive sensing [26] desire to lower power consumption and reduce the area of their circuits.

Figure 1 shows the fundamental structure of MTJ devices. As shown, an insulator layer MgO divides two ferromagnetic layers. In the free layer, the magnetization direction can be switched

Figure 1: Magnetic tunnel junction (MTJ).

but the magnetization direction in the reference layer is unchangeable. Thus, electrical properties of the MTJ device is identified by the magnetic field. The two ferromagnetic layers' magnetization orientations (m<sub>z</sub>) cause the two levels of the MTJ resistance to be in the high-resistance R<sub>AP</sub> at an anti-parallel state or low-resistance R<sub>P</sub> at a parallel state. The binary logic can be easily implemented by employing these two stable states of the MTJ [27]-[30]. Several methods for switching between the stable states of an MTJ have been presented. Below, three of the most prominent mechanisms for magnetization-switching are explained.

### 2.1 SPIN TRANSFER TORQUE (STT) SWITCHING

In order to enhance the density of the basic proposed MTJ circuits, spin transfer torque was presented in [31]. The bidirectional current I in STT device allows switch the MTJ state when I is bigger than a critical current  $I_{c0}$ . While STT enhances the scalability of the circuit, which provides a denser and simpler design, this method utilizes the same line to write and read the MTJ state which in turn leads to the issue of encountering an unexpected writing while a reading is occurring. Another drawback of the STT is that going from AP to P needs a smaller current than going from P to AP. Additionally, the application density is restricted in STT devices since a larger access transistor size is needed and increase in retention failures leads to unreliable operations [32]. The applications with high write speed have several problems since the

switching current of STT is proportional to the write pulse width in reverse [32]. The MTJ behavior model can be written as [33],[34]:

$$I_{CO} = \alpha \frac{\gamma^e}{\mu_R g} (\mu_0 M_s) H_k V \tag{1}$$

$$E = \frac{\mu_0 M_s H_k V}{2} \tag{2}$$

where the gyromagnetic ratio is  $\gamma$ , the magnetic damping constant  $\alpha$ , the elementary charge is e, the spin polarization efficiency factor is g, the Bohr magneton is  $\mu_B$ , the permeability of free space is  $\mu_0$ , the effective anisotropy field is  $H_k$ , the saturation magnetization is  $M_s$ , and the volume of the free layer is V. The average MTJ state switching delay time (t) can be attained as follows [33],[34]:

$$\tau = \tau_0 \exp\left(\frac{E}{K_B T} \left(1 - \frac{I}{I_{co}}\right)\right), when I < I_{co}$$

(3)

$$\frac{1}{\tau} = \left[\frac{2}{C + \ln\left(\frac{\pi^2 \epsilon}{4}\right)}\right] \frac{\mu_B P_{ref}}{e m_m (1 + P_{ref} P_{free})} (I - I_{c0}), when I > I_{c0}$$

$$\tag{4}$$

where the Boltzmann constant is  $K_B$ , the attempt period is  $\tau_0$ , the temperature is T, the thermal stability factor is  $\epsilon$ , Euler's constant is C, the tunneling spin polarizations are  $P_{ref}$  and  $P_{free}$ , and the magnetization moment is  $m_m$ .

### 2.2 VOLTAGE-CONTROLLED MAGNETIC ANISOTROPY (VCMA) SWITCHING

Magnetoelectric effects have been employed in the interest of lowering the required energy consumption for switching the MTJ state [35]. By utilizing a voltage-controlled MTJ with an electric field, less area and energy consumption is achievable [36],[37]. An electric field with the

VCMA effect is utilized with the purpose of switching the MTJ state, which is when the occupation of atomic orbitals at the interface is altered through an accumulation of electron charges induced by the electric field. A change of magnetic anisotropy is obtained with this and the spin-orbit interaction [35],[38],[39].

Figure 2 exhibits the operational characterization of VCMA-MTJ. The barrier thickness increase would result in lower parasitic conductance and the effect of current-induced torques when the switching is carried out through voltage [32]. VCMA can decrease the energy barrier between the AP and P states which makes the switch of states easier. The energy barrier ( $E_b$ ) between two stable magnetization states can be removed once the switching voltage  $V_b$  is more than MTJ critical voltage  $V_c$ . The minimum  $V_c$  for successful VCMA-MTJ switching is given by [40]:

Figure 2: Structure and stable states of VCMA-MTJ device.

$$V_c = \Delta(0)k_B T t_{ox} / \xi A \tag{5}$$

where the thermal stability under zero voltage is  $\Delta(0)$ ,  $k_B$  is the Boltzmann constant, the VCMA coefficient to weigh the perpendicular magnetic anisotropy (PMA) change under  $V_b$  is  $\xi$ , the temperature is T, the MTJ oxide layer thickness is  $t_{ox}$ , and the sectional area of the MTJ is A.

The VCMA-MTJ unstable states make its dynamics are changed consistently until  $V_c$  is obtained [41]. As soon as the excitation of MTJ terminals has finished, the energy barrier of the intermediate states returns to an amount more than the stable states resulting to stabilize the MTJ in its AP or P state. VCMA does not need large currents that lead to better scalability in its applications and less power consumption relating to STT. On the other hand, practical VCMA devices suffers from reliability issues which need to be examined more [42].

### 2.3 SPIN-ORBIT TORQUE (SOT) SWITCHING

A balanced switching current between the two MTJ states is allowed in the SOT devices by utilizing three terminals with the purpose of separating the read and write paths. In these devices, the read stability is increased since during the read operation, the possibility of a bit flip is decreased [32]. Spins are gathered once a current passes the non-magnetic layer and over the magnetization of the ferromagnetic layer, a torque switching is produced. Moreover, by utilizing SOT with the elimination of the time-demanding precessional motion, a faster switching can be happened [43]. On the other hand, SOT devices cannot be compatible with high-density applications since its three terminal structure causes a bigger cell size than STT-based applications.

#### 2.4 POST-CMOS ROLES OF SPIN-BASED DIGITAL CIRCUITS

This subsection discusses some digital applications of MTJ devices.

### 2.4.1 MTJ-BASED MRAM

MTJ-based memories are the most famous applications of MTJ. The best characteristics of static random-access memory (SRAM), dynamic random-access memory (DRAM), and flash memory can be found in Magnetic Random-Access Memory (MRAM) [44],[45]. MTJs are considered as the primary elements in information storage by employing the difference of the MTJ resistance in its antiparallel and parallel states to represent the "1" and "0" in the binary system and the intrinsic spin of electrons as a storage unit.

According to the needed MOS transistors' numbers and approach of write operation to build a memory cell, the MTJ-based MRAM's structures can be different [46],[49]. Figure 3 (a) shows the bit-cell structure of spin transfer torque MTJ-based MRAM (STT-MRAM). As shown, the STT-MTJ has higher density memories since each bit-cell has only one transistor with the STT-MTJ. The MTJ state switching during the write operation is performed by the bi-directional current  $I_{Write}$  and the comparison of read current  $I_{Read}$  with a reference current defines the MTJ state [30]. It should be noted that an asymmetric write operation characterizes STT-MRAM since the current needed to switch from the P to AP state is bigger than that of switching from the AP to P state [48]. As a result, the access transistor has to be large in the interest of obtaining the requirement of the write operations' worse case [47],[48],[50].

Relative to other techniques, STT-MRAM has intrinsic problems such as high write power and long latency [41]. However, magnetization flipping upon a voltage pulse is provided by MTJ with VCMA [36],[51]. A lower energy dissipation can be obtained by utilizing voltage instead of a charge current for MTJ write operations [41]. Furthermore, access transistor size reduction can be attained by the needed driving current reduction for the write operation [41]. By considering the switching energy and density of devices, VCMA-MTJ-based memory has better performance than STT-MRAM [35],[41],[52],[53].

Figure 3 (b) illustrates the structure of VCMA-MeRAM. This device has 1 access transistor and 1 MTJ in series like STT-MRAM. By switching the MTJ state or maintaining it, write operation can be performed. For this purpose, an extra circuit is required in order to check the state of MTJ and decide to maintain or switch the state of MTJ.

Herein, we discussed the structure of SOT-MRAM as its bit-cell design is shown in Figure 3 (c). As shown, the two access transistors in each bit-cell decreases the capacity of integration density [47],[49]. In this device, the read path and the write path are separated. The voltage applied

Figure 3: Memories devices: (a) STT-MRAM (b) VCMA-MeRAM (c) SOT-MRAM.

between the bit line (BL) and the source line (SL) generates the write current  $I_{Write}$  that is polarized and as a result, switches the MTJ free layer's magnetization direction. However, based on the magnitude of  $I_{Read}$ , the MTJ state is read during the read operation [54].

Recent researches claim that SOT-MRAM needs a lower write energy and a lower write time than STT-MRAM [55]-[58]. However, it is shown in [41] that VCMA-MeRAMs has better energy consumption, speed and area than STT-MRAM. Table 1 exhibits a comprehensive comparison between these devices provided in [59]. On the other hand, we need to consider that intensive development and research are being done on SOT and VCMA devices despite commercialized products are based in STT MTJ.

Recently, combination of read and write MTJ device's mechanisms have been employed for implementing memories. As an illustration, NAND-SPIN is an MTJ-based memory [47] which utilizes couple of the aforementioned switching mechanisms. As shown in Figure 4, the advantages of both SOT and STT mechanisms are taken in the interest of gaining better performance. The integration density of NAND-SPIN memory is better relative to SOT-MRAM since the transistors are shared by several MTJs. However, NAND-SPIN has better energy performance than STT-MRAM [47].

Table 1: Comparison between some MTJ-based memories.

|                                   | STT-MRAM | VCMA-MeRAM | SOT-MRAM |

|-----------------------------------|----------|------------|----------|

| Read Time (ns)                    | 1–5      | 1–5        | 1–5      |

| Write Time (ns)                   | 5–10     | <1         | <1       |

| Cell Size (area in $F^2$ )        | 40–50    | 20–30      | 50–70    |

| Bit Density (Gb/cm <sup>2</sup> ) | 1        | 2          | 0.75     |

| Read Energy/Bit (fJ)              | 10-20    | 1–5        | 10–20    |

| Write Energy/Bit (fJ)             | 100-200  | <5         | <10      |

Figure 4: The structure of 4-bit NAND-SPIN.

### 2.4.2 NON-VOLATILE LOGIC GATES

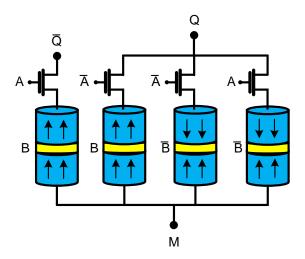

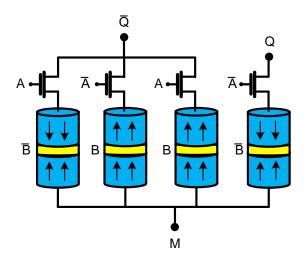

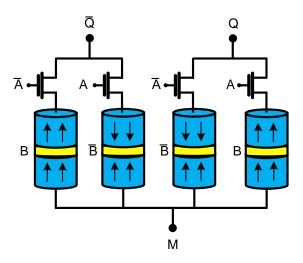

Other applications of MTJ devices are non-volatile logic gates which provide less power consumption and area. Figure 5 shows the structure of NV-AND / NV-NAND. The NAND and AND operations are represented by  $\overline{Q}$  and Q, respectively. Table 2 exhibits the truth table and Equations (6) and (7) illustrates the logic functions. For any MTJ's resistive level, this structure functions correctly.

$$Q = AB \tag{6}$$

$$\overline{Q} = \overline{AB} = \overline{A} + \overline{B} = \overline{AB} + \overline{AB} + A\overline{B} \tag{7}$$

Figure 5: The structure of NV-AND / NV-NAND.

Table 2: Truth table of AND/NAND.

| A | В | Q (AND) | $\overline{Q}$ (NAND) |

|---|---|---------|-----------------------|

| 0 | 0 | 0       | 1                     |

| 0 | 1 | 0       | 1                     |

| 1 | 0 | 0       | 1                     |

| 1 | 1 | 1       | 0                     |

Figure 6 illustrates the structure of NV-OR / NV-NOR. The NOR and OR operations are represented by  $\overline{Q}$  and Q, respectively. Table 3 exhibits the truth table and Equations (8) and (9) illustrates the logic functions.

$$Q = \bar{A}B + A\bar{B} + AB \tag{8}$$

$$\overline{Q} = \overline{A}\overline{B} \tag{9}$$

Table 3: Truth table of OR/NOR.

| A | В | Q (OR) | $\overline{Q}$ (NOR) |

|---|---|--------|----------------------|

| 0 | 0 | 0      | 1                    |

| 0 | 1 | 1      | 0                    |

| 1 | 0 | 1      | 0                    |

| 1 | 1 | 1      | 0                    |

Figure 6: the structure of NV-OR / NV-NOR.

Figure 7 illustrates the structure of NV-XOR / NV-XNOR. The XNOR and XOR operations are represented by  $\bar{Q}$  and Q, respectively. Table 4 exhibits the truth table and Equations (10) and (11) illustrates the logic functions.

$$Q = \bar{A}B + A\bar{B} \tag{10}$$

$$\bar{Q} = \bar{A}\bar{B} + AB \tag{11}$$

Table 4: Truth table of XOR/XNOR.

| A | В | Q (XOR) | $\overline{Q}$ (XNOR) |

|---|---|---------|-----------------------|

| 0 | 0 | 0       | 1                     |

| 0 | 1 | 1       | 0                     |

| 1 | 0 | 1       | 0                     |

| 1 | 1 | 0       | 1                     |

Figure 7: The structure of NV-XOR / NV-XNOR.

In [60], Deng presents some structures for logic gates that decrease the number of MTJ and NMOS transistors relative to the presented logic gate structures. On the other hand, some MTJ and NMOS settings such as their resistance configurations must be followed to be operated properly.

### 2.4.3 NON-VOLATILE CLOCKLESS LOOK-UP TABLE (C-LUT)

Look-Up Tables (LUTs) are one of the major FPGAs' components which are usually implemented by SRAM cells [61]. However, SRAM-based LUTs have several limitations such as high static power, volatility, and low logic density [62]. On the contrary, MTJ-based LUTs have lower mutual disturbance and power consumption since all parts are powered off except the data processing portion which is active.

Table 5 exhibits a comprehensive comparison of some MTJ-based LUTs provided in [63]. In [62], Salehi et al. employs spin Hall effect (SHE)-based MTJ for implementing a 6-input fracturable non-volatile Clockless LUT (C-LUT) for combinational logic operations without

Table 5: Characteristics of LUT designs.

| Design        | Write/Read Operation | Features and Challenges    |  |

|---------------|----------------------|----------------------------|--|

|               |                      | High Speed                 |  |

| FIMS-LUT [68] | Magnetic Field/TMR   | High Power Consumption     |  |

|               |                      | High Area Overhead         |  |

|               |                      | Relatively High Speed      |  |

| TAS-LUT [64]  | Magnetic Field/TMR   | High Power Consumption     |  |

|               | _                    | Medium Area Overhead       |  |

|               |                      | High Speed                 |  |

| STT-LUT [63]  | STT/TMR              | Low Power Consumption      |  |

| -             |                      | Low Area Overhead          |  |

|               |                      | High Speed                 |  |

| A-LUT [63]    | STT/TMR              | Scalable Power Consumption |  |

|               |                      | Low Area Overhead          |  |

requiring a clock while the proposed spin-based LUTs in [63]-[67] need a clock. This C-LUT reduces the area in comparison with the STT-MTJ-based C-LUT by removing the sense amplifier.

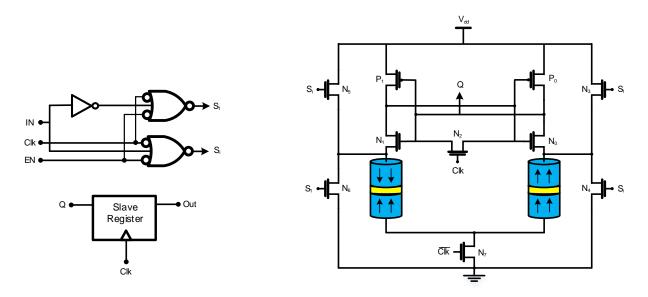

### 2.4.4 SPIN-MTJ BASED NON-VOLATILE FLIP-FLOP

Flip-flop based on non-volatile memory prevents the data loss due to system crashes and power failures. In [69], Zhao et al. proposes one of the first MTJ-based non-volatile flip-flop for System On Chip (SoC) and FPGA circuits. These circuits are fully non-volatile since all the processed data is stored in the cells of Spin-MTJ memory permanently. Figure 8 shows the full schematic of this circuit.

Figure 8: Spin-MTJ based Non-Volatile Flip-Flop [69].

The transistors N3, N4, N5, N6 are controlled by the NOR gates that two of them are active each time. While the circuit is in static mode, the power dissipation is reduced since the signal EN enables the current source. The pair of MTJs is written by the signal IN and then, the current direction is given. N7 switches between the reading and writing mode. The slave register keeps the prior data and the input data is stored when Clk = 1. However, the sense amplifier reads the stored data and the slave register updates with Q when Clk = 0. Several implementations of non-volatile flip-flop are available in [34],[70]-[72].

## 2.4.4 SPIN-MTJ BASED NON-VOLATILE FULL ADDER

Figure 9 shows the structure of a single-bit full adder including two outputs (S and  $C_o$ ) and three inputs (A, B and  $C_i$ ) given by Equations (12) and (13). In a CPU, high-density and low-power FA are desirable since FA is a fundamental unit to an arithmetic operation.

Figure 9: The schematic of Single-bit full adder (FA).

$$S = A \oplus B \oplus C_i = ABC_i + A\overline{B}\overline{C}_i + \overline{A}B\overline{C}_i + \overline{A}\overline{B}C_i$$

(12)

$$C_o = AB + AC_i + BC_i (13)$$

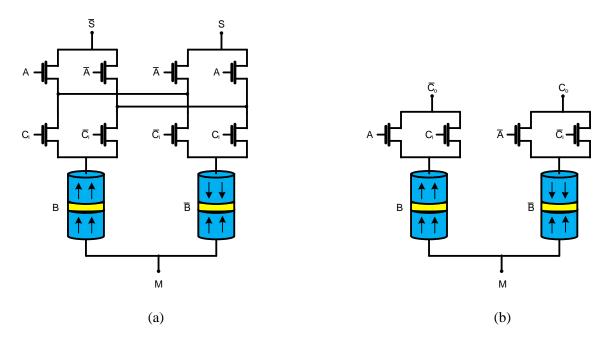

The MTJ-based SUM and CARRY sub-circuits are shown in Figure 10 [60]. In [23],[73]-[75], many more non-volatile full adders were presented.

Figure 10: The structure of full adder: (a) SUM sub-circuit (b) CARRY sub-circuit.

# 2.5 FABRICATION OF MAGNETIC TUNNEL JUNCTIONS

Researchers utilize several materials such as Mg<sub>3</sub>B<sub>2</sub>O<sub>6</sub> [89], ZnO [88], NaCl [87], and Al<sub>2</sub>O<sub>3</sub> [86] as barrier layer material but the most frequently used material is MgO [85]. Other barrier layer material such as titanates [90],[91] and ferrites [92] have been utilized too. Several groups investigate barriers with graphene as insulating layer [93],[94]. The most popular ferromagnetic layers are CoFeB, Co, and Fe [95]. In the past few years, several studies broadly have been done in MTJ with rare earth metals [98] and heusler alloys [96],[97]. Additionally, ferromagnetic electrodes in these devices' fabrication is being implemented by MTJ with magnetic oxides [99] [100][101].

Lower resistance ( $R_P$ ) will be achieved in the barrier's tunneled electrons once spins have the same orientation in lower and upper ferromagnets. The opposite spin-orientation in two ferromagnets results in higher electrical resistance ( $R_{AP}$ ). Therefore, such combination of an insulator and ferromagnets demonstrate spin-orientation dependent electrical behavior, which is not allowed in regular magnetic materials or conducting [102][103].

Magneto-resistance (MR) effect defines as a change in the device's electric resistance with an applied magnetic field's effect once spin-orientation of such a combination of insulator and ferromagnets is controlled by applying magnetic field [84][86]. This effect is recognized as TMR effect since these devices' MR effect is relevant to tunneling phenomena [84]. As a result, these devices demonstrate tunneling magnetoresistance (TMR) that relies on the barrier layer's thickness and the ferromagnetic layer's spin polarization [104]. Several successful effect of such combinations have been experimentally demonstrated in various groups[84][98]. Moreover, this

effect's technological development can be observed by many memory devices' successful implementation [76][83].

These devices are on the basis of the spin dependent tunneling principle. Huge value of TMR is achieved from insulating barrier's spin dependent tunneling. Theoretically, a TMR value of ~1000% was achieved [106][107] but experimentally, a value of 604% could be attained so far [108]. These devices' deposition is a difficult task in spite of interesting phenomena in these devices. In this subsection, we will explain these devices' fabrication, but before, we will focus on the junction area's importance.

#### 2.5.1 JUNCTION SIZE

In future storage technology, the possibility to form micrometer-scale junctions is one essential condition for the MTJ's application as read head sensors or MRAM elements. Working for longer duration and obtaining low dimensions is another challenge for these devices' fabrication. It is shown that for data retention over 10 years, a high enough thermal stability can be achieved for magnetic cells with size of nanometer [93][98][108][109]. By utilizing lithography process, MTJs are fabricated down to the nanometer levels' dimensions [110][111].

For a specified set of barrier parameters, a memory application should have a definite value for the junction area's resistance. Therefore, the product of barrier's resistance and junction area, resistance area (RA) product, is defined to understand the MTJ's characteristics[112][113]. On the basis of the operational requirements on access time and noise, an upper limit of around 20  $k\Omega$   $\mu$ m<sup>2</sup> to the RA product of MRAM cells is set [114][116]. Thus, researchers assess TMR of these devices along with RA product [117][121]. It is reported RA = 1  $k\Omega$   $\mu$ m<sup>2</sup> and TMR = 12% in RF plasma oxidized Al barrier [117], RS = 2  $k\Omega$   $\mu$ m<sup>2</sup> and TMR = 12% in natural in situ

oxidation [118], and RS = 960  $\Omega$   $\mu m^2$  and TMR = 6% in multiple oxidation of successive layers of Al in O<sub>2</sub> [119]. In order to minimize the junction area, lithography can be considered as an alternate solution by considering these several issues. Therefore, the MTJ's fabrication is a two-step process: (1) growth of multilayer structures by utilizing appropriate deposition technique, and (2) grown multilayers are fabricated into devices. We have explained these steps in the next subsections [101].

### 2.5.2 GROWTH OF MULTILAYER STRUCTURE

One of the major steps in the MTJ's fabrication is growth of a multilayer structure. For deposition of multilayer structure, we need dedicated deposition chamber with ultra-high vacuum  $(10^{-10}-10^{-11} \text{ Torr})$  [96][100].

## 2.5.3 MOLECULAR BEAM EPITAXY (MBE)

The most popular tool for the MTJ's deposition is MBE. This tool is efficient in maintaining different layers' orientation and stoichiometry. For this reason, researchers mostly utilize this technique to grow MTJ. In this technique, CaTiO<sub>3</sub> as insulating layer and trilayer heterostructure La<sub>1-x</sub>Sr<sub>x</sub>MnO<sub>3</sub> as the ferromagnet was utilized. This structure demonstrates magnetoresistance  $\Delta$ R/R(H) $\Delta$ R/R(H) of as much as 450% in 200 *Oe* applied field at 14 *K* which persists up to ~250 K [122]. In [123], RA product of the order of 10<sup>6</sup>  $\Omega$ – $\mu$ m<sup>2</sup> and TMR value ~120% are reported by depositing Fe/MgO/Fe structure with MBE method. In [124], RA product of few  $k\Omega$ – $\mu$ m<sup>2</sup> and MR ratio of 88% (T = 293 *K*) are reported for the structure of fully epitaxial Fe/MgO/Fe MTJ with this technique. For Fe(001)/MgO(001)/Fe(001) junctions, RA product of 25  $k\Omega$ – $\mu$ m<sup>2</sup> and TMR value 180% are reported by this group [105].

Likewise, several research groups utilize this technique to fabricate Fe/MgO/Fe MTJ with considerable values of TMR [125][128]. For MgO(100)/Fe/MgO/Fe/Co/Pd MTJ with thickness of 0.8 nm for insulating layer, these junctions show a very small interlayer magnetic coupling, TMR up to 17%, and a low resistance around  $4 \, k\Omega - \mu m^2$  [129]. Several other groups also employ this technique for MTJ structure growth such as Co/MgO/Co tunnel junctions [133], MgO–EuO composite tunnel barriers [132], heusler based MTJ [131], and Fe/MgO/Gd [130].

### 2.5.3.1 E-BEAM EVAPORATION

E-beam evaporation method can be utilized for growing Fe/MgO/Fe structures [84][134][135]. This set-up permits online monitoring of thickness by utilizing quartz crystal monitor and substrate heating up to 500 °C [136]. In [134][135], the details of these structures' growth procedure are reported. These structures do not show the formation of perfect interfaces but instead of that show the presence of Fe-oxides at interfaces [137]. Interface oxidation can be resulted from vacuum level of the order of 10<sup>-8</sup> Torr by utilizing this technique and growing MgO/Fe/MgO structures [140] and Fe/MgO/Fe/Co MTJ structures [138][139]. We should avoid this condition for the good quality MTJ's fabrication.

# 2.5.3.2 SPUTTERING DEPOSITION

Another choice for growing these structures is a combination of RF and DC sputtering since a typical MTJ multilayer structure consists of insulating and ferromagnetic layers. For the deposition of CoFeB/MgO/CoFeB structure, a Six-Gun RF sputtering set-up is utilized in [141][142].

This technique recently is efficiently utilized for the multilayer structure's deposition of this CoFeB based MTJ. Sputtering method is utilized for growing MgO tunnel barriers with CoFe

electrodes which demonstrate TMR values of up to about 300% at low temperatures and almost 220% at room temperature [143]. In [101] is shown that these structures demonstrate crystallinity from well distinguishable lattice for each layer.

Several researchers used this technique to develop MTJ with varying compositions of ferromagnetic CoFeB electrodes while these MTJs demonstrate highest value of TMR [144][148]. A value of TMR around 604% at room temperature employing this technique is reported in [108] which is the TMR maximum value has been reported so far. Moreover, this group has achieved a low switching current of  $49 \,\mu A$  in Ta/CoFeB/MgO/CoFeB/Ta, high thermal stability at dimension as low as  $40 \, nm$  diameter, and TMR value of the order of 120% by employing this technique. Therefore, these parameters try to use these MTJs in spintronic devices [149].

### 2.5.3.3 ION BEAM SPUTTERING DEPOSITION

To deposit these structures, Ion beam sputtering has been utilized by several research groups [150][155]. TMR values up to 110%, with RA products of 100–400  $\Omega$   $\mu$ m<sup>2</sup> for CoFeB/MgO/CoFeB MTJ have been reported by these authors. NiFe/Mg/MgO/CoFe MTJ is grown by utilizing this technique by Singh and Chaudhary [152][154]. These authors report a TMR value of 1% for ion beam sputtered MTJ [153].

To deposit multilayer structure, several famous methods has been discussed in this subsection which further fabricate these devices in well-defined junctions by using lithography process. For growing oxide heterostructures in context of MTJ, several other deposition techniques such as atomic layer deposition [158][161] and pulsed laser deposition [156][157] are also employed by researchers.

#### 2.5.4 LITHOGRAPHY

For the semiconductor devices' fabrication, one of the famous phenomena in electronic industry is Lithography [162][163]. E-beam lithography is employs even though in semiconductor industry, optical lithography meets the device size requirement [164]. In [165][166], e-beam lithography is preferred through advanced etching procedure and in [164][166], e-beam lithography is preferred to design devices free from mechanical damage and chemical impurity. Two lithography types are defined based on the fabricated device's size: (1) Nanolithography features smaller than 100 nm and (2) Microlithography for growing features smaller than 10  $\mu m$ . MTJs with junction size scaling down to few nm are under fabrication through the development of device requirements and technological advances. Therefore, the MTJ's fabrication is considered as a subcategory of nanolithography.

## 2.5.4.1 PHOTOLITHOGRAPHY

One of the approaches that often used for microchips' semiconductor manufacturing is Photolithography. For fabricating micro-electro-mechanical-systems (MEMS) devices, photolithography is usually utilized too. Several steps are required to fabricate device from layer grown on substrate (wafer) in typical lithography process. These steps can be outlined as follows [101]:

- I. As explained in Radio Corporation of America [167], surface layer cleaning.

- II. Heating the wafer surface to drive off any moisture that may be exist.

- III. Application of photoresist by spin coating.

- IV. Exposure of photoresist by pattern of intense light.

- V. Etching.

## VI. Photoresist removal.

Therefore, the two most critical steps in lithography process are: (1) exposure and (2) etching. The photoresist removal from layer is Etching. Chemical etching is a cost-effective and simple technique of etching by utilizing chemicals [168][169]. Several different techniques are used for etching procedure these days. These techniques are ion beam milling [172], reactive ion etching [171], and plasma etching [170]. While wet etching is considered as chemical etching procedure, these approaches are usually considered as dry etching.

Other principal step is exposure while the lithography's category is defined by the radiation's nature utilized for exposure. Photolithography is a process that ultra-violet radiation is employed for exposure. This technique is used for both MTJ fabrication and semiconductor devices' fabrication. Photolithography has been used in several researches in micron-sized Fe/MgO/Fe [174], Co<sub>75</sub>Fe<sub>25</sub>/Al<sub>2</sub>O<sub>3</sub>/Co<sub>75</sub>Fe<sub>25</sub> [173], and Ni–Fe/Al<sub>2</sub>O<sub>3</sub>/Co [172] junction. Chen et al. employed this technique to grow micron-sized junction on flexible substrate [175][176]. The MTJ fabrication is a regular process while the layers' number for pattering is more than three and each layer requires pattering. Patterning of Co, Al<sub>2</sub>O<sub>3</sub>, and NiFe layers is needed for NiFe/Al<sub>2</sub>O<sub>3</sub>/Co fabrication. The MTJ device patterning is a difficult job and requires a lot of expertise since each layer's patterning goes through several steps.

### 2.5.4.2 E-BEAM LITHOGRAPHY

Electron beam lithography has the ability of much greater patterning resolution. In the manufacture of photomasks, electron beam lithography is essential too. Electron beam lithography is kind of maskless lithography which a mask is not needed to produce the ultimate pattern. Instead, through controlling an electron beam while scans across a resist-coated

substrate, the ultimate pattern is made directly from a digital representation on a computer. The drawback of electron beam lithography is that it is much slower than photolithography. As a result, e-beam lithography is used in most of the MTJ uses [140][155]. This process is used to fabricate Ni<sub>80</sub>Fe<sub>20</sub>/Co<sub>75</sub>Fe<sub>25</sub>/Al-O/Co<sub>75</sub>Fe<sub>25</sub>/Ta MTJ. A part of the MTJ structure is removed by utilizing Ar ion milling and e-beam lithography in this procedure. Then, Pt layer of thickness 10 nm was vacuum-evaporated obliquely on both sides of Al<sub>2</sub>O<sub>3</sub>/Cu films, substrate was covered with a thick Al<sub>2</sub>O<sub>3</sub>/Cu film and liftoff in organic solvent. At the end, Ar ion milling defines junction area, in which the Pt films were utilized as etching masks with 100  $\mu m \times 10 nm$ .

## 2.5.5 PATTERNING OF FE/MGO/FE SYSTEM

Recently, ion milling is preferred over chemical etching in case of etching in spite of significant results in chemical etching. We first discuss the Fe/MgO/Fe/Au MTJ procedure utilizing e-beam lithography and chemical etching in the interest of understanding the MTJ fabrication phenomena. The detailed information of this lithography procedure is given by Fe/MgO/Fe MTJ. As depicted below, the process containing almost 21 steps which are demonstrated in terms of different steps for better understanding [101]:

- 1. Multilayer structure growth.

- 2. Deposition of photoresist (PR) on the structure.

- 3. PR Masking.

- 4. Radiation exposure on PR.

- 5. Desired structures are grown in PR.

- 6. Au layer etching.

- 7. Fe layer etching using appropriate etching agent.

- 8. MgO barrier layer etching.

- 9. Photoresist removal.

- 10. PR Deposition.

- 11. Utilization of another mask to define exposure to radiation and lower layer.

- 12. After exposure structures are formed through PR.

- 13. Lower electrode etching.

- 14. PR removal.

- 15. Silica deposition for insulation among several devices.

- 16. PR deposition.

- 17. Mask to exposure through radiation and grow contact pads.

- 18. Structure formation for lower contact pads.

- 19. Formation of structure and silica etching for contact pads.

- 20. Contact layer deposition and PR removal.

- 21. PR deposition and exposure through mask to deposit contact pads of around 1 mm.

#### 2.5.6 FABRICATION OF DEVICE USING PSEUDO/METAL MASKING PROCEDURE

To fabricate these devices, we need to pass through a complicated lithography process. These devices' properties can be affected through a number of such treatments. Thus, researcher employs the technologies that are free from complicated lithography process. Pseudo-masking is a technology that is utilized by researchers at the beginning of this technology as these junctions' fabrication. In [177][178], this methodology is employed to develop the procedure for growing CoFe/Al<sub>2</sub>O<sub>3</sub>/Co and CoFe/Al<sub>2</sub>O<sub>3</sub>/NiFe junctions. At room temperature, these junctions could achieve approximately 11% of TMR.

To minimizing magnetic coupling, the Jullieres's observation of TMR in Fe/Ge/Co junction has been employed in this procedure through oxidizing Ge in dry oxygen [179]. To deposit Gd/Gd<sub>2</sub>O<sub>3</sub>/NiFe junctions, metal masking is used by this group [180]. As a replacement for metal mask that allows in situ deposition of MTJ, Ootuka et al. reported fabrication method on the basis of Si<sub>3</sub>N<sub>4</sub> membrane [181]. As reported by Julliers [179] and Moodera group [177][178], this process also prevents the situation where vacuum breaking is needed for designing junctions. Although mask formation requires e-beam lithography, the pseudo-masking fabrication methods to grow MTJ without lithography process. In [67], pseudo masking is employed by Perkin et al. employed in the interest of fabricating these devices, which results in approximately 220% TMR value at room temperature. Thereafter, Barraud et al. used this technique for the purpose of growing Co/Al<sub>2</sub>O<sub>3</sub>/Co junction on organic substrate and Si [182] and on Kapton substrate by another group[183].

As described, MTJ fabrication is a multistep and complicated procedure. The most significant steps are choice of radiation, etching, and masking. In the lithography process a substantial improvement has been achieved through the technological advancement that makes good quality junction with smaller junction size and perfect shape. Researchers utilize various lithography techniques such as free electron lithography [186], X-ray lithography [185], and ion beam lithography [184]. Because of typical instrumentation associated with these techniques, the utilization of these techniques is restricted [187][188].

# **CHAPTER 3: BACKGROUND**

# 3.1 DEEP BELIEF NETWORK (DBN)

DBN can be easily realized by stacking Restricted Boltzmann machines (RBMs), which are classes of recurrent stochastic neural networks, in which state of the network, k, has an energy expressed by (1), determined by the connection weights between nodes and the node bias, where  $s_i^k$  denotes the state of node i in k,  $b_i$  represents the bias, or intrinsic excitability of node i, and  $w_{ij}$  is the weight of connection between nodes i and j [189].

$$E(k) = -\sum_{i} s_{i}^{k} b_{i} - \sum_{i < k} s_{i}^{k} s_{i}^{k} w_{ij}$$

(14)

The probability of each node in a RBM to be in state one is determined based on (2), where  $\sigma$  denotes the sigmoid function. RBMs can reach a Boltzmann distribution in which the system probability to be in state v is represented by (3), and u could be any possible system state. Therefore, given sufficient time, the system moves towards the states with the lowest associated energy.

$$P(s_i = 1) = \sigma \left( b_i + \sum_i w_{ii} s_i \right) \tag{15}$$

$$P(v) = \frac{e^{-E(v)}}{\sum_{u} e^{-E(u)}} \tag{16}$$

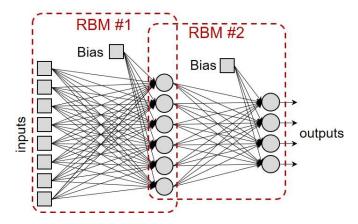

Figure 11: An example of DBN structure including a visible layer

RBM consists of two fully-connected layers called the *visible layer* and the *hidden layer*, as shown in Figure 11. Crossbar architecture is a widely-explored method to implement such networks. The most known method for training RBMs is contrastive divergence (CD), which is based on approximate gradient descent procedure using Gibbs sampling [190]. CD operates in four steps as described below:

- I. Feed-Forward I: The hidden layer, h, is sampled based on the applied training input vector, v, to the visible layer.

- II. Feed-back: The generated input (v') is sampled based on the sampled hidden layer output which is fed-back to the network.

- III. Feed-Forward II: The reconstructed hidden layer, h', is sampled by applying v' to the visible layer.

- IV. Update: The weights are updated according to Equation (17), where W is the weight matrix and  $\eta$  is the learning rate.

$$\Delta W = \eta(\mathbf{v}h^T - \mathbf{v}\hat{h}^T) \tag{17}$$

# Algorithm 1: Contrastive Divergence Unsupervised Learning Algorithm

```

Input: train dataset (D<sub>train</sub>), # of training samples (S), # of RBMs (M)

Output: weight (n).mat, bias(n).mat, where n is the RBM number

Require: Maximum iteration (MaxIter), Learning Rate (\eta)

for i = 1:S do

\mathbf{v} = \mathbf{D}_{\text{train}}(\mathbf{i});

for j = 1:M do

for k= 1:MaxIter do

Feed-Forward 1: h = \sigma (b + \sum w. v);

Feed-Back: v' = \sigma (c + \sum w. h);

Feed-Forward 2: h' = \sigma (b + \sum w. v');

Update:

\Delta W(j) = \eta (vh^T - v'h'^T) \Rightarrow W(j) = W(j) + \Delta W(j)

\Delta B(i) = \eta (h - h') \Rightarrow B(i) = B(i) + \Delta B(i)

\Delta C(j) = \eta (v - v') \Rightarrow C(j) = C(j) + \Delta C(j)

end

end

end

for j = 1:M do

weight(j).mat \LeftarrowW(j);

bias(j).mat \Leftarrow B(j);

end

```

A DBN can be formed by stacking RBMs and trained similarly to RBMs. The visible layer and the first of the hidden layers within the network are trained first with CD. Then, the CD is repeated as much as needed, which will adjust the weights in a hierarchical flow as described in Algorithm 1.

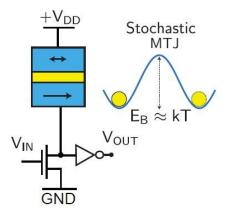

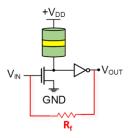

# 3.2 EMBEDDED MRAM-BASED NEURON

In this subsection, we show how a recently-proposed building block based on embedded MRAM technology can realize a neuron with probabilistic sigmoidal activation function [13]. The MRAM-based stochastic device (p-bit) structure is shown in Figure 12. It consists of a magnetic tunnel junction (MTJ), which is a 2-terminal device with two possible resistive levels based on the orientation of its ferromagnetic (FM) layers, i.e. *fixed layer* and *free layer*. The fixed layer has a fixed magnetic orientation, while the free layer's magnetization orientation can be

Figure 12: The diagram of the embedded MRAM-based neuron

switched. In conventional MRAM cells, free layer of the MTJ is manufactured with a thermally-stable nanomagnet with a large energy barrier with respect to the thermal energy (kT). Accordingly, the fixed layer works as a non-volatile storage. Recently, in search of functional spintronic paradigms, thermally-unstable MTJs based on superparamagnetic materials have been theoretically and experimentally explored [191], [192], [193], [194], [11], [195], [196], [197], [198].

In this work, we use a thermally-unstable MRAM device with a low energy-barrier nanomagnet  $(E_B \ll 40 \text{ kT})$  [13]. The MTJ resistance of this device randomly fluctuates between the two possible resistive states. This leads to a fluctuating output voltage at the drain of the NMOS transistor connected to a CMOS inverter. The inverter amplify such voltage deviation from the threshold voltage and generate a stochastic output modulated by the input voltage. Particularly, by reducing the drain-source resistance  $(r_{ds})$  through increasing the input voltage  $(V_{IN})$ , the voltage at the drain of the NMOS transistor is shorted to the ground. Alternatively, it can get to  $V_{DD}$  by increasing the  $r_{ds}$  through decreasing  $V_{IN}$ . Such device operation is formulated considering the MTJ conductance [13]:

Figure 13: Output probability of MRAM-based neuron vs. its input voltage.

$$G_{MTJ} = G_0 \left[ 1 + m_z \frac{TMR}{(2+TMR)} \right] \tag{18}$$

where  $m_z$  is the free layer magnetization,  $G_0$  denotes the average MTJ conductance,  $(G_P+G_{AP})/2$ , and TMR represents the tunneling magnetoresistance ratio. The drain voltage can be written as:

$$V_{DRAIN}/V_{DD} = \frac{(2+TMR) + TMR \, m_z}{(2+TMR)(1+\alpha) + TMR \, m_z}$$

(19)

where  $\alpha$  is the ratio of the transistor conductance ( $G_T$ ) to the average MTJ conductance ( $G_0$ ).