# Reactive Rejuvenation of CMOS Logic Paths using Self-Activating Voltage Domains

Rízwan A. Ashraf, Ahmad Al-Zahraní, Navíd Khoshaví, Ramtín Zand, Soheíl Salehí, Arman Roohí, Míngjíe Lín, and Ronald F. DeMara,

Department of Electrical Engineering and Computer Science University of Central Florida

Web: http://cal.ucf.edu

# Reactive Rejuvenation of Voltage Domains for Anti-aging

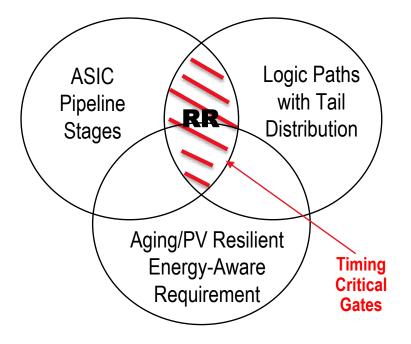

#### **Reactive Rejuvenation (RR)**:

a <u>post-fabrication</u> self-adapting circuit-level approach to mitigate timing degradations.

#### **Research Objective:**

Mitigate *Transistor Aging* due to BTI and HCI thus reducing the energy wastage due to conservative selection of guardbands.

### **Targeting Aging-critical Elements:**

- aging-critical logic portions of the circuit are targeted for protection → minimal overhead

- power-gating is effective in reducing BTI and HCI.

Switching activity (p) effects the shift in V<sub>th</sub>

$\Delta V_{th}(t) \propto (pt)^n$

COMPUTER

ARCHITECTURE

| Need addressed        | Approach                                                           | Benefit                                                                            |  |  |

|-----------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|

| Transistor Aging      | Power-gating of critical elements                                  | Reduced lifetime delay<br>degradation<br>through stress reduction                  |  |  |

|                       | In-situ timing assessment and autonomous control of Sleep Interval | Avoids the need for<br>complicated modeling of aging<br>degradation at design-time |  |  |

| Energy<br>Consumption | Reduced voltage guardbands                                         | Low energy requirement with<br>narrower margins for longer<br>periods              |  |  |

|                       | De-emphasized role of voltage regulators                           | Circumvent conversion<br>inefficiencies and switching<br>losses                    |  |  |

|                       | Selective Redundancy                                               | Power-gating lowers the leakage energy overheads                                   |  |  |

# **Related Works**

|              | 0.001 832036                                    | 2003 80 - 3000 T                                                                                                     | 1079 (1993)                                | Anna ana                         | Overheads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1474-174                             |

|--------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|              | Anti-Aging<br>Strategy                          | Design Re-<br>quirements/<br>Parameters                                                                              | Adaptability<br>Characteristics/<br>Degree | Throughput                       | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Area                                 |

| SO PLINES    | Second and                                      | and the second                                                                                                       | Worst-case Design                          | Concernance -                    | Second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |

| VM, FM       | Static Margin                                   | $\frac{\text{MD-RoD}}{\Delta V_{DD}},$<br>$\Delta F_{nominal}$                                                       | None                                       | FM: High                         | VM: High (Dy-<br>namic & Leak-<br>age)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | None                                 |

| Gate-Sizing  | Static Margin                                   | MD-RoD; Ex-<br>tended Std. Lib.;<br>Multi-obj. Opt/<br>$\Delta\beta_i$ , $\forall$ gates $i$                         | None                                       | None                             | Medium (Dy-<br>namic & Leak-<br>age)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Low (Gate-level)                     |

| Re-Synthesis | Static Margin                                   | MD-RoD anno-<br>tated Std. Lib.;<br>Aging-aware<br>Synthesis/ $\Delta\beta_i$ ,<br>$\Delta V_{th,i} \forall$ gates i | None                                       | None                             | Low-Medium<br>(Dynamic &<br>Leakage)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Low (Gate-level)                     |

|              |                                                 |                                                                                                                      | mic Operating Cond                         | itions                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

| DVFS         | Dynamic Margin                                  | Timing Sensors;<br>Feedback Con-<br>trol $\Delta V_{DD}(t)$ ,<br>$\Delta F(t)$ ,<br>$\Delta V_{bb}(t)$               | Yes/ Fully Au-<br>tonomous                 | Low                              | Medium (Dy-<br>namic & Leak-<br>age)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Medium (On-<br>chip VR &<br>sensors) |

| SVS          | Dynamic Margin                                  | $\frac{\text{MD-RoD}}{\Delta V_{DD}(t} + \Delta t_{step})$                                                           | Yes' tstep                                 | None                             | Medium (Dy-<br>namic & Leak-<br>age)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Medium (On-<br>chip VR)              |

| GNOMO        | Static Margin +<br>Power-Gating                 | $\frac{\text{MD-RoD}}{(V_{DD,g}, t_{idle})}$                                                                         | None                                       | Medium (Work-<br>load Dependent) | Medium (Dy-<br>namic & Leak-<br>age)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | None                                 |

|              |                                                 |                                                                                                                      | ive Resource Manae                         | ement                            | NUMBER OF STREET, STRE |                                      |

| SD           | Proactive Mngt.<br>+ Power-Gating               | Modular Redun-<br>dancy/ Sleep In-<br>terval                                                                         | Yes / Sleep Inter-<br>val                  | None                             | High (Leakage)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | High (Module-<br>level)              |

| ITL schemes  | Proactive Mngt.<br>+ Power-Gating               | Exploit App.<br>Redundancy/<br>Idle time                                                                             | Yes / Task<br>Scheduling                   | Medium (Work-<br>load Dependent) | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | None                                 |

| RR           | Reactive Fine-<br>Grain Mngt. +<br>Power-Gating | Timing Sen-<br>sors; Feedback<br>Control; CPRT/<br>ERT%                                                              | Yes/ Fully Au-<br>tonomous                 | None                             | Minimal (Leak-<br>age)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Low (Gate-level<br>& sensors)        |

Proposed herein

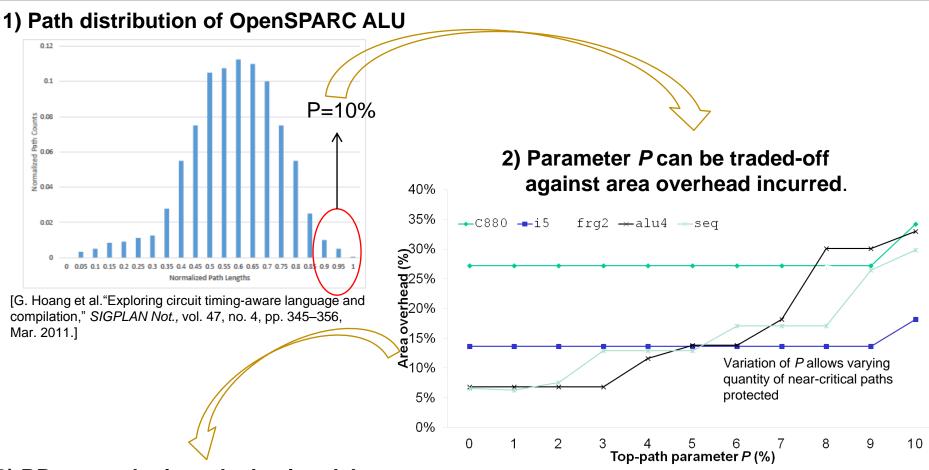

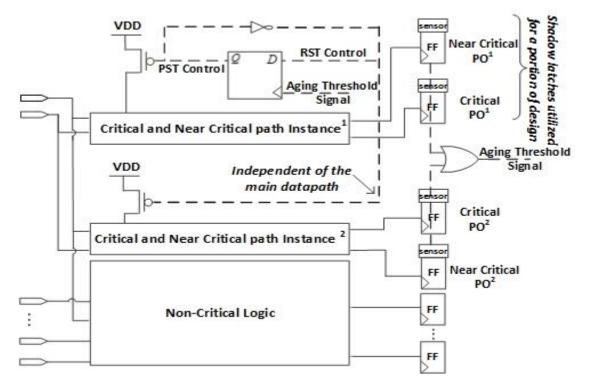

3) RR covers logic paths having delays:

$$[D_{critical}(t) * (100\% - P), D_{critical}(t)]$$

- P is top-path parameter

- based on near critical paths due to aging and/or PV effects

- P=10% used herein

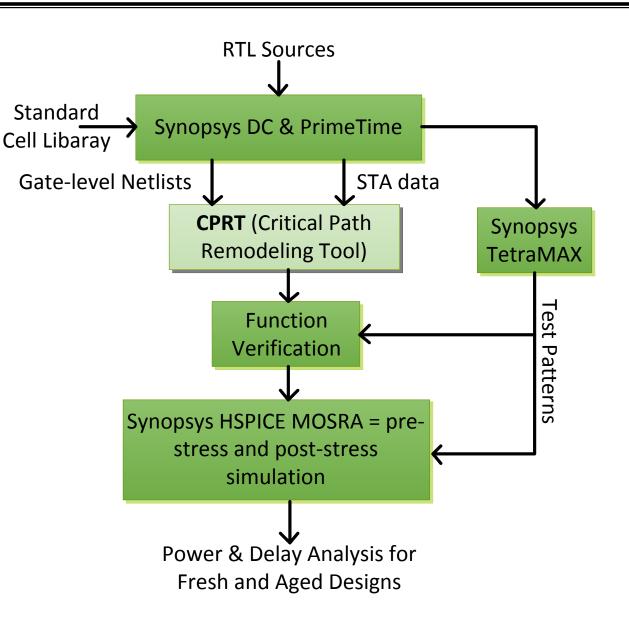

## Critical Path Remodeling Tool (CPRT)

COMPUTER

ARCHITECTURE

COMPUTER ARCHITECTURE LABORATORY

#### Need for circuit-level feedback:

Determination of *sleep interval* at design-time is based on assumptions and may mismatch actual circuit aging.

#### **Reactive Rejuvenation (RR):**

Fully autonomous reliable operation with optimal switching interval and minimal design effort.

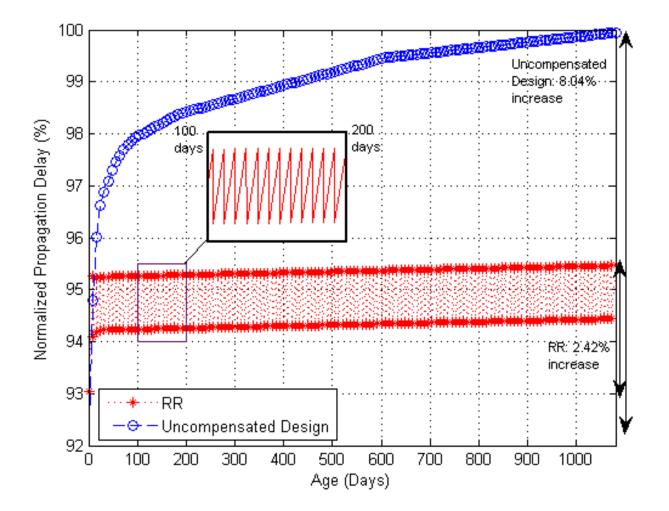

## **RR Reduction of Delay Degradation** c880

- NanGate Library based on 45nm Predictive Technology Model is used

- Built-in models for BTI and HCI are utilized for HSPICE simulations

#### **Elastic Recovery Threshold:**

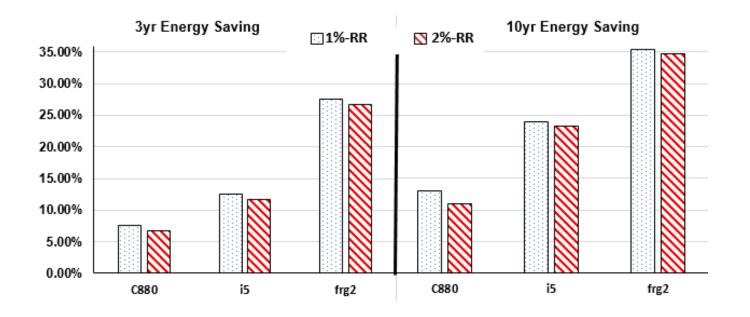

at design-time, supply voltage is set such that delay of circuit is ERT% below desired timing specification. ERT=1% and 2% used.

#### **Reduced guardbands:**

enables energy savings as high as 35.3% and 34.6% for frg2 with ERT of 1% and 2% respectively over 10 years.

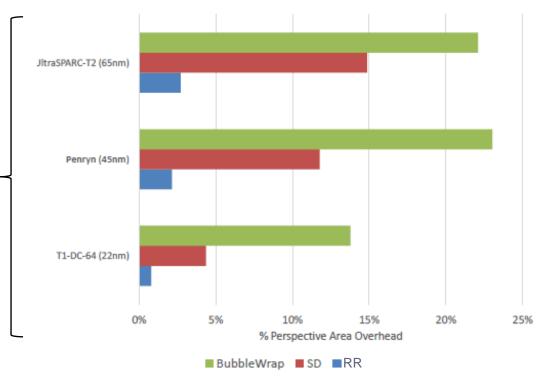

# Area Overhead w.r.t. Related Works

#### **Case-study:**

- 45nm-based Intel Penryn multicore processor.

- Core-area of 46.1%, Uncore-area composed of caches, NoC, etc.

#### **Execution unit:**

- 39%, of which 65.5% is occupied by arithmetic units

- $\rightarrow$  aging-critical portion = 11% of die

- For BubbleWrap: half of the cores are designated as expandable

- For SD: aging-sensitive logic is replicated

- Utilized ALU area overhead with N=2, P=7%

#### **Summary of Approach**

- RR provides an adaptive technique for anti-aging using a spatial redundancy and power-gating to enable BTI recovery

- Accurate aging modeling → unnecessary as circuit degradation is determined using operational conditions

- Intrinsic runtime competition among logic domains in the presence of process, voltage and temperature variations

- Favorable energy savings as high as 35.3% using RR are obtained due to reduction of operating voltage through autonomous adaptation of switching interval