# MFPA: MIXED-SIGNAL FIELD PROGRAMMABLE ARRAY FOR ENERGY-AWARE COMPRESSIVE SIGNAL PROCESSING

by

ADRIAN TATULIAN B.S. University of Central Florida, 2013

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Spring Term 2020

Major Professor: Ronald F. DeMara

© 2020 Adrian Tatulian

#### ABSTRACT

Compressive Sensing (CS) is a signal processing technique which reduces the number of samples taken per frame to decrease energy, storage, and data transmission overheads, as well as reducing time taken for data acquisition in time-critical applications. The tradeoff in such an approach is increased complexity of signal reconstruction. While several algorithms have been developed for CS signal reconstruction, hardware implementation of these algorithms is still an area of active research. Prior work has sought to utilize parallelism available in reconstruction algorithms to minimize hardware overheads; however, such approaches are limited by the underlying limitations in CMOS technology. Herein, the MFPA (Mixed-signal Field Programmable Array) approach is presented as a hybrid spin-CMOS reconfigurable fabric specifically designed for implementation of CS data sampling and signal reconstruction. The resulting fabric consists of 1) slice-organized analog blocks providing amplifiers, transistors, capacitors, and Magnetic Tunnel Junctions (MTJs) which are configurable to achieving square/square root operations required for calculating vector norms, 2) digital functional blocks which feature 6-input clockless lookup tables for computation of matrix inverse, and 3) an MRAMbased nonvolatile crossbar array for carrying out low-energy matrix-vector multiplication operations. The various functional blocks are connected via a global interconnect and spin-based analog-to-digital converters. Simulation results demonstrate significant energy and area benefits compared to equivalent CMOS digital implementations for each of the functional blocks used: this includes an 80% reduction in energy and 97% reduction in transistor count for the nonvolatile crossbar array, 80% standby power reduction and 25% reduced area footprint for the clockless

lookup tables, and roughly 97% reduction in transistor count for a multiplier built using components from the analog blocks. Moreover, the proposed fabric yields 77% energy reduction compared to CMOS when used to implement CS reconstruction, in addition to latency improvements.

#### ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor, Dr. DeMara, for welcoming me into the Computer Architecture Laboratory and since then always being there to support me whether that meant proofreading a paper, recommending courses, or simply encouraging me that I'm on the right track. As a result, I was able to complete this thesis and serve as co-author on two IEEE publications within two years of coming into the program as an out-of-field student with very limited ECE knowledge. In addition, I would like to thank Dr. Nazanin Rahnavard and Dr. Damian Dechev for agreeing to serve on my thesis committee.

Finally, this work was supported in part by the Center for Probabilistic Spin Logic for Low-Energy Boolean and Non-Boolean Computing (CAPSL), one of the Nanoelectronic Computing Research (nCORE) Centers as task 2759.006, a Semiconductor Research Corporation (SRC) program sponsored by the NSF through CCF-1739635, and by NSF through ECCS-1810256.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                      |

|------------------------------------------------------|

| LIST OF TABLES                                       |

| CHAPTER ONE: INTRODUCTION 1                          |

| Need for Mixed-Signal Reconfigurable Arrays1         |

| Compressive Sensing                                  |

| Spin-Based Computation and Architectural Approaches5 |

| Contributions and Organziation of Thesis9            |

| CHAPTER TWO: RELATED WORK 12                         |

| Mixed-Signal Arrays12                                |

| NVM-Based FPGAs14                                    |

| Hardware for Implementation of CS Sampling17         |

| Hardware for Implementation of CS Reconstruction     |

| Summary                                              |

| CHAPTER THREE: MFPA PLATFORM                         |

| NVM Crossbar                                         |

| Configurable Digital Blocks (CDBs)                   |

| Configurable Analog Blocks (CABs)                    |

| CHAPTER FOUR: ENERGY AND DELAY PERFORMANCE  |

|---------------------------------------------|

| NVM Crossbar                                |

| CDB                                         |

| CAB                                         |

| CHAPTER FIVE: ASSESSMENT OF ERROR TOLERANCE |

| OMP                                         |

| CoSaMP 44                                   |

| AMP                                         |

| CHAPTER SIX: FABRIC-BASED CS REALIZATION 49 |

| Sampling Architecture                       |

| Reconstruction Architecture 50              |

| Further Benefits                            |

| CHAPTER SEVEN: CONCLUSIONS                  |

| Technical Summary and Insights              |

| Scope and Limitations                       |

| Future Work                                 |

| APPENDIX: COPYRIGHT PERMISSIONS             |

| REFERENCES                                  |

## **LIST OF FIGURES**

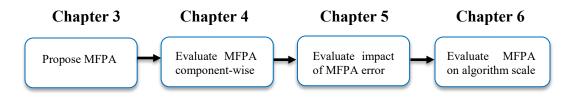

| Fig. 1: Outline of thesis. Preliminary versions of some of this work appeared as a first author |

|-------------------------------------------------------------------------------------------------|

| publication in the 2019 International Conference on Reconfigurable Computing and FPGAs          |

| [35]                                                                                            |

| Fig. 2: Summary of selected previous approaches to beyond-CMOS NVM integration in               |

| reconfigurable fabrics                                                                          |

| Fig. 3: Summary of challenges and solutions relating to hardware implementation of              |

| Compressive Sensing. Each of the listed challenges is addressed by MFPA, as discussed in        |

| Chapter 1                                                                                       |

| Fig. 4: (a) Single-slice organization for proposed MFPA architecture, b) MFPA routing and       |

| switch interconnect design, and (c) Hybrid spin/charge device realization as configurable       |

| blocks within the MFPA fabric                                                                   |

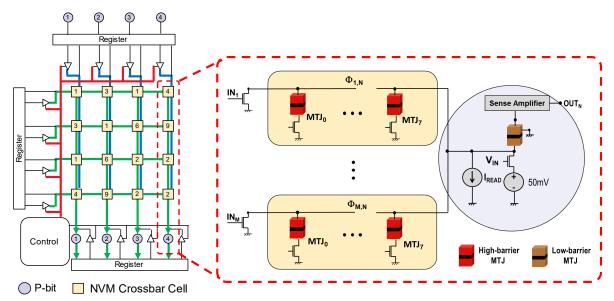

| Fig. 5: MFPA NVM Crossbar consisting of 1 MTJ per cell for In-Memory Computing, where           |

| red signals show the configuration flow, the blue signals depict the path for populating the    |

| measurement matrix and green signals illustrate the path for VMM operation                      |

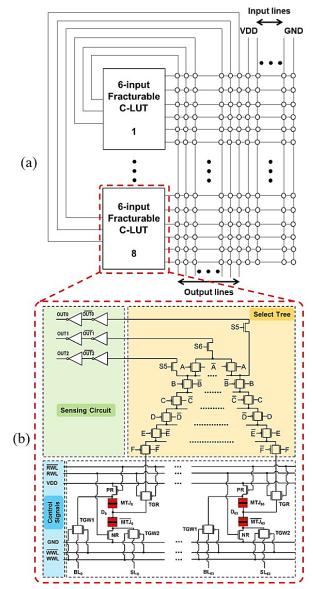

| Fig. 6: (a) MFPA CDB structure and (b) C-LUT circuit components utilized for CDB logic          |

| select/retrieval [3]                                                                            |

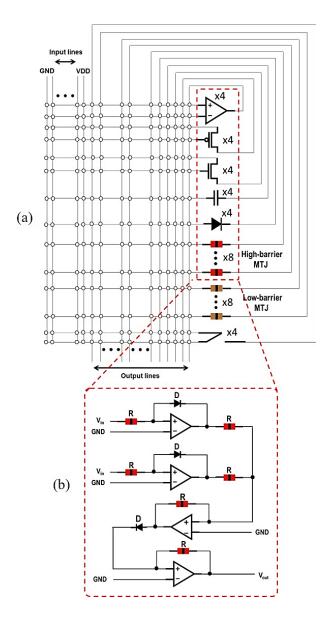

| Fig. 7: (a) MFPA CAB structure and (b) configuration of an analog multiplier circuit using      |

| CAB elements                                                                                    |

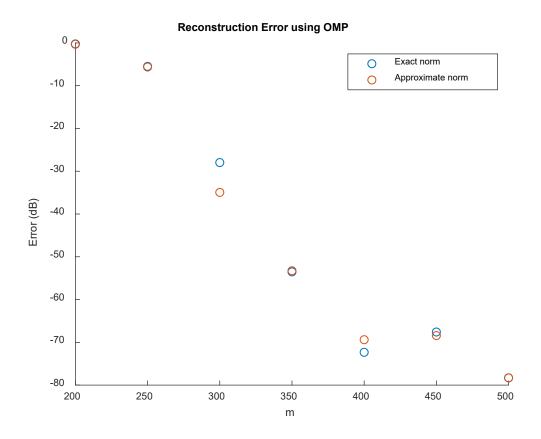

| Fig. 8: Reconstruction error using OMP                | 43 |

|-------------------------------------------------------|----|

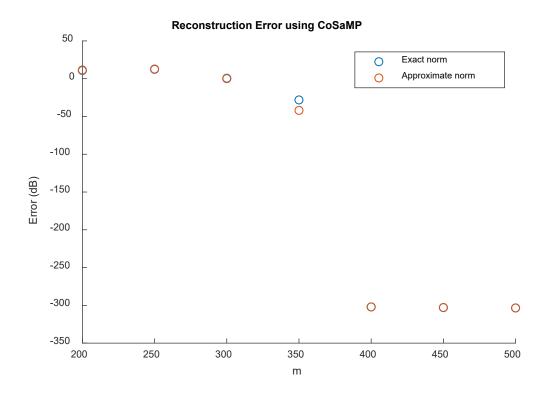

| Fig. 9: Reconstruction error using CoSaMP             | 45 |

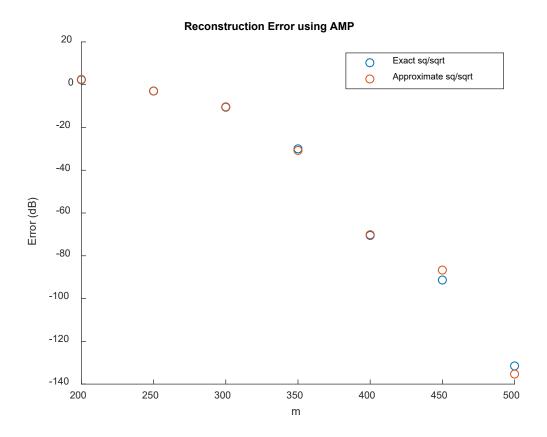

| Fig. 10: Reconstruction error using AMP               | 47 |

| Fig. 11: Hardware architecture for AMP reconstruction | 52 |

| Fig. 12: Logical organization of this thesis          | 57 |

### LIST OF TABLES

| Table 1: Comparison of mixed-signal field-programmable fabrics which are suitable for |    |

|---------------------------------------------------------------------------------------|----|

| various signal processing tasks                                                       | 14 |

| Table 2: Comparison of energy needed for VMM in CMOS crossbar vs. proposed NVM        |    |

| crossbar.                                                                             | 36 |

| Table 3: Data for analog squaring circuit.                                            | 38 |

| Table 4: Data for analog square root circuit.                                         | 39 |

| Table 5: Data for analog inverse square root circuit.                                 | 39 |

| Table 6: Minimum number of measurements needed for -60 dB error, using exact and      |    |

| approximate square-square root operations.                                            | 48 |

| Table 7: MFPA energy costs.                                                           | 53 |

| Table 8: Energy for AMP.                                                              | 54 |

#### CHAPTER ONE: INTRODUCTION<sup>1</sup>

#### Need for Mixed-Signal Reconfigurable Arrays

The flexibility offered by reconfigurable fabrics has proven to be useful in signal processing applications. For instance, Huang *et al.* described an FPGA-based scalable architecture for computation of Discrete Cosine Transform (DCT) in image-video coding applications [1]. FPGAs allow for dynamic partial reconfiguration for zonal coding, i.e., performing DCT on zones varying in size from 1×1 to 8×8, as well as reconfigurability in the precision of DCT coefficients. It was shown that having this flexibility allows for optimizations which result in significant savings in both power and area consumption.

While digital-only FPGAs can be convenient for online algorithms requiring dynamic reconfiguration [2] and conducting general-purpose computation directly in hardware to avoid software overheads [3, 4], computations in the signal processing domain can generally be more efficiently solved in the analog domain due to the analog nature of real-world signals [5]. Thus, Field Programmable Analog Arrays (FPAAs) have gained attention as analog counterparts to FPGAs. It has been shown that analog computation for certain applications can offer orders of magnitude improvement in computational energy efficiency at the cost of reduced accuracy [6]. Therefore, judicious use of analog and mixed-signal computation may lead to benefits in various applications suitable for approximate computation. Mixed-signal arrays have already been used

<sup>&</sup>lt;sup>1</sup>© 2020 IEEE. Part of this chapter is reprinted, with permission, from [35].

for applications such as low-power temperature sensors and heart-rate alarms for IoT applications [7].

Unfortunately, analog systems present many challenges not present in their digital counterparts such as limited accuracy, low tolerance to noise and parasitics, and limited programmability. As such, analog design automation has been a field of active research, and algorithms have been developed for analog synthesis, layout and verification. It has been found that using a set of Configurable Analog Blocks (CABs), each with fixed layout, allows for a bounded synthesis problem and leads to an Electronic Design Automation (EDA) flow similar to that used in digital design [8].

#### Compressive Sensing

Compressive Sensing (CS) is an emerging signal processing technique that is well-suited for analog computation. The objective in CS is to reconstruct a sparse signal, i.e., a signal with only a small number of non-zero values in some basis, using sub-Nyquist sampling rates. This achieves reduced energy, storage, and data transmission overheads [9, 10], in addition to reducing sampling duration in time-sensitive applications such as MRI [11]. CS consists of a sampling phase, followed by a reconstruction phase.

During the sampling phase, measurements on the signal of interest are taken at a specified rate and quantization resolution. The objective of the sampling phase is to determine a compressed measurement vector,  $\mathbf{y} \in \mathbb{R}^M$ , based on the signal vector,  $\mathbf{x} \in \mathbb{R}^N$ , where  $M \ll N$ . A measurement matrix  $\mathbf{\Phi} \in \mathbb{R}^{M \times N}$  is used to achieve this using the transformation  $\mathbf{y} = \mathbf{\Phi} \mathbf{x}$ . Different methods exist

for generating the CS measurement matrix: one is by populating the entire matrix using values from a Gaussian distribution. Another is by restricting matrix elements to either '1' or '0', and simply populating each column of the matrix with a set number of '1's placed at random locations. The randomness of the measurement matrix ensures that the signal is uniformly sampled, i.e., no one part of the signal is given special consideration. In certain situations, signals may contain a specific *region of interest*: in this case, it is desirable to sample the region of interest at a higher rate, and thus a higher column weight (i.e., higher density of '1's) is used for columns corresponding to the signal's region of interest [12].

The reconstruction phase of Compressive Sensing entails solving  $\mathbf{y} = \mathbf{\Phi} \mathbf{x}$  to reconstruct the signal vector,  $\mathbf{x}$ . Since the matrix  $\mathbf{\Phi}$  contains more columns than rows, this amounts to solving an undetermined system of linear equations with more unknowns than equations, and hence an infinite number of solutions. In CS, the solution with lowest sparsity rate, i.e., lowest density of nonzero elements, is selected. This amounts to solving the minimization problem:  $\hat{\mathbf{x}} =$ argmin $\|\mathbf{x}\|_0$  s.t.  $\mathbf{y} = \mathbf{\Phi} \mathbf{x}$ . Unfortunately, this problem has been shown to be NP-hard and is therefore not practical to solve [9]. Thus, it is more common to approach signal reconstruction using the basis pursuit problem [10]:  $\hat{\mathbf{x}} = \arg\min||\mathbf{x}||_1$  s.t.  $\mathbf{y} = \mathbf{\Phi} \mathbf{x}$ , otherwise known as  $\ell_1$ minimization. By shifting focus from the  $\ell_0$  norm to the  $\ell_1$  norm, the problem becomes convex and therefore computationally more tractable to solve. The condition for being able to do this is known as the *Restricted Isometry Property (RIP)*, i.e., that for any *k*-sparse vector  $\mathbf{x}$ ,

$\|\boldsymbol{x}\|_p(1-\delta) \le \|\boldsymbol{\Phi}\boldsymbol{x}\|_p \le \|\boldsymbol{x}\|_p(1+\delta)$  for some specified *p*.

In addition to basis pursuit, a wide variety of algorithms with different tradeoffs are available for CS reconstruction [13]. One such algorithm which has been heavily targeted by hardware designers is Orthogonal Matching Pursuit (OMP). OMP is a greedy algorithm which seeks to use a set of k column vectors from the  $\boldsymbol{\Phi}$  matrix as a basis to represent  $\boldsymbol{y}$ . The challenge is to select the right column vectors, and then use this information to reconstruct the original signal vector,  $\boldsymbol{x}$ . The algorithm works by repeatedly picking columns of  $\boldsymbol{\Phi}$  with maximum correlation to the remaining part of  $\boldsymbol{y}$ . At each iteration, the algorithm solves a least-squares problem to pick an optimal solution for  $\boldsymbol{x}$ , based on the columns of  $\boldsymbol{\Phi}$  which have been picked so far. Based on  $\boldsymbol{\Phi}$  and  $\boldsymbol{x}$ , the algorithm then calculates  $\boldsymbol{y}$  and subtracts this from actual  $\boldsymbol{y}$  to determine the new residual vector before going to the next iteration. For a k-sparse signal, the objective is to attain an exact representation of the original signal after k iterations [14, 15]. In reality, the reconstruction will not be exact due to unavoidable measurement noise in the sampling process. The precise steps of OMP are outlined in Algorithm 1.

#### Spin-Based Computation and Architectural Approaches

A common issue with FPGAs is errors caused by faults such as process variation and cosmic ray interference. Hence, fault tolerance in FPGAs has been a widely-researched area [16-19] and has included methods such as evolutionary computation [20, 21], asynchronous logic [22, 23], and modular redundancies [24, 25]. Each of these solutions presents significant overheads in terms of power and area. This, in addition to challenges relating to CMOS scaling and power consumption, has motivated researchers to explore emerging devices as an alternative or complement to CMOS-based logic. Indeed, emerging devices such as quantum cellular automata (QCA) [26], domain

| Algorithm 1 Orthogonal Matching F | Pursuit |

|-----------------------------------|---------|

|-----------------------------------|---------|

**Inputs:** The measurement matrix,  $\Phi$ The measurement vector,  $\mathbf{y}$ The signal sparsity, k

**Output:** The signal vector,  $\mathbf{x}$

**Procedure:**

1) Initialize the residual  $\mathbf{r}_0 = \mathbf{y}$ , the index set  $\Lambda_0 = \emptyset$ , the column set  $\Phi'_0 = \mathbf{0}$ , and the counter i = 1.

while i < k do</li>

2) Find the index λ<sub>i</sub> most correlated with the measurement matrix, Φ by solving the optimization problem: λ<sub>i</sub> = arg max |⟨**r**<sub>i-1</sub>,φ<sub>j</sub>⟩|. j=1,...,N

3) Add λ<sub>i</sub> to the index set: Λ<sub>i</sub> = Λ<sub>i-1</sub> ∪ {λ<sub>i</sub>}.

4) Augment the column set Φ'<sub>i</sub> by φ<sub>λ<sub>i</sub></sub>: Φ'<sub>i</sub> = [Φ'<sub>i-1</sub>, φ<sub>λ<sub>i</sub></sub>].

5) Solve a least squares problem to determine the updated solution for the signal, **x**<sub>i</sub>: **x**<sub>i</sub> = arg min||**y**-Φ<sub>i</sub>**x**||.

6) Update the residual: **r**<sub>i</sub> = **y**-Φ<sub>i</sub>**x**<sub>i</sub>.

7) Increment the counter, *i*. wall nanomagnets [27], and spin-based devices [28, 29] have demonstrated superior performance in designs such as full adder and sense amplifier circuits. While several beyond-CMOS alternatives currently exist, the focus in this work will be on spin-based devices due to their commercial availability and benefits listed below.

Spin-based devices, specifically Spin Transfer Torque-based Magnetic Tunnel Junctions (STT-MTJs), are a form of post-CMOS technology which serve as the basis for Magnetic Random Access Memory (MRAM) in addition to having logic capabilities. MTJ's offer numerous benefits such as nonvolatility, near-zero static power consumption, area efficiency, fast read operation, and ability to be vertically integrated with CMOS for area efficiency [30]. STT-MTJs consist of two ferromagnetic layers, referred to as the fixed and free layers and separated by a thin oxide barrier. A bi-directional current passing through the device can change the polarization of the free layer magnetization and thus flip the device between the parallel (P) state and the anti-parallel (AP) state. The P-state device resistance is given by  $R_P = R_{MTJ}$  while the AP-state resistance is given by  $R_{AP} = R_{MTJ}(1 + TMR)$ , where:

$$R_{MTJ} = \frac{t_{ox}}{Factor \times Area\sqrt{\varphi}} exp(1.025t_{ox}\sqrt{\varphi})$$

(1)

$$TMR = \frac{TMR_0}{1 + \left(\frac{V_b}{V_h}\right)^2} \tag{2}$$

with *TMR* being tunneling magnetoresistance,  $t_{ox}$  the oxide layer thickness, *Factor* a materialdependent parameter which depends on the resistance-area product of the device, *Area* the surface area of the device,  $\varphi$  the oxide layer energy barrier height,  $V_b$  bias voltage, and  $V_h$  the bias voltage at which *TMR* drops to half of its initial value. In order for an MTJ to switch states, an energy barrier must be overcome. This switching process can occur in several ways; however, the two most practical methods are Spin Transfer Torque (STT) and Spin Hall Effect (SHE) switching. In STT switching, a spin-polarized current passing through the device transfers angular momentum to electrons in the device's free layer, which causes the magnetic moments of these electrons, and hence the free layer magnetization direction, to switch. In SHE switching, a charge current passing through a heavy metal base layer can induce spin-polarized current to pass through the device, causing switching as before. While STT devices are two-terminal with only one read/write path, SHE devices are three-terminal with separate read and write paths. Hence, the probability for write disturbance in these devices is lower, in addition to lower write latencies [10].

MTJs are also capable of switching stochastically due to thermal noise, if the energy barrier is set to a sufficiently low value ( $\ll 40 \ kT$ , where k is Boltzmann's constant and T is absolute temperature). The stochastic switching property has valuable applications when random or nondeterministic outputs are necessary [10]. While spin-based devices have been researched in academia for several years, they are now also gaining commercial ground, with Intel announcing the availability of 1T1MTJ MRAM cells in conjunction with their 22-nm FinFET technology [31].

MTJs contribute valuable properties such as non-volatility and stochasticity, allowing them to be suitable for diverse applications. One application is the fracturable 6-input spin-based look-up table, proposed in [32] and upgraded to utilize the Spin Hall Effect [33] and operate asynchronously as a Clockless-LUT (C-LUT) design [3]. The C-LUT's select tree consists of *D* levels of transmission gates, each controlling access to a spin-based memory cell. The memory cells consist of pairs of complementary MTJs for a wide read margin yielding reliable read operation. Furthermore, sensing is accomplished through a voltage divider circuit and a pair of inverters to amplify the signal, which eliminates the need for an external clock or large sense amplifiers. Such a design can be used for combinational logic to implement either one *D*-input Boolean function, or two (*D*-1)-input Boolean functions in parallel. This design yields an 80% reduction on standby power consumption compared to an SRAM-based LUT, which addresses a key challenge faced by CMOS designs.

In addition, the stochastic switching properties of low-energy-barrier MTJs can be used to implement a True Random Number Generator (TRNG) to generate an adaptive CS measurement matrix [10, 34]. This design is based on a *p-bit*, which divides the supply voltage  $V_{DD}$  between an MTJ and NMOS transistor. The MTJ is fabricated to have a low energy barrier (~1 *kT*) between P and AP states, and hence switches due to thermal activation. The p-bit utilizes the voltage in between the two devices, which switches stochastically due to the stochastic switching of the MTJ device. The p-bit output serves as the input to a D flip-flop, which then generates a random *M*-bit stream, where each bit determines one row of the measurement matrix, for random sampling of the input signal. The TRNG used in this design was found to reduce energy consumption per bit by 9-fold on average, compared to state-of-the-art TRNGs, in addition to an average area reduction of 3-fold [10].

To support mixed-signal operation and conversion, an Adaptive Intermittent Quantizer (AIQ) is a suitable spintronic circuit. It utilizes the Voltage-Controlled Magnetic Anisotropy (VCMA) effect to dynamically control MTJ energy barriers to implement an Analog-to-Digital Converter

(ADC) featuring dynamic Sampling Rate/Quantization Resolution (SR/QR) tradeoff [30]. In this design, the MTJs are arranged in a resistive-switch-ladder architecture, with the analog signal as input. Dynamically controlling the states of the switches and control over the number of active devices in the circuit allows the architecture to function at various QRs; in addition, use of an asynchronous clock allows the SR to be dynamically set as well. The SR/QR tradeoff is determined by the Signal-to-Noise (SNR) ratio of the input signal, e.g., high SNR favors high QR when sampling. As expected, this technique allows ADC at fixed bit and energy budgets, and results in considerable energy savings overall. Thus, spin-based architectures offer key benefits in power and area consumption when compared to CMOS and are promising candidates for next-generation reconfigurable fabrics.

#### Contributions and Organization of Thesis

In this work, a hybrid spin-CMOS Mixed-signal Field Programmable Array (MFPA) is proposed for Compressive Sensing applications. The proposed MFPA architecture consists of Configurable Analog Blocks (CABs), Configurable Digital Blocks (CDBs) and an MRAM-based Nonvolatile Crossbar Array (NVM Xbar) joined by a CMOS-based global interconnect. While CS can provide benefits such as reduced data storage and transmission costs, applications such as Internet of Things (IoT) devices also require minimal power consumption. Mixed-signal computing and spin-based devices are viable approaches for achieving this due to many advantages offered by this approach, including: a) **intrinsic computation for reduced hardware complexity:** time- and power-consuming operations such as square root are performed in one cycle using a simple circuit, with no digital-to-analog conversion needed due to input signals already being analog,

b) **stochasticity for true random number generation:** spin-based devices offer a low-energy method of achieving random number generation necessary for CS algorithms,

c) **power and area efficiency:** spin-based devices do not have leakage power constraints like CMOS and furthermore can be integrated vertically with CMOS for reduced area overhead, and d) **efficient VMM:** spin-based devices can be readily integrated into crossbar arrays for single-cycle Vector-Matrix Multiplication (VMM) operations. Thus, the hypothesis is that the proposed design will be capable of performing CS sampling and reconstruction while delivering significant energy and area benefits compared to the conventional digital CMOS implementation.

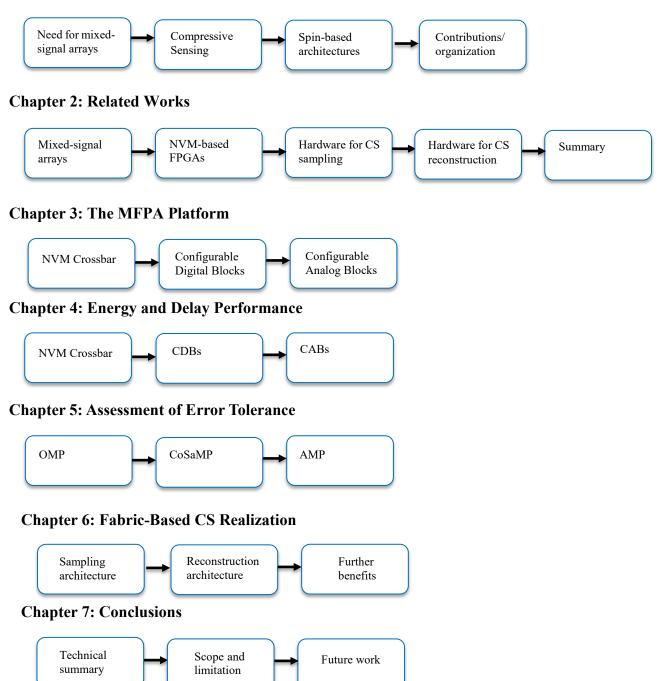

The thesis is organized as illustrated by Fig. 1: Chapter 2 reviews related works in the fields of reconfigurable arrays and hardware-based CS sampling and reconstruction. Chapter 3 outlines the specifics of the hardware proposed herein, beginning with an overview of the architecture and proceeding to discuss details of the NVM Xbar, CAB and CDB. Each component is then simulated and compared with an equivalent digital CMOS design in Chapter 4. Chapter 5 proceeds to assess the impact of computation errors associated with CAB analog outputs on CS reconstruction algorithms. Next, Chapter 6 presents an architecture for implementation of CS reconstruction using the proposed fabric, and evaluates the design compared to the digital CMOS equivalent. Finally, Chapter 7 concludes the thesis by giving a technical summary, and outlining insights gained and future work in the field.

#### **Chapter 1: Introduction**

Fig. 1: Outline of thesis. Preliminary versions of some of this work appeared as a first author publication in the 2019 International Conference on Reconfigurable Computing and FPGAs [35].

# CHAPTER TWO: RELATED WORKS<sup>2</sup>

#### Mixed-signal Arrays

Schlottmann and Hasler [36] noted that two main hurdles have hindered the widespread adaptation of analog computation: the lack of a programmable interface, and the lack of robust design tools. The Reconfigurable Analog Signal Processor (RASP) proposed by them was a groundbreaking development in FPAAs in that it provided an avenue for programmability of analog devices, and was further augmented through an integrated set of high-level tools for systemlevel analog design. Since this breakthrough, there has been continued innovation in development of mixed-signal reconfigurable arrays, i.e., those containing both analog and digital computation.

Wunderlich [5] presented a Field Programmable Mixed Array (FPMA) interleaving both analog and digital elements in a Manhattan-routable fabric. Their design consisted of Computational Analog Blocks (CABs) as well as Computational Logic Blocks (CLBs) interwoven through a global interconnect. The CLBs were comprised of LUTs and D Flip-Flops (D-FFs) while the CABs were comprised of elements such as capacitors, transistors, and op-amps. Additionally, each block contained a local interconnect consisting of a set of reconfigurable switches.

George [37] proposed a similar architecture which also integrated a 16-bit microprocessor for added computational capability, thus enabling a 1,000-fold improvement in energy efficiency in addition to a 100-fold decrease in die area compared to the digital equivalent. Finally, Choi [38] proposed an architecture which consisted of three separate arrays of CLBs, Arithmetic Logic Units

<sup>&</sup>lt;sup>2</sup> © 2020 IEEE. Part of this chapter is reprinted, with permission, from [35].

(ALUs) and Time-domain Configurable Analog Blocks (TCABs), with a network of "gluing blocks" interfacing the arrays with one another as well as external input/output. TCABs allow for dynamic reconfigurability of the analog function being implemented, in contrast to CABs which only allow for reconfigurability of interconnects.

Pyle [39] further built on earlier efforts implementing evolutionary computation on FPGAs [4, 40, 41] to explore the possibility of analog computation of mathematical functions, specifically, the square, square root, cube, and cube root functions. Pyle's approach was to use a Self-Scaling Genetic Algorithm (SSGA) to scale the function parameters to an acceptable range, at which point the computations were performed on an analog fabric and refined through a process of Differential Digital Correction (DDC), using the Cypress PSoC-5LP chip [39]. This approach was later extended to more generalized mathematical functions by Thangavel [42] by extending these functions for Puiseux series generalization accommodating negative and fractional exponents as power series algebraic expansions.

Table 1 summarizes the various approaches provided by the above-mentioned authors and provides a comparison to the design proposed herein.

#### NVM-Based FPGAs

Nonvolatile memories (NVMs), including memristors, Phase Change Memory (PCM), and Spin Torque Transfer-based Magnetic Random Access Memory (STT-MRAM) offer several advantages to conventional SRAM, including low static power consumption, high area density, and non-volatility. Thus, integration of these devices into FPGAs has been a popular research interest in recent years. Many works have focused on one of two options: replacing SRAM with NVMs as the storage element in look-up tables (LUTs), or replacing SRAM with NVM in routing

Table 1: Comparison of mixed-signal field-programmable fabrics which are suitable for various signal processing tasks.

| Work                       | Routing<br>Architecture          | CAB Elements                                                                                                           | CDB Elements                         | Highlighted Contributions                            |

|----------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------|

| Wunderlich [5]             | Manhattan                        | Operational transconductance<br>amplifiers, transistors, capacitors,<br>MITEs (multiple input translinear<br>elements) | 3-input Basic logic<br>element (BLE) | Integrated analog/digital computation                |

| George [36]                | Manhattan w/<br>µProc. Cores     | Operational transconductance<br>amplifiers, transistors, multipliers                                                   | 4-input Basic logic<br>element (BLE) | Integrated microprocessor with<br>CABs/CLBs          |

| Choi [37]                  | Separate TCAB/<br>ALU/CLB arrays | Time configurable analog blocks<br>(TCABs)                                                                             | 4-input programmable<br>LUT          | Programmability using TCABs                          |

| Schlottmann [35]           | Crossbar                         | Operational transconductance<br>amplifiers, transistors                                                                | N/A                                  | Dynamically reconfigurable<br>FPAA                   |

| M-FPA<br>(proposed herein) | Crossbar                         | Amplifiers, transistors, capacitors,<br>low-/high-barrier MTJs                                                         | 6-input Fracturable<br>C-LUT         | Spin-based FPA with NVM crossbar for CS applications |

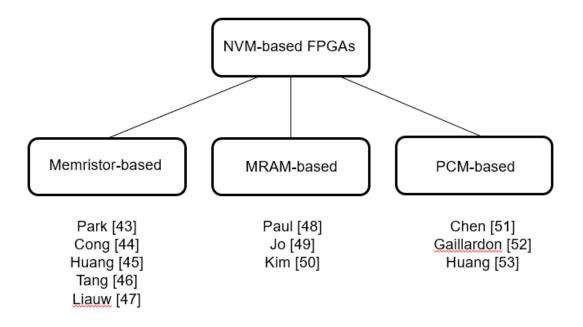

elements such as switching blocks (SBs) and connection blocks (CBs) [43, 44]. Fig. 2 gives a summary of selected works relating to NVM integration in FPGAs.

Cong [44] proposed using memristive crossbar arrays to implement switching blocks in the FPGA fabric. In this scheme, memristors and metal wires are stacked on top of CMOS access transistors to reduce area overhead. The authors determined that this optimization reduced the SB area overhead to negligible amounts, as opposed to CMOS-based SBs which consume 10% - 50% of the FPGA area. Specifically, a 96% reduction in area, 55% improvement in performance, and 79% reduction in power was attained. Similar results were reported by Huang [45] and Tang [46], among other authors.

Moreover, Liauw [47] was first to propose using memristors to replace SRAM in LUTs. Park [43] extended this idea to bring memristors and SRAM together to build hybrid FPGAs consisting of alternating SRAM-based and NVM-based LUTs. Such hardware allows for both power and performance optimization by placing SRAM-based logic blocks (superior in speed) on the critical path of an application, while using NVM-based logic blocks (superior in power consumption) elsewhere. Indeed, the placement algorithm developed by the authors around this idea attained a 22% average reduction in power consumption on the benchmarks tested, with only negligible increase in critical path delay.

In addition to memristors, STT-MRAM can be used as an NVM alternative which offers advantages in speed, endurance, and density. Paul [48] proposed CLBs with MTJs replacing SRAM cells, which could then be further improved using Shannon decomposition-based power gating. He found a 48% reduction in area, 22% delay improvement, and 16% power reduction compared to an equivalent CMOS design. Jo [49] proposed an 8-input MRAM-based LUT which attained 74% read power improvement compared to CMOS. Finally, Kim [50] designed a CAD tool for MRAM-based nonvolatile LUTs to address programmability issues that come with emerging technologies.

PCM is a further NVM possibility, offering high performance, scalability, and high density. PCM also allows for 3D die stacking, which can further enhance density, as well as performance, by shortening wire lengths, and power, by reducing parasitic capacitance of wires. In addition, PCM allows for implementation of Multi-Level Cells (MLCs) which can hold multiple bits within one device by programming multiple levels of resistances. Chen [51] found significant benefits in area, leakage power, and read energy by using MLC-PCM to replace SRAM in LUTs and routing blocks in an FPGA employing a 3D die-stacked architecture. Gaillardon [52] achieved similar results using PCM-based LUTs. Huang [53] further researched improving PCM retention time and leakage power, which are two major weaknesses of the technology. By using 0-V biasing during normal FPGA operation, he was able to reduce active leakage power to 1.19 nW and extend retention time to 10 years.

Fig. 2: Summary of selected previous approaches to beyond-CMOS NVM integration in reconfigurable fabrics

#### Hardware for Implementation of CS Sampling

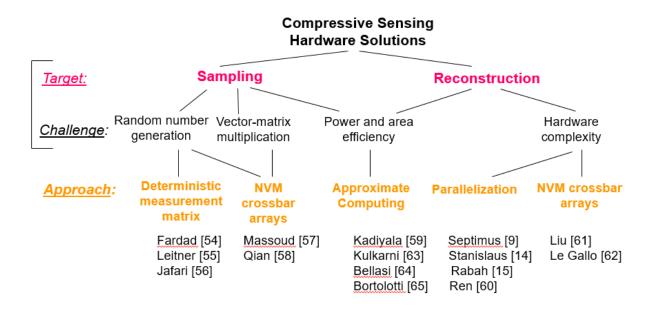

Implementing CS sampling and reconstruction in hardware present unique challenges. Sampling requires the use of a random number generator, which is traditionally implemented using a Linear Feedback Shift Register (LFSR) that can present significant power and area overheads [10]. Moreover, CS sampling requires a VMM operation which can be costly when dealing with large sample sizes. Potential solutions to these challenges include use of a deterministic measurement matrix and use of memristor crossbar arrays for VMM operations. Finally, approximate computing approaches can be used to alleviate power and area overheads. Fig. 3 provides a summary of these challenges and solutions. Fardad [54] published a paper outlining the use of deterministic measurement matrices in CS. His method was based on a parity check matrix based on hyperplanes in Euclidean geometry. Specifically, for prime *p* and two integers m > 1 and s > 0, an *m*-dimensional Euclidean geometry over the Galois field GF( $p^s$ ) can be defined. A  $\mu$ -dimensional subspace of the vector space of all *m*-tuples in this geometry is called a  $\mu$ -flat. Choosing two different values of  $\mu$ , i.e.,  $\mu_1$  and  $\mu_2$ , a matrix *H* can be defined with elements  $h_{ij} = 1$  if and only if the  $i^{th}\mu_2$ -flat contains the  $j^{th}\mu_1$ -flat (where  $\mu_2 > \mu_1$ ). This determines a deterministic, sparse, binary matrix. In CS reconstruction applications, the authors compared this to a Gaussian matrix and observed similar performance in terms of percentage of perfect signal reconstructions. In addition to avoiding overheads associated with random number generation, the authors noted a two-order-of-magnitude reduction in power consumption when using this matrix for signal reconstruction using OMP, versus the conventional technique of using a Gaussian matrix.

Leitner [55] proposed a different method of accomplishing CS sampling via a deterministic, sparse, binary measurement matrix, in the context of image sensors. Their method involves splitting the image pixels into sets of  $\frac{N}{M}$  + *OL* neighboring pixels, where *N* is the image size, *M* the number of measurements taken, and *OL* the size of the overlap between adjacent pixel sets. In this context, each measurement is determined by summing the values of all of the neighboring pixels in its corresponding group. The elements of the measurement matrix are hence given by:

$$\phi_{ij} = \begin{cases} 1 & if \ 1 \ + \ \frac{(i-1)N}{M} \le j \le \frac{iN}{M} + OL\\ 0 & otherwise \end{cases}$$

(3)

It is observed that while this matrix does not satisfy the RIP property, it does provide incoherence with the Inverse Discrete Cosine Transform (IDCT) basis. As such, this matrix works well with low-frequency images, but fails with high-frequency images. Specifically, the authors compared the peak signal-to-noise ratio (PSNR) of natural images reconstructed using the proposed matrix and a Gaussian matrix, using the technique of  $\ell_1$ -minimization. The results indicated that the proposed matrix outperformed the Gaussian matrix by 3.7 dB, on average. Signal reconstruction using the proposed matrix failed when using an artificial image comprised of alternating black and white pixels, though such an image would rarely appear in practice. The authors noted significant energy savings for an image sensor using this approach, when compared to previous works relying on LFSRs.

Finally, Jafari [56] proposed constructing a deterministic measurement matrix simply by choosing rows from the identity matrix, in the context of a wearable chip for seizure detection. Their results indicated a two-order-of-magnitude reduction in both latency and dynamic power consumption, compared to an equivalent system using LFSR to generate random matrices.

In contrast to the above techniques employing deterministic measurement matrices, Massoud [57] proposed using memristors to store the measurement matrix, taking advantage of their nonvolatility as memory devices, and hybrid logic-memory capabilities. In this approach, the authors proposed using LFSRs to program each memristor to one of two values, which would then act as multiplexers to modulate the input signal. Hence, the memristors were effectively being used to store a binary measurement matrix. The authors observed sufficient reconstruction accuracy using this approach, and cited potential benefits involving chip area, resilience to jitter, and hardware complexity.

Qian [58] built upon this work by introducing memristor crossbar arrays for VMM operations during CS sampling. In contrast to Massoud's approach of using LFSRs to generate random values, Qian proposed relying on the process variation inherent in memristor filament lengths to generate randomness. Due to the physical model of a memristor, consisting of a filament growing under certain connections to establish an electrical connection between two electrodes, randomness in filament length can result in randomness in device state under identical conditions. The authors observed that signal reconstruction using  $\ell_1$ -minimization yields similar PSNRs to that of using a Gaussian matrix, while eliminating expensive hardware such as LFSRs and multiply-accumulate units for digital VMM.

Finally, Kadiyala [59] proposed using approximate computation to reduce power and area overheads during the sampling stage. Their work was built upon two methods: *probabilistic pruning* and *probabilistic logic minimization*. Probabilistic pruning refers to removing elements of a circuit which do not make a large difference in the accuracy of the output data, whereas probabilistic logic minimization refers to flipping bits of certain output states to minimize the logic overhead. The authors found that when these techniques are applied to the multiply-accumulate units involved in the VMM architecture of CS sampling, a 54% reduction in power and 43% reduction in area can be attained at the cost of 1 dB reduction in PSNR.

Fig. 3: Summary of challenges and potential solutions relating to hardware implementation of Compressive Sensing. Each of the listed challenges is addressed by MFPA, as discussed in Chapter 1.

#### Hardware for Implementation of CS Reconstruction

Implementing reconstruction using OMP or any other algorithm presents challenges related to hardware complexity and power and area overheads. Approaches to addressing these issues have included maximizing parallelism inherent in the reconstruction algorithms, using memristive crossbar arrays to reduce hardware complexity, and once again using approximate computing to reduce power and area overheads at the cost of accuracy. These approaches are summarized in Fig. 3 and explained in more detail below.

Maximizing parallelization in the reconstruction approach has been a common theme in the literature. Septimus and Steinberg [9] were among the first to propose such an implementation. Their approach was to use an array of multipliers to accomplish the set of vector-matrix and vector-

vector multiplications in Step 2 of Algorithm 1 in parallel. They made use of the Moore-Penrose pseudo-inverse, defined as  $\boldsymbol{\Phi}_i^{\dagger} = (\boldsymbol{\Phi}_i^T \boldsymbol{\Phi}_i)^{-1} \boldsymbol{\Phi}_i^T$ , whereby the matrix inversion problem in Step 5 was reduced to that of inverting the symmetric matrix,  $\boldsymbol{C} = \boldsymbol{\Phi}_i^T \boldsymbol{\Phi}_i$ . This inversion could then be performed in a computationally efficient way by using the technique of Alternative Cholesky Decomposition to express  $\boldsymbol{C}$  in the form  $\boldsymbol{C} = \boldsymbol{L}\boldsymbol{D}\boldsymbol{L}^T$ , where  $\boldsymbol{L}$  is a lower triangular matrix and  $\boldsymbol{D}$  is a diagonal matrix. These computations are then performed using the same hardware used for Step 2.

Stanislaus and Mohsenin [14] significantly improved the performance of Algorithm 1 by modifying it to use a thresholding process to remove certain columns of  $\boldsymbol{\Phi}_i$  based on relative magnitude of the dot product. Their architecture involved separate hardware cores to perform the two optimization problems involved in the algorithm. Rabah [15] used the same algorithm and computation approach as [9]; however, they designed a four-stage architecture aimed at maximizing the utilization of parallelism as well as reuse of hardware. Their architecture consisted of 1) inner product and comparator unit, 2) Cholesky inversion unit, 3) residual computation unit, and 4) reconstructed signal computation unit. This approach yielded an improvement in performance for large-signal analysis, compared to previous works. Finally, Ren [60] proposed a parallel CS FPGA-based architecture consisting of configurable processing elements, including both a scalar core supporting scalar comparison, addition, accumulation, and division, and a separate core for vector operations. The authors found a speedup of 41x in their implementation compared to the execution time observed on a CPU. All of the implementations discussed in this section rely on purely-digital computation via FPGAs: Xilinx Virtex-5 components were used in [9] and [14], while Xilinx Virtex-6 was used in [15] and Kintex-7 was used in [60].

In contrast to the above approaches relying on parallelization, Liu [61] proposed using memristors for computationally efficient reconstruction in the presence of noise. Their idea was to reformulate the  $\ell_1$ -minimization problem using the alternating directions method of multipliers (ADMM). ADMM allows one to solve the  $\ell_1$ -minimization problem by following an iterative algorithm consisting of three steps: two steps involve only simple vector operations, while the other step can be solved through vector-matrix multiplication. Using a memristor crossbar array to conduct vector-matrix multiplication operations yields O(1) complexity for that step for matrices having ranks not exceeding the size of the array, while the complexity of the rest of the algorithm is O(n). This yields an overall complexity of O(n) for the noisy CS problem, compared to a complexity of  $O(n^{3.5})$  using alternative approaches such as second-order cone program.

Le Gallo [62] took a similar approach of using memristive PCM arrays, which were used to implement both CS sampling and reconstruction. An Approximate Message Passing (AMP) algorithm was used for reconstruction, which consists of VMM operations as well as simple vector operations. Similar to Liu, the crossbar array was used to implement the VMM to achieve an overall complexity of O(n). In addition, due to the crossbar's property of only requiring read operations during the multiplication, and eliminating the need for multiply-accumulate units, a 98% reduction in dynamic power consumption was observed compared to an equivalent FPGA design.

Kulkarni and Mohsenin [63] took yet a different approach to improving the performance of CS reconstruction. Beginning with the OMP algorithm, they introduced modifications to improve performance at the cost of accuracy. One modification proposed by them was the thresholding technique OMP algorithm (tOMP), which introduces a *column reduction* phase before the counter is incremented at each step of the algorithm. The column reduction phase is a thresholding technique which eliminates *p* columns from the column set  $\Phi_i$ ' at each iteration of the algorithm, corresponding to the least significant elements of the index set,  $\Lambda_i$ . The result is a reduction in complexity in the VMM operations, with (n - kp)m multiplications being required at the  $k^{th}$  iteration during Step 2 of Algorithm 1. An alternate modification to the OMP algorithm proposed by the authors is gradient descent OMP (GDOMP), where the least squares minimization operation in Step 5 of Algorithm 1 is replaced by a stochastic gradient descent minimization. Thus, tOMP and GDOMP seek to reduce hardware complexity at two distinct stages of the OMP algorithm.

GDOMP and tOMP result in energy improvements of 5% and 23% over OMP, respectively. In addition, tOMP results in a 27% reduction in reconstruction time, and GDOMP takes 33% less area, compared to OMP. Bellasi [64] took a parallel approach through their modified OMP algorithm, which introduces a rounding stage at each iteration to reinforce integer-valued results. Finally, Bortolotti [65] proposed approximate computing at the hardware level in the context of wearable health monitoring devices. To address the memory power wall so critical to wearable electronics, the authors proposed storing the CS measurement matrix using low-V<sub>DD</sub> SRAM cells, at the cost of higher probabilities of bit flips, after which a proximal gradient descent algorithm is used for reconstruction. Due to the robust nature of CS reconstruction, the authors observed that they were able to reduce  $V_{DD}$  down to 0.6 V while retaining a near-100% recovery probability and attaining a 60% reduction in power consumption.

#### Summary

While FPGAs have traditionally been CMOS-based digital devices comprised of CLBs using LUTs to implement logic functions, there have been two parallel directions of research into changing this architecture. The first aims at introducing analog computation into reconfigurable fabrics by the addition of CABs in addition to CLBs. This allows for efficiency in applications such as signal processing which are most efficiently carried out in the analog domain. The second research direction seeks to replace SRAM cells comprising FPGA LUTs and routing architecture by NVM equivalents. This brings several benefits compared to CMOS, especially in terms of area overhead and static power consumption.

CS is one application well-suited for FPGAs. In the sampling phase, CS challenges the underlying hardware to rapidly generate random numbers and carry out VMM while maintaining area and overheads suitable for wearable and IoT devices. Solutions taken towards these problems have included using a deterministic measurement matrix to avoid costs associated with random number generation, as well as carrying out VMM using NVM crossbar arrays to reduce the power and delay costs associated with a sequence of multiply-accumulate operations. On the reconstruction side, the underlying hardware is challenged to implement a suitable reconstruction algorithm while maintaining an acceptable level of power and area overhead as well as hardware complexity. Solutions here have included maximizing parallelism in hardware, utilizing

approximate computing to minimize power and area overheads, and again using NVM crossbar arrays to reduce overheads associated with VMM.

## **CHAPTER THREE: MFPA PLATFORM<sup>3</sup>**

Herein, a device-level-to-architecture-level approach is proposed to integrate front-end signal processing within a low-footprint reconfigurable fabric that enables mixed-signal processing. This approach advances hybrid spin/CMOS Mixed-signal Field Programmable Arrays (MFPAs), which enable high-throughput on-chip Compressive Sensing via established algorithms for signal reconstruction. Mixed-signal techniques combined with in-memory computation geared to the demands of Compressive Sensing will be combined in a field-programmable and run-time adaptable platform.

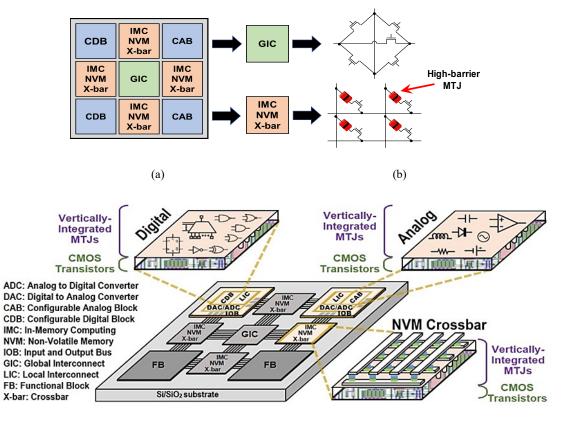

As shown in Fig. 4, the MFPA architecture entails a circuit and register-level design so that an MFPA slice acquires analog signals and then performs CS sampling and reconstruction via In-Memory Computing (IMC) using reduced precision/dynamic range. IMC approaches extend related works, such as Rabah's architecture [15] consisting of separate processing elements (PEs) and memory elements (MEs). The proposed architecture develops analog computable memories, or analog computing arrays, where instead of storing the analog values to be used by external computing elements, IMC is utilized. This cross-cutting beyond von Neumann architecture explores the use of dense emerging NVM arrays to perform VMM necessary for execution of CS signal reconstruction algorithms such as OMP.

Low energy barrier MTJs are used as compact TRNGs for generation of the CS measurement matrix, as justified within previously-published work [10]. The proposed MFPA is composed of

<sup>&</sup>lt;sup>3</sup> © 2020 IEEE. Part of this chapter is reprinted, with permission, from [35].

(c)

Fig. 4: (a) Single-slice organization for proposed MFPA architecture, (b) MFPA routing and switch interconnect design, and (c) Hybrid spin/charge device realization as configurable blocks within the MFPA fabric

two types of Functional Blocks (FBs): Configurable Digital Blocks (CDBs) and Configurable Analog Blocks (CABs), similar to CABs and CLBs used in previous CMOS-based FPMAs [5, 37]. These FBs are connected via the embedded NVM Crossbar Arrays which perform VMM. Furthermore, within the CDBs the recently-published MTJ-based Look-Up Table (LUT) [3] is used to implement Boolean functions via IMC. Additionally, hybrid spin-CMOS ADCs [66] are used within CABs.

Thus, MTJs are investigated for selected processing roles to simultaneously reduce area and energy requirements while providing stochasticity and non-volatility needed by the OMP algorithm. MFPAs can advance a unified platform on a single die accommodating a continuum of information conversion losses and costs targeting CS applications. Design of such a mixed-signal reconfigurable fabric can enable feasible hardware approaches that can execute CS algorithms more efficiently than digital FPGA-based or CPU-based implementations, which can then be extended to low-energy miniaturization for IoT sensing applications. The parallelism enabled by the fabric is reaily applicable to other areas as well, such as artificial intelligence [67].

## NVM Crossbar

The proposed MFPA architecture utilizes a  $50 \times 50$  Global Interconnect Crossbar (GIC) as well as  $50 \times 50$  NVM crossbar arrays connecting the analog and digital blocks. The NVM crossbar arrays consist of deterministic bit cells, along with probabilistic low-energy barrier p-bits to realize energy- and area-efficient implementation of CS applications.

As previously mentioned, p-bits enable true random number generation based on thermally unstable MTJs. In this design, the probabilistic behavior of the device is tunable. This approach requires just a single p-bit and a D-FF to quantize the output to a 1 or 0. Whereas the tunable stochastic voltage range of p-bits is only  $\pm 50$  mV, a current-summation approach is used to perform the matrix multiplication of the input vector with the weight matrix that corresponds to the measurement matrix of the CS algorithm. By utilizing a collection of programmable resistive elements for each weight with a fixed read current, the voltage applied to a p-bit can be tuned,

Fig. 5: MFPA NVM Crossbar consisting of 8 MTJs per cell for In-Memory Computing, where red signals show the configuration flow, the blue signals depict the path for populating the measurement matrix and green signals illustrate the path for VMM operation which in turn adjusts the probability of reading a 1 or 0. Therein, MTJ devices with a high energy barrier, such as 40 *kT*, maintain the CS matrix data in a non-volatile manner, as Fig. 5 shows.

The MFPA crossbar operates by applying inputs to either the rows or columns and reading the resulting node states, which allows the MFPA to efficiently realize CS applications. Fig. 5 depicts a possible implementation of the NVM Crossbar. MTJs are the targeted devices for adjusting the voltage applied to the input of the output p-bit device given a fixed current. According to detailed analysis, a write voltage with  $\pm$  50mV range can provide the desired probabilistic switching behavior. The positive and negative voltage range is achieved through connecting one of the write terminals to a fixed voltage of 50mV, while the other terminal can alter from 0V to  $V_{IN-MAX} =$  100mV. The read current, *I<sub>READ</sub>*, is defined based on the size of the array, as elaborated in Equation

$$I_{READ} = \frac{V_{IN-MAX} \times Number of Array Rows}{R_{MTJ}}$$

(4)

where  $R_{MTJ}$  is the MTJ resistance in the anti-parallel state, and  $V_{IN-MAX}$  is the maximum input voltage allowed to ensure the designed probabilistic behavior for the p-bit device. The total power consumption of the array during the read process can be calculated using Equation 5:

$$P_{READ} = I_{READ} \times V_{DD} \times Num. of Array Columns$$

(5)

Within this array, the input voltage range only depends on the TMR value of the MTJ, as expressed by Equation 6:

$$\frac{V_{IN-MAX}}{1+TMR} < V_{IN} < V_{IN-MAX} \tag{6}$$

so that the total read energy consumption of the array is determined by  $E_{READ} = P_{READ} \times T_{SW}$  where  $T_{SW}$  is the switching time of the p-bit device, which is on the order of 10 ps based on simulation results. However,  $T_{SW}$  is lower than the time required for MOS transistor switching, so the energy consumption is limited by the circuit clock frequency.

#### Configurable Digital Blocks (CDBs)

Fig. 6(a) shows the proposed CDB design, similar to the architecture proposed by Wunderlich *et al.* [5]. Each CDB takes *N* inputs and produces *M* outputs. The building block of the CDB is the C-LUT, as described in Chapter 1 and shown in Fig. 6(b). Each C-LUT can provide two 5-input Boolean logic functions or one 6-input function. Consequently, each C-LUT contains  $2^6 = 64$  memory cells. The CDB is able to interface with the analog inputs/outputs of the NVM Crossbar

through analog-digital and digital-analog conversion. Herein, the aforementioned spin-based AIQ is used for signal conversion while the C-LUT is configured to realize a LUT-based encoder [30].

Fig. 6: (a) MFPA CDB structure and (b) C-LUT circuit components utilized for CDB logic select/retrieval [3]

## Configurable Analog Blocks (CABs)

The proposed CAB design is shown in Fig. 7(a). The CAB elements include four Operational Transconductance Amplifiers (OTAs), four PMOS/NMOS transistors, four capacitors, and both high energy barrier and low energy barrier MTJs. The CAB utilizes local interconnect dimensions of  $50 \times 25$ . Local routing interconnects are programmed to configure CABs to implement functions such as square/square root, which are complex to implement digitally yet necessary for many CS reconstruction algorithms, e.g., for computation of vector norm. These functions can be implemented based on an analog multiplier circuit using the configuration shown in Fig. 7(b).

Fig. 7: (a) MFPA CAB structure and (b) configuration of an analog multiplier circuit using CAB elements

# CHAPTER FOUR: ENERGY AND DELAY PERFORMANCE OF MFPA COMPONENTS<sup>4</sup>

The HSPICE circuit simulator is used to validate the functionality of the C-LUT using the 14 nm Technology FinFET Predictive Model (PTM) libraries [68], the STT-MRAM model developed by Kim *et al.* in [69], the VCMA-STT-MRAM model developed by Kang *et al.* in [70], and the pbit model developed by Camsari *et al.* in [71] to validate the functionality of the CDB and CAB elements used in the proposed MFPA. Previous hardware-based CS implementations have included stochastic CMOS [72] and hybrid CMOS-memristor designs [73], as well as CMOS FPGAs for signal reconstruction [9, 14, 15]. For instance, reconstruction time using a CMOS FPGA was found to be 24 µs in comparison to 68 ms using a CPU implementation and 37.6 ms on a GPU [9]. However, CMOS-based designs suffer from significant area and leakage power overheads, as well as limited quality of randomness from linear feedback shift registers (LFSRs), in comparison to emerging device TRNG approaches [10].

## NVM Crossbar

To estimate the energy reduction of the present approach over a pure-CMOS approach, the necessary CMOS elements required to implement a  $100 \times 25$  single-cycle parallel weighted sum operation using 8-bit weights are considered, which is comparable to the computation performed

<sup>&</sup>lt;sup>4</sup> © 2020 IEEE. Part of this chapter is reprinted, with permission, from [35].

| Array Size | CMOS X-bar Energy | NVM X-bar Energy | Energy Improvement |

|------------|-------------------|------------------|--------------------|

| 100×25     | 1,177 pJ          | 240 pJ           | ~5X                |

| 200×50     | 4,708 pJ          | 968 pJ           | ~4.8X              |

| 400×100    | 18,832 pJ         | 3840 pJ          | ~4.9X              |

Table 2: Comparison of energy needed for VMM in CMOS crossbar vs. proposed NVM crossbar.

within the analog array of a  $100 \times 25$  matrix. Each weight would require eight SRAM cells to store the 8-bit weight as well as eight AND gates and eight 1-bit Full Adders to multiply the input bit with the weight. This yields a total of 20,000 SRAM cells consuming 1,050 pJ in-total [74], along with 20,000 Full Adders consuming 106 pJ [75, 76] in aggregate, and 20,000 AND gates consuming roughly 21 pJ collectively. Thus, a grand total of 1,177pJ per operation is consumed by the CMOS-only design, which is roughly 5-fold more energy for computation than in the proposed MFPA's NVM Crossbar. Additionally, a spin-based approach offers non-volatility, as opposed to volatile SRAM cells. Moreover, the CMOS-only approach requires 640,287 transistors, while the MFPA utilizes just 20,000 MTJ devices each having an access transistor, which achieves a ~26-fold device reduction contributing considerable area savings per the results listed in Table 2.

## <u>CDB</u>

Simulation results indicate that the average read energy consumption of the C-LUT is 21.9 fJ while the write energy consumption of the C-LUT is 155.2 fJ. Additionally, according to the results, the C-LUT achieves more than 80% standby power consumption reduction while providing around 25% reduced area footprint compared to a CMOS-based LUT.

## CAB

The CABs are used to implement circuits for computing square/square root operations used in CS reconstruction algorithms, such as for calculating vector norm. In addition, an inverse square root circuit can also be implemented as a common operation in both CS sampling (i.e., normalizing the measurement matrix using the norm) and CS reconstruction. Fig. 7(b) shows the circuit used. This circuit consists of three stages: the first stage is a logarithmic amplifier, with output voltage  $V_1$  given by:

$$V_1 = -n_1 V_T ln\left(\frac{V_{in}}{RI_{s1}}\right) \tag{7}$$

where  $V_T$  is thermal voltage, R is the resistance used in that stage,  $I_{s1}$  is the diode saturation current, and  $n_1$  is the diode ideality factor, given by:  $n_1 = \frac{r_{s1}I_{s1}}{V_T}$  with  $r_{s1}$  being diode saturation resistance. The second stage is an analog adder, with output voltage  $V_2$  given in terms of the input  $V_1$  as  $V_2 = -2V_1$ . Finally, the third stage is an anti-log amplifier with output voltage given in terms of input voltage  $V_2$  as:

$$V_{out} = -RI_{s2}e^{\frac{V_2}{n_2 V_T}}.$$

(8)

Overall, it is simple to see that the output of this circuit is given by:

$$V_{out} = -\frac{RI_{s_2}}{(RI_{s_1})^{2n_1/n_2}} (V_{in})^{2n_1/n_2}.$$

(9)

According to this theory, the circuit shown in Fig. 4(b) can be used to implement any positive power function of the input voltage by modifying the diode characteristics in the input/output stages. Furthermore, by inserting a standard inverting amplifier before the final exponentiation, the circuit output becomes:

$$V_{out} = -\frac{RI_{s2}}{(RI_{s1})^{2n_1/n_2}} (V_{in})^{-2n_1/n_2}$$

(10)

in which case any inverse power function can be implemented as well.

This circuit was simulated in HSPICE using the 14 nm PTM LSTP transistor library [36], with parameters modified to achieve squaring and square root operations. Finally, an inverting amplifier was inserted before the final stage to achieve inverse square root operations as well. The results of these simulations are listed in Table 3 for the squaring circuit, Table 4 for the square root circuit, and Table 5 for the inverse square root circuit.

| V <sub>DD</sub>  | 0.8 V                 |

|------------------|-----------------------|

| Input range      | $0.2 \ V - 0.6 \ V$   |

| Output range     | $0.02 \ V - 0.18 \ V$ |

| Computation Time | 3.5 ns                |

| Average Power    | 126 μW                |

| Average Error    | 1.2%                  |

| Max Error        | 6.0%                  |

Table 3: Data for analog squaring circuit.

| V <sub>DD</sub>  | 0.8 V                 |

|------------------|-----------------------|

| Input range      | $0.2 \ V - 0.6 \ V$   |

| Output range     | $0.20 \ V - 0.34 \ V$ |

| Computation Time | 6.4 ns                |

| Average Power    | 122 μW                |

| Average Error    | 0.7%                  |

| Max Error        | 2.4%                  |

Table 4: Data for analog square root circuit.

Table 5: Data for analog inverse square root circuit.

| V <sub>DD</sub>  | 0.8 V               |

|------------------|---------------------|

| Input range      | $0.2 \ V - 0.6 \ V$ |

| Output range     | 1.3 – 2.3 mV        |

| Computation Time | 3.0 ns              |

| Average Power    | 166 μW              |

| Average Error    | 0.4%                |

| Max Error        | 1.6%                |

The result for the squaring circuit can be compared to an approximate 8-bit digital multiplier, proposed in earlier work [77]. The digital multiplier, operating at a  $log_2(mean\ relative\ error\ distance) = -6$  (i.e., average error of roughly 1.6%, slightly worse than the proposed analog design), delivered average power consumption of 126  $\mu$ W while consisting of approximately 245 logic gates (i.e., roughly 980 transistors) while the proposed analog design consists of only 30 transistors. Thus, the squaring circuit produced herein produces slightly better error than the approximate digital multiplier, while delivering a 97% reduction in transistor count.

## **CHAPTER FIVE: ASSESSMENT OF ERROR TOLERANCE**

Due to CS reconstruction being intrinsically lossy, it seems as though a small amount of computational error would not cause significant degradation in reconstruction performance, as long as the error is within a reasonable threshold below that seen in typical measurement noise (e.g., within 10%). This has been one of the primary motivations behind using approximate analog computation for performing difficult operations such as square and square root. While the computation errors obtained with these functions is within reasonable bounds, it is worth determining the impact on different CS reconstruction algorithms.

In this chapter, three commonly-used algorithms are implemented: OMP, Compressive Sampling Matching Pursuit (CoSaMP), and Approximate Message Passing (AMP). In each case, 50 random signals are generated using MATLAB, in addition to a Gaussian measurement matrix with normalized columns. CS parameters used are n = 1000, k = 100, and m between 200 and 500. For each value of m, the average reconstruction error seen amongst the 50 tested signals is recorded, where reconstruction error (in dB) is computed as:  $e = 20 \log \frac{\|\hat{x}-x\|}{\|x\|}$  with x being the original signal and  $\hat{x}$  being the reconstructed signal.

Data obtained in this way is compared between two trials: Trial 1 uses exact computation, while Trial 2 uses approximations when computing square and square root operations. This includes computation of square and square root for normalization of the CS measurement matrix during the sampling phase. Errors are injected by multiplying squared values by a Gaussian random variable with mean 1 and standard deviation of 0.02, and multiplying square roots by a Gaussian random variable with mean 1 and standard deviation of 0.01. These distributions are

meant to approximate the error data reported in Table 3 and Table 4, respectively. Comparing the reconstruction errors in this way allows for a direct assessment of the impact delivered by using CABs for approximate computation.

#### <u>OMP</u>

The OMP Algorithm has already been presented in the introduction and discussed extensively in thesis. While the OMP algorithm does not include explicit square and square root computations, these operations are necessary for normalization of the CS measurement matrix before the reconstruction phase can commence. Based on the errors introduced into these operations, Fig. 8 shows the error data obtained.

Fig. 8: Reconstruction error using OMP

It is seen from the graph that reconstruction error between trials using exact and approximate computation is usually negligible, except in the case when 300 measurements are taken. However, if a certain level of error (e.g., -60 dB) is expected, then the minimum number of measurements will be the same in both cases.

## <u>CoSaMP</u>

The CoSaMP algorithm presents optimizations over OMP to allow for greater robustness over measurement noise. The algorithm is presented as Algorithm 2 below [78]:

| Algorit                | <b>hm 2</b> Compressive Sampling Matching Pursuit                                                                                                                        |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inputs                 | : The measurement matrix, $oldsymbol{\Phi}$                                                                                                                              |

|                        | The measurement vector, $\mathbf{y}$                                                                                                                                     |

|                        | The signal sparsity, $k$                                                                                                                                                 |

| Output                 | : The approximate signal vector, $\mathbf{a}$                                                                                                                            |

| Proced                 | ure:                                                                                                                                                                     |

|                        | Initialize the residual $\mathbf{r}_0 = \mathbf{y}$ , the signal approximation $\mathbf{a}_0 = 0$ , and the nter $i = 1$ .                                               |

| $\mathbf{w}\mathbf{h}$ | $\mathbf{ile} \ i < k \ \mathbf{do}$                                                                                                                                     |

| 2) ]                   | Form the signal proxy, $\mathbf{z} = \Phi^T \mathbf{r}_{i-1}$ .                                                                                                          |

|                        | Define $\Omega$ as the support set of the $2k$ largest components of $\mathbf{z}$ : $\Omega = p(\mathbf{z}_{2k})$ .                                                      |

| 4)                     | Define set T as the union of $\Omega$ and the support of $\mathbf{a}_{i-1}$ : T = $\Omega \cup p(\mathbf{a}_{i-1})$ .                                                    |

| 5) S                   | Solve a least squares problem to determine the updated solution for the nal, $\mathbf{\hat{x}}$ : $\mathbf{\hat{x}} _T = \arg \min   \mathbf{y} - \Phi_T \mathbf{x}  $ . |

| 6) \$                  | Set $\hat{\mathbf{x}} _{T^c} = 0.$                                                                                                                                       |

| 7)]                    | Prune $\hat{\mathbf{x}}$ to keep the k largest components: $\mathbf{a}_i = \hat{\mathbf{x}} _k$ .                                                                        |

| 8) 1                   | Update the residual: $\mathbf{r}_i = \mathbf{y} - \mathbf{\Phi} \mathbf{a}_i$ .                                                                                          |

| 9) ]                   | Increment the counter, $i$ .                                                                                                                                             |

| end                    | while                                                                                                                                                                    |

While the working principle of CoSaMP is similar to OMP (picking columns from  $\boldsymbol{\Phi}$  most closely correlated with  $\boldsymbol{r}$ , and using these columns to perform least squares minimization to estimate the signal), CoSaMP picks multiple columns from  $\boldsymbol{\Phi}$  at each iteration as an effort to still pick the most closely-correlated column at every step, even if this correlation has been degraded due to measurement noise. CoSaMP results are shown in Fig. 9 below.

## Fig. 9: Reconstruction error using CoSaMP

Like OMP, CoSaMP does not explicitly require square and square root operations, and only relies on these operations to normalize the measurement matrix during the sampling phase. As with OMP, deviations in measurement error when using CABs for approximate computing are negligible.

## AMP

While OMP and CoSaMP belong to the class of greedy reconstruction algorithms, AMP is a soft thresholding algorithm designed for fast convergence [79]. The algorithm is presented as Algorithm 3 below: Algorithm 3 Approximate Message Passing

Inputs: The measurement matrix,  $\Phi$ The measurement vector,  $\mathbf{y}$ The number of measurements, mOutput: The approximate signal vector,  $\hat{\mathbf{x}}$

## Procedure:

1) Initialize the residual  $\mathbf{r}_0 = \mathbf{y}$ , the signal approximation  $\hat{\mathbf{x}}_0 = \mathbf{0}$ , and the counter i = 1.

while i < k do 2)  $\theta = \|\mathbf{r}_{i-1}\|/\sqrt{m}$ 3)  $\mathbf{a} = \hat{\mathbf{x}}_{i-1} + \Phi^{\mathbf{T}}\mathbf{r}_{i-1}$ 4)  $\hat{\mathbf{x}}_i = \operatorname{sign}(\mathbf{a})\max(|\mathbf{a}| - \theta, 0)$ 5)  $b_i = \|\mathbf{x}_i\|_0/m$ 6)  $\mathbf{r}_i = \mathbf{y} - \Phi \mathbf{x}_i + b_i \mathbf{r}_{i-1}$ end while

In this notation, sign(a)max( $|a| - \theta$ , 0) refers to element-wise vector operations, where the constant value  $\theta$  is applied to each element. The function sign(*x*) is defined to be +1 for *x* > 0 and -1 for *x* < 0. Unlike OMP or CoSaMP, AMP uses less matrix multiplication operations and does not require a least squares minimization operation. Thus, AMP is known for relatively fast convergence [79]. Moreover, AMP requires explicit calculation of square and square root in each iteration. The error analysis for approximate computation was performed for AMP, as for the previous algorithms, with results presented in Fig. 10. Despite the explicit reliance on square and square root operations, AMP also shows negligible impact from approximating these operations.

Fig. 10: Reconstruction error using AMP

Table 6 lists the value of  $m_c$ , i.e., the minimum number of measurements necessary to attain a reconstruction error less than -60 dB using exact versus approximate square and square root operations (given to within 5 measurements). The table demonstrates no need to increase number of measurements for OMP and CoSaMP, with AMP needing 2.5% more measurements to attain the same measurement error. Thus, the overall conclusion is that the approximation error presented by the CABs has minimal impact on CS reconstruction accuracy and performance of the MFPA.

| Algorithm | $m_c$ (exact) | $m_c$ (approximate) |

|-----------|---------------|---------------------|

| OMP       | 390           | 390                 |

| CoSaMP    | 370           | 370                 |

| AMP       | 395           | 405                 |

Table 6: Minimum number of measurements needed for -60 dB error, using exact and approximate square/square root operations.

## **CHAPTER SIX: FABRIC-BASED CS REALIZATION**

Sampling Architecture

As outlined in Chapter 1, Compressive Sensing (CS) requires a measurement matrix,  $\boldsymbol{\Phi}$ , which multiplies the signal vector x to yield the compressed measurement vector, y. Often the signal vector will contain a region of interest (RoI) sampled at a higher rate than the rest of the signal. To accomplish this, the columns in  $\boldsymbol{\Phi}$  which coincide with the RoI should have a higher concentration of nonzero elements than the other columns. As proposed by Salehi et al. [10] the measurement matrix can be generated using a spin-based crossbar architecture as shown in Fig. 5. In this approach, p-bits located at the top of each column are used to populate their respective columns. The input voltage to the p-bit at each column allows for tunable stochasticity of the output which can be utilized to generate the CS measurement matrix adaptively according to the signal characteristics such as noise, sparsity rate, and region of interest. The p-bit enables a tunable TRNG, in which higher input voltage yields a higher probability of nonzero values being generated. The p-bit output is amplified via a CMOS inverter and fed into a power-gated D-FF to generate a digital output string, and these values are written into the measurement matrix row-byrow, i.e., one row per clock cycle. As shown in Fig. 5, the red lines show the configuration flow, the blue lines depict the path for populating the measurement matrix and the green lines illustrate the path for the VMM operation.

## **Reconstruction Architecture**

After the measurement matrix is generated, and values are stored in the NVM array, any algorithm can be used for signal reconstruction. For the purposes of this chapter, Algorithm 3 (AMP) will be used. In this example, the CS parameters assumed are n = 256 and m = 64. Thus, the size of  $\boldsymbol{\Phi}$  is 256 × 64, vectors  $\boldsymbol{y}$  and  $\boldsymbol{r}$  have length 64, and vectors  $\hat{\boldsymbol{x}}$  and  $\boldsymbol{a}$  have length 256.