# AN ADAPTIVE MODULAR REDUNDANCY TECHNIQUE TO SELF-REGULATE AVAILABILITY, AREA, AND ENERGY CONSUMPTION IN MISSION-CRITICAL APPLICATIONS

by

# RAWAD N. AL-HADDAD B.S. JORDAN UNIVERSITY OF SCIENCE AND TECHNOLOGY, 2003 M.S. UNIVERSITY OF CENTRAL FLORIDA, 2008

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2011

Major Professor: Ronald F. DeMara

© 2011 Rawad N. Al-Haddad

# ABSTRACT

As reconfigurable devices' capacities and the complexity of applications that use them increase, the need for self-reliance of deployed systems becomes increasingly prominent. A *Sustainable Modular Adaptive Redundancy Technique (SMART)* composed of a dual-layered *organic system* is proposed, analyzed, implemented, and experimentally evaluated. SMART relies upon a variety of self-regulating properties to control availability, energy consumption, and area used, in dynamically-changing environments that require high degree of adaptation. The hardware layer is implemented on a Xilinx Virtex-4 *Field Programmable Gate Array (FPGA)* to provide self-repair using a novel approach called a *Reconfigurable Adaptive Redundancy System (RARS)*. The software layer supervises the organic activities within the FPGA and extends the self-healing capabilities through application-independent, intrinsic, evolutionary repair techniques to leverage the benefits of dynamic *Partial Reconfiguration (PR)*.

A SMART prototype is evaluated using a Sobel edge detection application. This prototype is shown to provide sustainability for stressful occurrences of transient and permanent fault injection procedures while still reducing energy consumption and area requirements. An *Organic Genetic Algorithm (OGA)* technique is shown capable of consistently repairing hard faults while maintaining correct edge detector outputs, by exploiting spatial redundancy in the reconfigurable hardware.

A Monte Carlo driven *Continuous Markov Time Chains (CTMC)* simulation is conducted to compare SMART's availability to industry-standard *Triple Modular Technique (TMR)*

techniques. Based on nine use cases, parameterized with realistic fault and repair rates acquired from publically available sources, the results indicate that availability is significantly enhanced by the adoption of fast repair techniques targeting aging-related hard-faults. Under harsh environments, SMART is shown to improve system availability from 36.02% with lengthy repair techniques to 98.84% with fast ones. This value increases to "five nines" (99.9998%) under relatively more favorable conditions.

Lastly, SMART is compared to twenty eight standard TMR benchmarks that are generated by the widely-accepted BL-TMR tools. Results show that in seven out of nine use cases, SMART is the recommended technique, with power savings ranging from 22% to 29%, and area savings ranging from 17% to 24%, while still maintaining the same level of availability.

To my wife, Reem.

To my father, mother, and brother.

# ACKNOWLEDGMENTS

This research was sponsored by the Defense Advanced Research Projects Agency (DARPA) under contract #W31P4Q-08-C-0168.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                              |

|------------------------------------------------------------------------------|

| LIST OF TABLES xii                                                           |

| CHAPTER 1: INTRODUCTION                                                      |

| 1.1. Need for Autonomous Repair in Mission Critical Applications1            |

| 1.2. Advantages of Reconfigurable Logic to Support Fault-Tolerance           |

| 1.3. Contributions of the Dissertation7                                      |

| 1.3.1. Design and Implementation of SMART7                                   |

| 1.3.2. Autonomous Fault-Tolerance Technique to Improve Availability10        |

| 1.3.3. Evaluating Self-Regulation of Availability, Area, and Energy          |

| CHAPTER 2: RELATED WORK                                                      |

| 2.1. Device Technology Related Work15                                        |

| 2.1.1. Role of Reconfigurable Devices in Space Mission-Critical Applications |

| 2.1.2. Failure Modes and Their Effects                                       |

| 2.2. Application Related Work                                                |

| 2.2.1. Fault Tolerance in Reconfigurable Devices                             |

| 2.2.2. Organic Computing Approaches                                          |

| 2.2.3. Genetic Algorithm Techniques                                          |

| 2.2.3.1. Standard GA Techniques                                              |

| 2.2.3.2. Parallel GA Techniques                                              |

| CHAPTER 3: SMART DESIGN OBJECTIVES                                           |

| 3.1. Exploit Reconfigurability to Realize Adaptive Level of Redundancy       |

| 3.2. I  | Develop Organically Amenable Hard-Fault Repair Techniques    | 39 |

|---------|--------------------------------------------------------------|----|

| 3.3. I  | mplement SMART and Evaluate it Using Widely Accepted Metrics | 42 |

| CHAPTER | R 4: A SMART ARCHITECTURE FOR MISSION-CRITICAL SYSTEMS       | 45 |

| 4.1. F  | RARS Hardware Layer                                          | 46 |

| 4.1.1.  | Motivation as a Hybrid of Approaches                         | 47 |

| 4.1.2.  | Architecture and Components                                  | 49 |

| 4.1.3.  | Range of Possible Configurations                             | 51 |

| 4.2.    | Organic Fault-Tolerance Software Management Layer            | 54 |

| 4.2.1.  | Architecture and Components                                  | 56 |

| 4.2.2.  | Scrubbing and Amorphous Spares                               | 57 |

| 4.2.3.  | Organic GA Repair Technique                                  | 59 |

| 4.2     | .3.1. Direct Bitstream Evolution                             | 59 |

| 4.2     | .3.2. Intrinsic Fitness Evaluation                           | 62 |

| 4.2.    | .3.3. Model-Free Fitness Function                            | 62 |

| 4.2.    | .3.4. OGA Design and Implementation                          | 64 |

| 4.3. F  | Fault-Handling Handshaking-Based Communication Protocol      | 68 |

| 4.4. I  | Dynamic Partial Reconfiguration                              | 71 |

| 4.5. T  | The Repair Cycle and Self-x Properties                       | 74 |

| CHAPTER | R 5: EXPERIMENTS AND RESULTS                                 | 79 |

| 5.1. E  | Experimental Configuration: Edge Detection Application       | 79 |

| 5.2. U  | Use Case Results                                             | 85 |

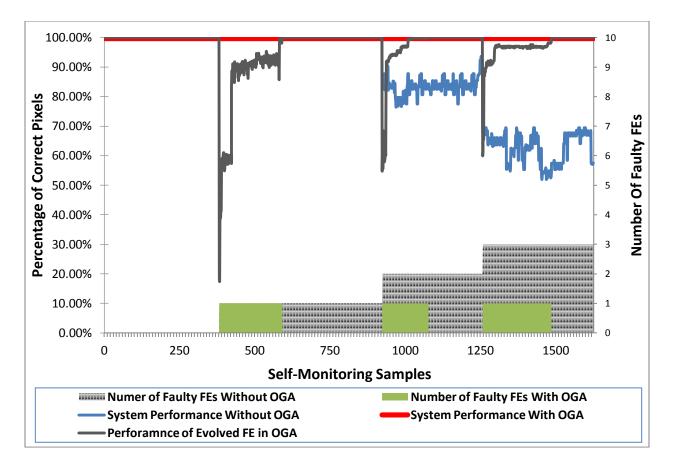

| 5.3. T  | The Relationship between RARS and the OGA                    | 94 |

| CHAPTER | R 6: AVAILABILITY, AREA, AND POWER EVALUATION METRCIS        | 97 |

| 6.1. S  | Semi-Hypothetical Use Cases                                  | 98 |

| 6.1.1.      | Soft-Fault Rate                                        | 99  |

|-------------|--------------------------------------------------------|-----|

| 6.1.2.      | Soft-Fault Repair Rate                                 | 99  |

| 6.1.3.      | Hard-Fault Rate                                        | 100 |

| 6.1.4.      | Hard-Fault Repair Rate                                 | 100 |

| 6.2. Ava    | ilability Analysis Using Markov Models                 |     |

| 6.2.1.      | Markov Configuration                                   | 105 |

| 6.2.2.      | Availability Evaluation Metric Results                 | 106 |

| 6.3. Area   | a and Power Comparison to industry-standard Techniques | 116 |

| 6.3.1.      | Experimental Setup                                     | 118 |

| 6.3.2.      | Experimental Results                                   | 123 |

| CHAPTER 7:  | CONCLUSION                                             | 136 |

| 7.1. Tecl   | hnical Summary                                         | 136 |

| 7.2. Futu   | ure Work                                               | 138 |

| APPENDIX: 0 | COMMUNICATION PROTOCOL MESSAGES                        | 140 |

| REFERENCE   | ES                                                     | 150 |

# LIST OF FIGURES

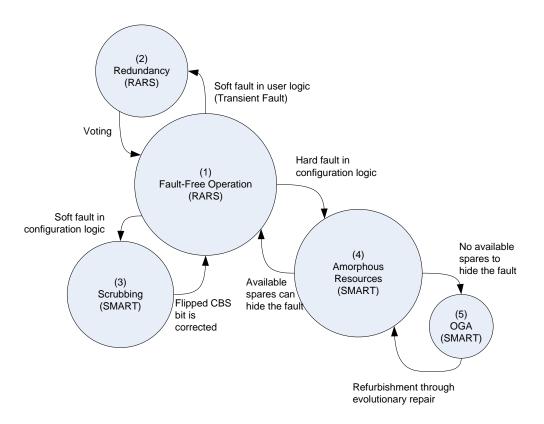

| Figure 1: High-level Operational View of SMART Repair Methods                       |

|-------------------------------------------------------------------------------------|

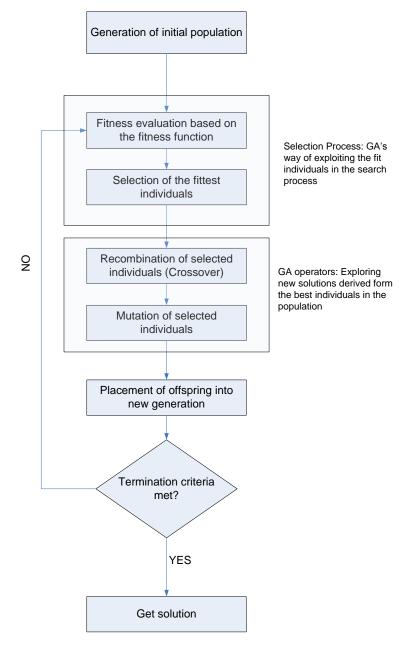

| Figure 2: Genetic Algorithm Flow Chart                                              |

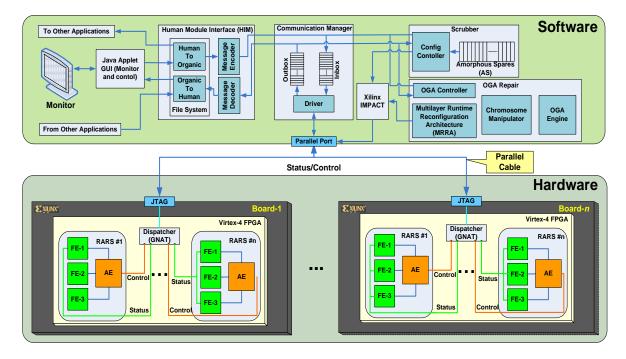

| Figure 3: SMART Top-level Hardware and Software Architecture                        |

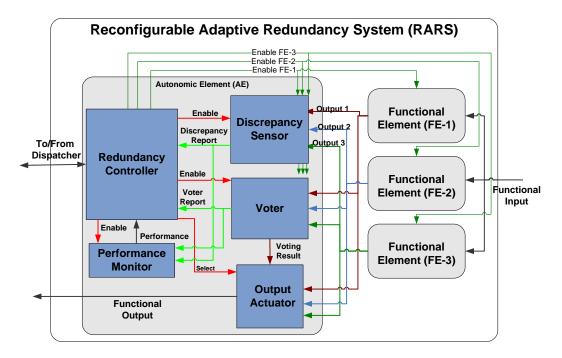

| Figure 4: Reconfigurable Adaptive Redundancy System (RARS)                          |

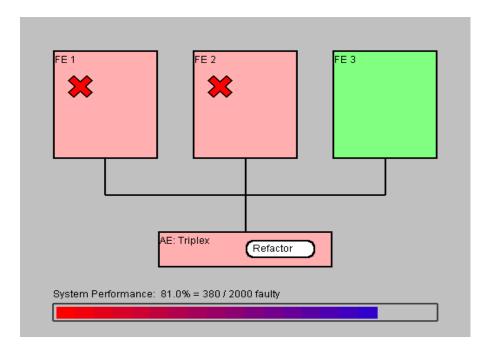

| Figure 5: Java Applet GUI Indicating Instantaneous RARS Status                      |

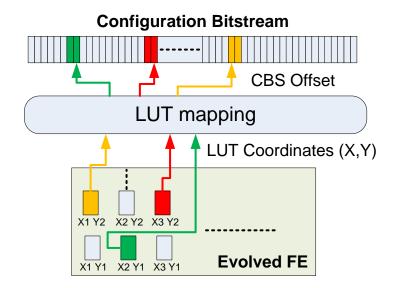

| Figure 6: Mapping from LUT Coordinates to CBS Offset Representation                 |

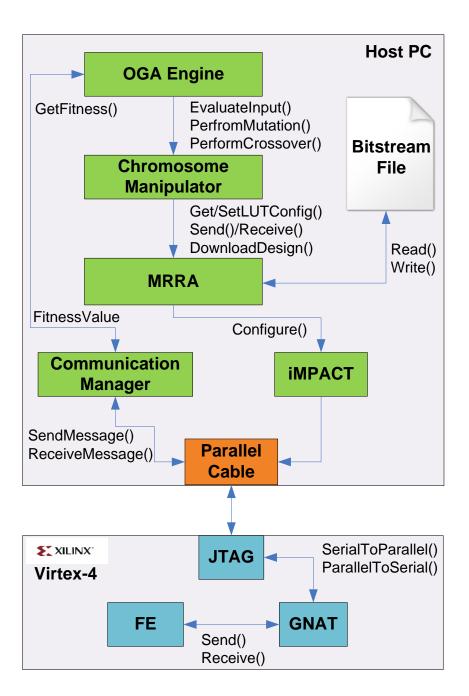

| Figure 7: OGA Intrinsic Evolution Platform                                          |

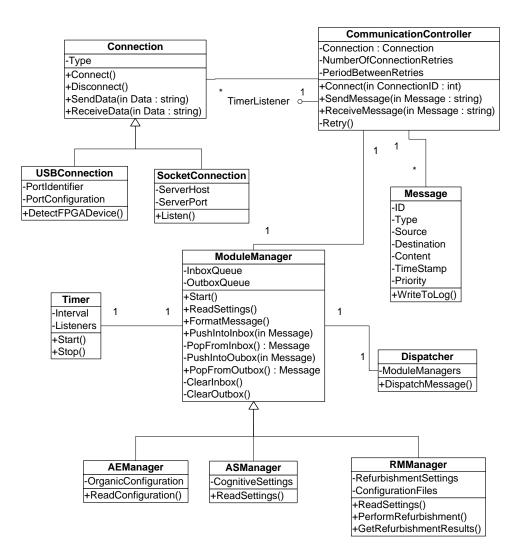

| Figure 8: Class Diagram of the Communication Module in the Software Layer71         |

| Figure 9: FPGA Layout for FE1, FE2, FE3, and RARS74                                 |

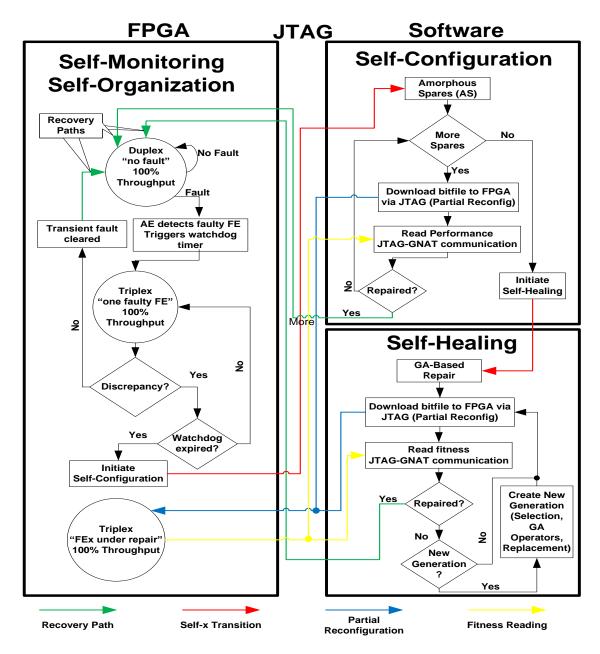

| Figure 10: System Self-x Properties Flow Diagram                                    |

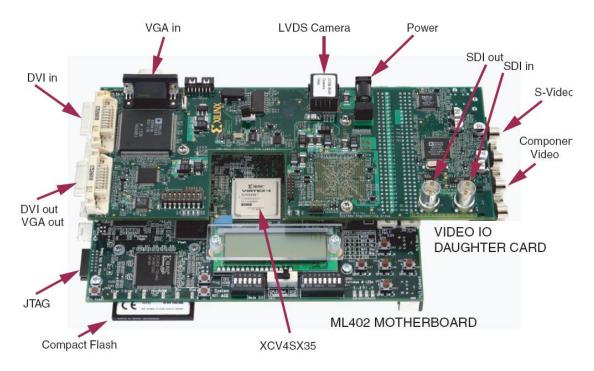

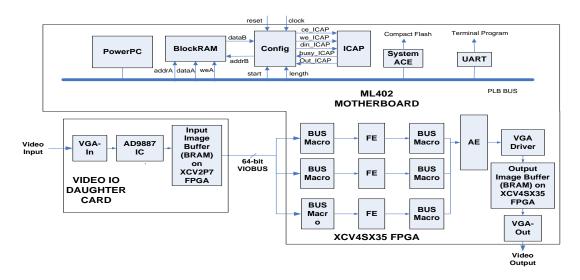

| Figure 11: Xilinx Dual-Layered Video Starter Kit                                    |

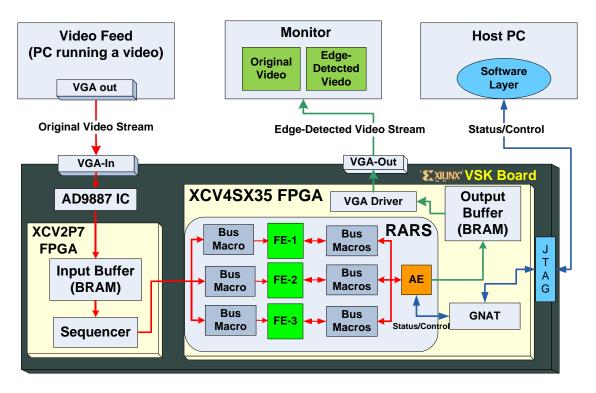

| Figure 12: SMART Use Case System Architecture                                       |

| Figure 13: Use Case Physical Design using Xilinx VSK Platform                       |

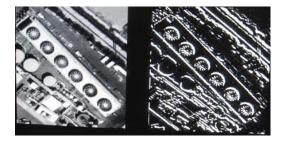

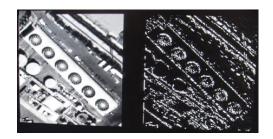

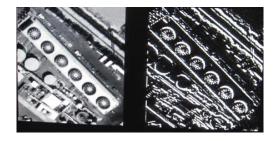

| Figure 14: Original and Edge-detected Images under Different RARS Configurations    |

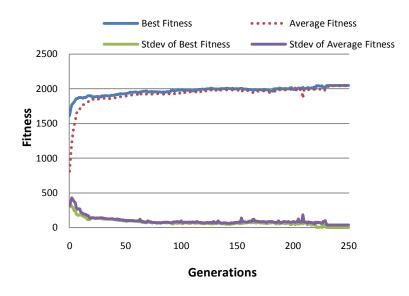

| Figure 15: OGA Best and Average Fitness Results                                     |

| Figure 16: Holistic Experiment Demonstrating the Interaction between RARS and OGA96 |

| Figure 17: Markov State-Transition Diagram of RARS104                               |

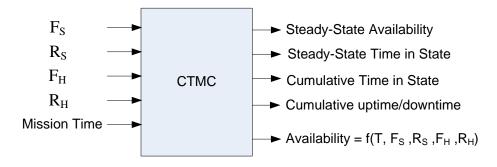

| Figure 18: Functional Model of the CTMC Experiments105                              |

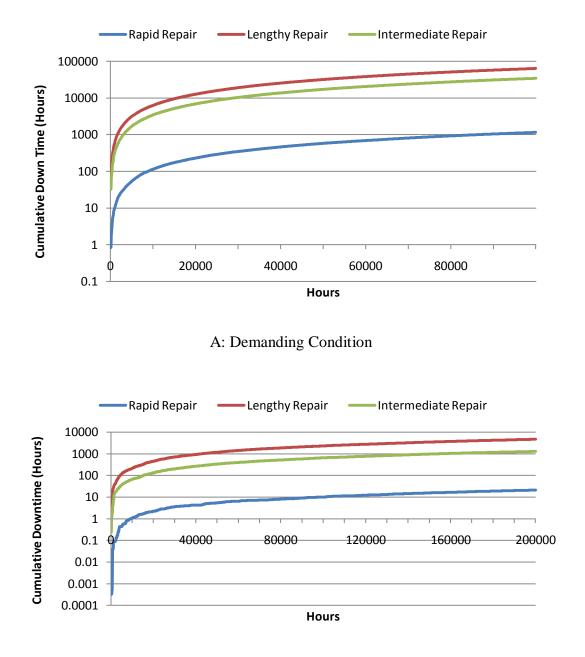

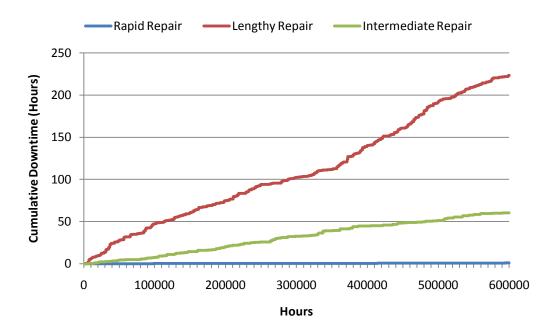

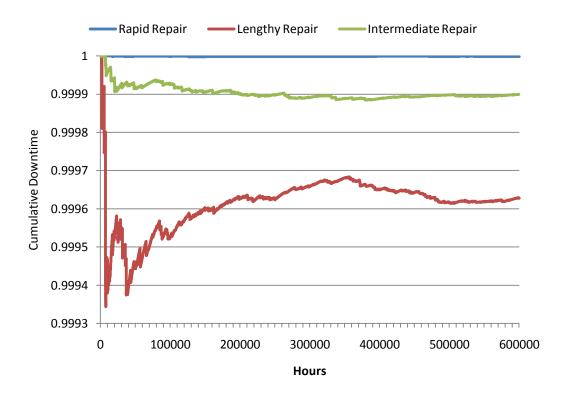

| Figure 19: Cumulative Downtime under the Nine Use Cases                             |

|-------------------------------------------------------------------------------------|

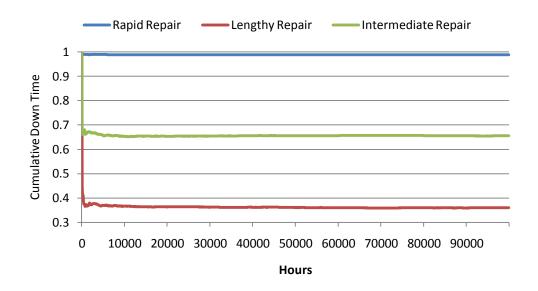

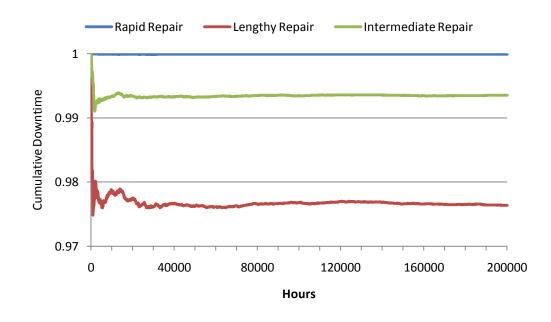

| Figure 20: Availability under the Nine Use Cases113                                 |

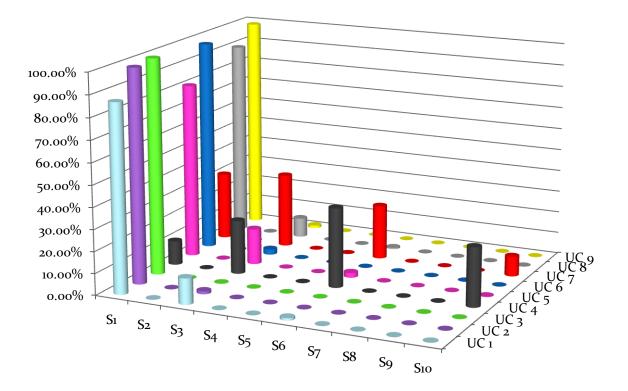

| Figure 21: Percentage of Time in Each State under the Nine Use Cases114             |

| Figure 22: Operational Phases Distribution under the Nine Use Cases                 |

| Figure 23: Component Differences between RARS and TMR117                            |

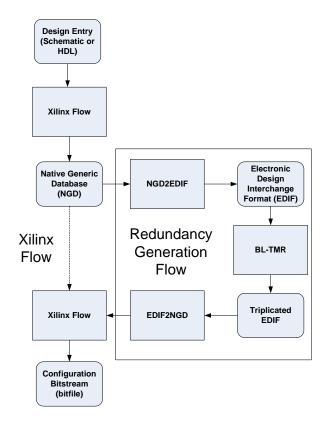

| Figure 24: Custom TMR-Insertion Flow Based on Integrated BL-TMR and Xilinx Flows120 |

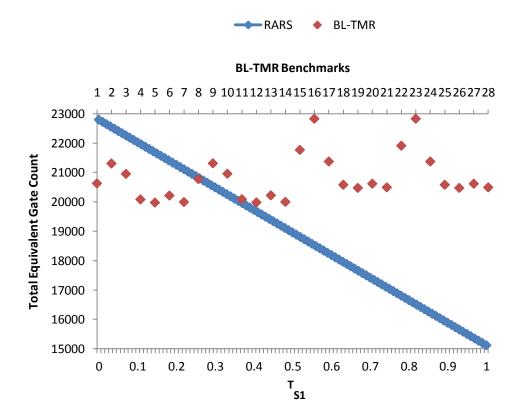

| Figure 25: RARS Area Overhead Relative to Twenty Eight Benchmarks                   |

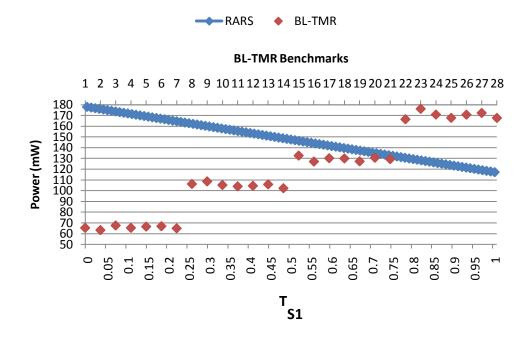

| Figure 26: RARS Power Overhead Relative to Twenty Eight Benchmarks                  |

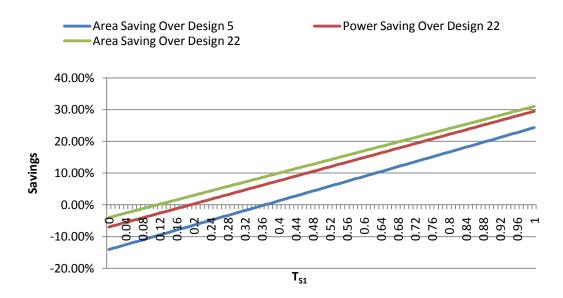

| Figure 27: RARS Area and Power Savings Relative to the Top Two Benchmarks           |

# LIST OF TABLES

| Table 1: Mission-Critical Space Applications Employing FPGA Devices                      | 17   |

|------------------------------------------------------------------------------------------|------|

| Table 2: Comparison between SMART and Other Prominent Fault-Tolerance Approaches         | 23   |

| Table 3: Successful Applications of IGA                                                  | 35   |

| Table 4: System Goals, Motivations, and Impacts                                          | 36   |

| Table 5: System Modules Implementation Details                                           | 43   |

| Table 6: Possible Values of the Voter Report                                             | 50   |

| Table 7: DIP Switch Assignment in RARS Prototype                                         | 83   |

| Table 8: LED Assignment in RARS Prototype                                                | 83   |

| Table 9: Fitness and Timing Information for Twenty GA Runs                               | 90   |

| Table 10: OGA Parameters used in Experiments                                             | 91   |

| Table 11: Comparison between SMART and Other Edge Detection Evolution Techniques         | 93   |

| Table 12: OGA Results for Various Numbers of Hard Faults                                 | .101 |

| Table 13: Fault and Repair Values of the Nine Use Cases                                  | 102  |

| Table 14: Average of Cumulative Time in State for the Nine Use Cases                     | 107  |

| Table 15: Standard Error (alpha=0.05) of Cumulative Time in State for the Nine Use Cases | .107 |

| Table 16: Overhead Analysis Quantities Definition                                        | 117  |

| Table 17: 28 BL-TMR Triplicated Edge Detector Benchmarks                                 | 124  |

| Table 18: Area Results of the Twenty Eight Benchmarks                                | 125 |

|--------------------------------------------------------------------------------------|-----|

| Table 19: Area Results of RARS Sub-Modules                                           | 126 |

| Table 20: RARS Area Savings over Benchamrk Five for Different T <sub>S1</sub> Values | 126 |

| Table 21: Power Results (in mWatt) for the Twenty Eight Benchmarks                   | 128 |

| Table 22: Power Results for RARS Sub-Modules                                         | 129 |

| Table 23: RARS Power Savings over Design Twenty Two for Different TS1 Values         | 130 |

| Table 24: Combining Availability, Area, and Power Results                            | 135 |

# **CHAPTER 1: INTRODUCTION**

In this chapter, the significance of the problem will be defined and a solution framework will be presented. Moreover, the contributions of the dissertation will be highlighted, emphasizing the innovation and novelty in SMART as a fault-tolerance technique targeting reconfigurable devices in mission-critical applications.

### 1.1. Need for Autonomous Repair in Mission Critical Applications

Current high-performance processing systems frequently consist of heterogeneous processor cores or subsystems that depend on one another in nontrivial ways. Each subsystem is itself a multi-component system with diverse capabilities. The organization of these subsystems is typically static; it is determined with great care at design time and optimized for a particular mode of operation. This design strategy is appropriate for systems that are accessible for repair when their components fail. However, systems which are unreachable once deployed present a different set of challenges. In these systems, the failure of a single component may result in large-scale inefficiency or even complete mission failure.

Therefore, electronic systems operating in demanding environments require increased capability for autonomous fault tolerance and self-adaptation, especially as system complexities and interdependencies increase. Hence, the goal of *Organic Computing (OC)* techniques [1, 2] is to create systems capable of adaptive and fault-tolerant behaviors. The OC paradigm is compatible with biologically-inspired computing concepts that emphasize the so-called "self-x properties"

which emerge at the system-level and represent life-like properties such as self-configuration, self-reorganization, and self-healing [2, 3]. These properties must be maintained in an autonomous fashion yet be sufficiently constrained to avoid the emergence of undesirable behaviors.

Complex digital systems that are able to operate autonomously for long periods of time without external repair are essential for reducing the risk involved in mission-critical applications, such as space, deep-sea, manned and unmanned avionic missions, and deployments to remote or perilous terrestrial areas. For instance, a military or commercial satellite that cannot recover from a hardware failure becomes orbiting space junk or must be replaced, thereby incurring great economic costs and negative societal impact. In contrast, a sustainable self-aware satellite would offer increased dependability and extended lifetime. Organic computing is one of the most promising approaches to realizing such dependable systems.

### 1.2. Advantages of Reconfigurable Logic to Support Fault-Tolerance

The OC paradigm is seldom tied to a particular platform or implementation, which makes it relatively broad in its impact and unrestricted with respect to any specific research or industrial context. Nonetheless, the immense flexibility of reconfigurable hardware devices makes them especially suited to hosting OC applications [4]. The fact that SRAM-based FPGAs can be dynamically reconfigured has made them a popular hardware platform for numerous OC systems [4, 5].

Several external environmental or internally-driven performance demands may require a change in the configuration of a multi-component system to maintain functionality and throughput throughout an extended mission [6]. For instance, a fault may occur in an individual component, which must then be replaced, refurbished to some degree, or otherwise bypassed. Although one could hypothesize that routine hardware failures would be a likely trigger for configuration change, other mission-level considerations, such as a storage device reaching its capacity or the environment deviating from expectation, could be handled similarly. In either case, existing modules must be reconfigured; SRAM-based FPGA devices facilitate this flexibility by enabling dynamic device reconfiguration.

SRAM FPGAs represent ideal platforms for hosting organic computing hardware implementations due to their ability to reconfigure a system at any time to adapt to events that necessitate a change in the hardware, such as fault-occurrence or changes in mission requirements. The following reasons justify our selection of reconfigurable devices to host SMART:

1. Reconfigurable hardware allows fast, in situ reconfiguration of a hardware device. This characteristic has been utilized in SMART to circumvent faulty resources in the hardware by maintaining collections of *Amorphous Spares (AS)*, which are pre-seeded bitstream files that represent the same functionality of the circuit, though with different implementations or area constraints. Once errors are detected, these AS can be downloaded and tested individually to determine if any of them do not make use of the

faulty resource on the fabric. This approach is not possible on *Application Specific Integrated Circuits (ASIC)* due to the fixed nature of their hardware fabric.

- 2. Dynamic PR allows for the reconfiguration of faulty components while the system is kept online. This method can be coupled with hardware redundancy such that the repair process can operate on the faulty part of the system, while other redundant parts continue in a normal operation mode to drive the system output. SMART employs this technique to provide efficient repair so that the system can continue to provide the highest possible performance while being repaired.

- 3. Time-multiplexing of different applications on the same FPGA greatly benefits organic systems, which normally require adaptive and flexible design practices, such as changing the functionality of the hardware during certain stages of the mission to support another application or other operational modes. Different bitstreams for different applications can be stored and downloaded whenever the mission demands their use.

- 4. Reconfiguration capability facilitates organic repair through evolutionary algorithms. Reconfigurability allows for testing the fitness of individuals on the hardware, and also enables direct evolution of the most compact presentation of the circuit, which is the *Configuration Bit Stream (CBS)* that stores the logic and routing configuration of the user circuit. Both Intrinsic fitness evaluation and direct CBS evolution are not possible in ASIC because the hardware logic and routing cannot be changed after fabrication. The

OGA that we implement in this work has many properties that are made possible due to the reconfigurability of the underlying hardware, as discussed in Section 4.2.3

- 5. Reconfigurable systems based on FPGAs also have the option to integrate flexible softcore processors such as Microblaze on the same fabric with the application hardware, which provides an opportunity to implement a complete SoC application. High-end FPGA boards are also equipped with embedded cores such as PowerPC that interface with the FPGA and control its reconfigurability via the *Internal Configuration Access Port (ICAP)*.

- 6. A multitude of computing and memory resources such as High-Speed *Digital Signal Processing (DSP)* blocks operating at high speeds, block RAMs, FIFOs, and other builtin hardware logic are available on today's FPGAs to provide many options for a broad range of applications and accelerated implementations of commonly used image processing, arithmetic, communication, and encryption applications

- 7. Reconfigurable logic provides the option to change the clock frequency for a select part of the fabric at run time through the use of the built-in *Digital Clock Manager (DCM)* block. Therefore, an OC system can optimize the power usage for an application to meet mission requirements.

Despite of all the aforementioned advantages, using FPGA devices rather than their ASIC counterparts in mission-critical applications is a double-edged sword. On the one hand, they allow the support of self-x capabilities through reconfiguration. On the other hand, such

capabilities can introduce new fault vulnerabilities to the hardware. Transient faults, which commonly occur as a *Single Event Upset (SEU)* [7] are a primary source of concern when deploying SRAM-based devices in mission-critical applications such as space applications [8]. SEUs can occur when a charged particle impacts the silicon substrate with enough energy to incur either a transient pulse in a combinational logic or a state flip in a sequential circuit. The former is only articulated if a state storage component, such as a Flip-Flop, is affected by the transient signal. Hence, the effect of SEU on combinational logic in ASICs could vanish without any repairs. On the other hand, SEUs hitting memory cells are more likely to cause damage because they flip the state of a stored bit, which affects the system until the relevant Flip-Flop is loaded with a new correct value.

In SRAM-based FPGAs, where even the combinational logic is implemented using SRAM *Look-Up Tables (LUTs)*, SEUs gain amplified importance as every SEU is a state-flip that can affect both the sequential and the combinational logic. To this end, space-qualified versions of SRAM-based FPGAs are commercially available for mitigating SEUs at the circuit level such as Xilinx's QPro [6], Indeed, a new field of research that targets fault tolerance in reconfigurable platforms has emerged [6] to take advantage of the inherent reconfigurability of FPGAs. In conjunction with the use of high reliability components, mission-critical applications can benefit from PR to survive the various sources of failures that might affect reconfigurable resources.

### 1.3. Contributions of the Dissertation

In this dissertation, we introduce SMART, a novel fault-tolerance technique exhibiting many advantages over the manufacturer's current standardized fault handling method, which is the *Triple Modular Redundancy (TMR)* Technique. SMART provides *Adaptive Modular Redundancy (AMR)*, in contrast to the fixed one in TMR, by exploiting the reconfigurability property of the FPGA devices [9]. Moreover, SMART provides handling for hard-faults which are seldom considered in self-repair techniques due to their supposed rareness. We demonstrate via standard evaluation metrics and actual reported fault rates that hard-fault repair is needed to provide sustainable mission operations in harsh environments. Moreover, not just that SMART provides improved availability; it does it in a resource-aware fashion by optimizing energy consumption and area usage.

#### 1.3.1. Design and Implementation of SMART

In this work, we present the design and implementation of SMART, a two-layered sustainable autonomic architecture for fault handling. The autonomous hardware layer is implemented on a Virtex-4 Xilinx XC4VSX35 FPGA device [10], while the software layer is intended to be on a PowerPC embedded core with ICAP interface to the FPGA device to download different CBSs for repair purposes. In this work, in order to facilitate testing and verification, the software layer resides on a host PC that is connected to the FPGA via a Xilinx parallel cable IV. SMART is inspired by the OC paradigm, and thus the emergence of self-x properties is observed at the system level after assembling the individual parts into a single, integrated, fault-tolerant system.

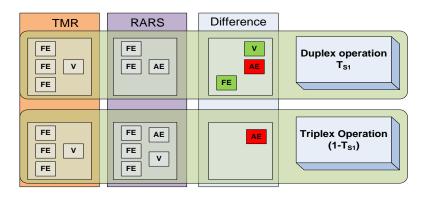

The hardware layer implements a decentralized observer/controller processing loop to adjust the configuration of the system based on real-time mission information. It accomplishes this task using a novel general-purpose redundancy scheme called RARS [11] which does not have a predetermined number of redundant modules like other fixed redundancy schemes commonly found in the literature such as Duplex, TMR, and pair-and-spare. [12, 13]. Instead, RARS can reconfigure its components at run-time to provide the appropriate level of redundancy that matches the mission status. The distributed controller function in RARS, which is called the *Autonomic Element (AE)*, monitors the status of the redundant parts that implement the user application, called the *Functional Elements (FEs)*, and collects the reports from various sensors to make decisions about which configuration to select. Having multiple RARS modules facilitates the decentralization of the organic layer while reducing single points of failure.

RARS is a resource-conservative adaptive redundancy architecture that is only reconfigured to a high power/area configuration when multiple instances of the FE are needed to identify, mask, or repair faults. Other approaches like TMR run in triplex mode even when faults are not present, consuming three times the simplex configuration resources only to provide fault-tolerance during brief intervals of the mission lifetime during which the system is subject to faults. RARS saving benefits will be shown analytically and experimentally in Chapter 6.

Still, the fault-tolerance of RARS is restricted by the limited capacity of the available hardware to support alternative routing and/or logic for faulty parts. Therefore, a monitoring and refurbishment layer that resides above the hardware layer serves two purposes. The first is to collect the hardware status reports and render them into a human-readable format so that system operators can monitor the deployed system and interact with it. The second is to provide active repair in the event of faults, either via scrubbing [13], which involves rewriting the configuration memory with a fault-free CBS to correct any SEU occurrences in the configuration logic, or via a dynamic refurbishment process for permanent faults using *Evolvable Hardware (EHW)* approaches [14] . The evolutionary approach employed in this work is a novel *Genetic Algorithm (GA)* that implements design practices suiting the organic nature of the system and thus is referred to as an *Organic GA (OGA)*. The software layer reads the performance and status of RARS and triggers the refurbishment procedures whenever the redundancy degree of RARS is not adequate to mask the faults.

The two layers are connected via Xilinx Parallel Cable that connects between a standard *Joint Test Action Group (JTAG)* [15] port on the FPGA and the parallel port on the host PC. On the FPGA, the JTAG communicates with RARS via the *General-Purpose Native JTAG Tester (GNAT)* [15] platform. The messages themselves are communicated using a special communication protocol that was designed specifically for this system. This communication link carries messages between the two layers as part of the fault-tolerance algorithm and also transmits the CBS to reconfigure parts of the system as needed.

Dynamic PR is adopted to improve two aspects of the organic repair. First, it significantly reduces the configuration time as compared to the full bitstream configuration approach due to the small size of the bitstream. Second, it allows the system to remain online while its faulty parts are being reconfigured; this helps increase the availability of the system by enabling it to maintain functionality even during repair. Dynamic PR is used in two stages of the repair cycle.

It is first used in the scrubbing stage when the AS are repetitively configured on the FPGA searching for a spare that exclude the faulty resource, and second, it is used by the OGA when candidate solutions are reconfigured on the FPGA for fitness evaluation.

In this work, we implement the well-known Sobel edge detection [16] application on the hardware layer to illustrate the organic self-healing, self-configuring, and self-monitoring capabilities of RARS. In addition, we implement the software layer and connect it to the circuit on the FPGA through the JTAG port. This layer is shown to successfully monitor and supervise the organic hardware layer and also performs evolutionary refurbishment of faulty modules.

After combining all modules into one integrated fault-tolerant platform, we scrutinized the system behavior while processing a real-time video stream under various fault scenarios. The hardware layer demonstrated emergent self-monitoring and self-reorganization properties that allowed the system to sustain even in the presence of successive faults. When the number of faults exceeded the capabilities of the hardware layer, the higher-level software layer augmented the response through self-reconfiguration and self-healing.

### 1.3.2. Autonomous Fault-Tolerance Technique to Improve Availability

Figure 1 depicts the high-level view of SMART's repair methods and the various events that trigger their executions. The central state of SMART operation is the fault-free operation (1) that requires only RARS's self-monitoring techniques to detect the occurrence of faults. An SEU can impact the FPGA resources and cause a single bit flip in one of the LUTs. This LUT may fall

either on the data path of the application, i.e., a user register that stores an intermediate calculation value, or on the logic path, i.e., an LUT that is programmed to implement the intended circuit functionality. SEUs that affect LUTs in the user logic can be overwritten by subsequent operations without any repair interventions. This type of fault is classified as transient, and normally fades away in the regular execution cycle. The transient effect can be masked with redundancy techniques (2) until the fault is corrected.

However, if the soft fault affects an LUT in the reconfigurable logic, then the bit flip will remain manifested until the unlikely event of another SEU impacting the exact same location. A bit flip in the logic path can be more harmful to the application because it changes the truth-table content of the affected LUT and thus alters the behavior of the circuit. This type of SEUs cannot be ameliorated in subsequent operations because the affected element is not written by the user application; thus, it must be explicitly re-written by reloading the correct CBS via scrubbing (3).

Next, consider if radiation leads to pathways for electro-migration and accelerated aging effects [17]. This type of *Local Permanent Damage (LPD)* can be modeled as a stuck-at fault at one of the LUT inputs. Unfortunately, scrubbing techniques that rewrite the CBS contents will at best give up after a number of retries or at worst may usurp the mission, taking the device offline to repeatedly attempt to overwrite a permanent fault. In that case, a permanent fault handling technique is required to circumvent the stuck-at faulty resource and thus repair the user application.

The self-configuration of spares via AS (4), aims to avoid the faulty resource by consecutively reconfiguring the faulty FE with design-time pre-seeded bitfiles, each of which exclusively avoids a set of LUTs in the physical FE area. By doing so, SMART searches the set of spares for one spare that can hide the fault by not using the broken LUT. Carrying spares is a common technique for fault-tolerance due to its simplicity and quickness, it is limited though to the number of carried spares, and cannot actually adapt at run-time to handle fault-scenarios that were not accounted for at design-time when the spares where configured.

As a remedy, SMART adds one last-resort repair mechanism that is invoked when all other techniques fail to repair faults. This technique is the evolutionary OGA (5) repair that is not restricted by the number of spares or any other design-time considerations. Instead, it can heuristically search for alternative circuits that can bypass the faulty resource and thus produce the expected output. Such technique can sometimes be slow or unpredictable, but the fact that it is delayed to the very end of the repair cycle makes it a much better alternative to conceding to downgraded level of operation.

Figure 1: High-level Operational View of SMART Repair Methods

### 1.3.3. Evaluating Self-Regulation of Availability, Area, and Energy

The first evaluation metric that we perform is reliability assessment of SMART compared to conventional TMR and scrubbing techniques that choose to ignore hard faults handling due to their rareness. To accomplish this, we model RARS as a *Continuous-time Markov Chain (CTMC)*, providing transition probabilities of soft and hard fault rates based on publically available fault-measurement data, and soft and hard repair rates based on experimental results of SMART prototype. We present a full factorial experiment with nine levels based on three levels of each MTTF and MTTR of the hard faults, where each experiments consists of Monte Carlo simulations for the fault and repair levels to calculate various reliability and availability metrics

that can help shedding light on the significance of hard fault repair in fault-tolerance systems. Details on availability analysis using CTMC can be found in section 6.2.2.

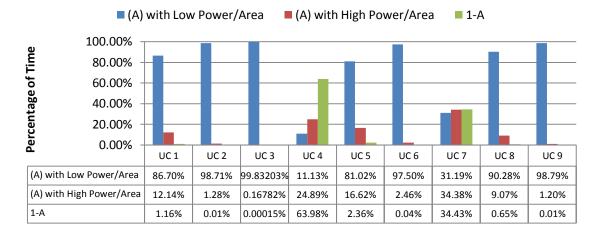

After we experimentally established the benefits of SMART on the availability of missioncritical systems in space applications, we shifted the focus to assessing SMART's power and area considerations as a real engineering platform. For that, we used the standard *BYU-LANL Triple Modular Redundancy (BL-TMR)* [18] toolset to create triplicated designs of the image processing Sobel edge detector use case that we evaluated SMART against. The BL-TMR tool is a Java-based project that relies on the platform-independent *Electronic Design Interchange Format (EDIF)* [18] files to automatically insert redundancy, such as duplication and triplication, into digital designs. We chose four voter insertion options times seven voter insertion algorithms to design twenty eight BL-TMR triplicated edge detectors benchmarks. We used Xilinx mapping reports to extract the area overhead of each benchmark, and *Xilinx Power Analyzer (XPA)* [19] tool to calculate the dynamic power of the benchmarks. We then compared the twenty eight benchmarks to RARS in term of power and area to demonstrate the benefits of utilizing PR in FPGA-based fault-tolerance applications. The experimental setup and results are documented in section 6.3.2.

## **CHAPTER 2: RELATED WORK**

In this chapter, we present literature survey for previous works of the dissertation. The previous work is classified into technology related work and application related work, where the former deals with reconfigurable devices and their susceptibility to faults, while the latter focuses on the various fault-tolerance methods and their applications.

#### 2.1. Device Technology Related Work

### 2.1.1. Role of Reconfigurable Devices in Space Mission-Critical Applications

Hardware devices are commonly viewed as fixed-functionality devices as they are rendered for specific application at fabrication time and cannot be changed after that. However, the main benefit of FPGA devices is reconfigurability, as the fabrication will only create a programmable platform that can be configured -and often reconfigured- by the end user, to realize various functionalities at runtime.

FPGAs are seas of programmable logic blocks that are highly interconnected through other programmable hierarchal communication switches. FPGAs can be made of anti-fuse technology, which allows single device programming, or SRAM cells that allows any number of device programming operations [6]. The focus of this dissertation is on SRAM-FPGAs because SMART relies on the reconfigurability feature to realize fault-tolerance with reduced power and area overhead.

SRAM-FPGA devices allow both logic and interconnect to be programmed by downloading a CBS that represents the desired circuit functionality. The generation of the CBS is normally automated through the usage of software tools, like Xilinx ISE pack [20], that read the design in schematic or *Hardware Definition Languages (HDL)* formats, and then transform the design into native bitfiles to program the target devices. Thus, FPGAs are considered a suitable platform for prototyping because they can be instantly programmed with the desired hardware functionality without going through the complicated, lengthy, process of fabrication in ASICs.

Therefore, FPGA Devices have been widely used in space mission-critical applications for different purposes. For example, *Europa* mission [21] designers intend to use FPGA devices as a prototyping platform during the development phase, then based on a specially-designed flow, the prototype will be implemented on radiation-hardened ASIC devices for the actual mission deployment. Other missions will use FPGA devices in the actual deployment, whereas others are intended to test SRAM-FPGA resilience to SEU's. Table 1 shows a list of actual space missions that utilize FPGAs in their operations, along with the deployment timeframe, and the intended use of the FPGAs. The various mission reported in the table demonstrate the important role of FPGA devices in such domain, and thus justify the direction toward fault-tolerance in FPGA in research and industry.

| Satellite Name                                                                     | Year<br>Deployed | Application                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FedSat (Australia -<br>CRCSS) [22]                                                 | 2002             | Remote Sensing: Control Logic, Classifier, Predictor, Encoder.<br>Contains Actel FPGA for pre-filtering, Xilinx FPGA for data<br>acquisition and synchronizations, another Xilinx FPGA device<br>for data decoding. |

| Cibola (USA-Los<br>Alamos) [23]                                                    | 2007             | Nine Xilinx Virtex FPGA devices used for sensor-processing<br>and SEU studies (soft faults monitoring and mitigation)                                                                                               |

| SmartSat-1 (Japan –<br>NICT) [24]                                                  | 2008             | Seven XC2VP4 Xilinx FPGAs implementing<br>Modulation/demodulation function (2 kbps -2 Mbps)                                                                                                                         |

| Space-Based<br>Reconfigurable<br>Supercomputer [25]                                | Future           | Xilinx Virtex-4, Atmel AT697 radiation-hardened, SPARC processor. Supercomputers that can achieve 1,000 GOPs, weigh 40 pounds, and consume only 80 watts                                                            |

| Venus Express [26]                                                                 | 2005-<br>2012    | Two radiation-hardened Xilinx Virtex-1 FPGA devices to implement <i>Venus Monitoring Camera (VMC)</i> .                                                                                                             |

| NASA New Dawn [26]                                                                 | 2007-<br>2015    | Improved on Framing Cameras (VMC) that was used in Venus                                                                                                                                                            |

| Mars Rover (JPL) [27]                                                              | Many             | Xilinx Virtex FPGA has been used in DC motor controller in the rover                                                                                                                                                |

| Europa [21]                                                                        | 2020-<br>2029    | FPGAs are used in prototyping, then the final design will be<br>implemented on Rad-Hard ASIC devices for the actual mission                                                                                         |

| ARTEMIS<br>Reconfigurable Payload<br>Processor (Responsive<br>Space Missions) [28] | Many             | RA-RCC (Reconfigurable Computers) using 3 Virtex-4<br>(V4LX160) FPGAs                                                                                                                                               |

Table 1: Mission-Critical Space Applications Employing FPGA Devices

## 2.1.2. Failure Modes and Their Effects

Using FPGA devices comes at the expense of increased fault rate compared to ASIC-based devices. In the space environment, SRAM-based FPGAs can be affected by either radiation-induced or aging-related faults [29]. Radiation-induced faults can be either non-destructive (soft) or destructive (hard). Aging Faults on the other hand are almost always destructive, which means that the fault cannot be recovered by rewriting the CBS. Regardless of the fault types, the application should be prepared to autonomously recover from the faults due to the limited human intervention in space missions. This section will provide taxonomy of the various fault types that can affect FPGA devices in space, and the common methods of dealing with them.

Radiation can cause one of the following two failure modes in FPFA devices [30]:

- 1- *Single Event Effect (SEE)*: Effect caused by *single* energetic sub-atomic particle strike, this is a random event that does not directly depend on cumulative effects. SEEs can result in two type of faults:

- a. Non-destructive SEU: This is a state-flip of an SRAM cell that is caused by the SEE [7]. It is non-destructive in the sense that the flipped bit can be restored by rewriting the cell's content with the correct value. SEUs can happen in the configuration logic or the user logic. The configuration logic is what defines the FPGA circuit behavior; the only way to correct SEUs in this logic is to rewrite the flipped cell with a new value via scrubbing. However, SEUs in the user logic fall on the datapath, and thus can be corrected by subsequent writes to the same user register.

- b. Destructive *Single Event Latch-up (SEL)*: Occurs when an energetic charged particle causes excessive supply power to destruct the memory cell [30]. This destruction is permanent and cannot be restored by rewriting the CBS like in the previous SEU case.

- 2- *Total Ionizing Dose (TID)*: Cumulative damage caused by protons and electrons hitting the silicon substrate for long times. TIDs are almost always destructive.

To Summarize, radiation can cause destructive faults through TID faults or SEEs that get manifested as SELs. More commonly, radiation will cause non-destructive SEEs in the forms of SEUs.

Numerous fault-tolerance systems in the literature have neglected permanent fault handling in FPGA devices [31]. The reason behind this choice is that many resources in research and industry have claimed that Xilinx SRAM-based FPGAs are immune to radiation-induced destructive hard faults. No SEL was reported during experiments when SRAM-based FPGAs were exposed to the maximum tested *Linear Energy Transfer (LET)* of tens of MeV cm<sup>2</sup>/mg [29]. Xilinx Virtex family was also found immune against TID effect of up to 300 krad in [32]. Moreover, The introduction of epitaxial CMOS fabrication process in Virtex devices resulted in TID immunity of >100 krad and SEL immunity of LET > 120 MeV cm<sup>2</sup>/mg [33].

Therefore, conventional fault-tolerance approaches targeting SRAM-based FPGA devices in space applications have disregarded hard-faults tolerance [31]. Instead, they focused on mitigating SEU faults in the data path using redundancy techniques, such as TMR, to mask the transient effect of the user registers bit flips [34], and implementing scrubbing techniques to overwrite SEUs in the configuration logic [35]. Xilinx devices have shown high tolerance to SEL and TID, thus SEU remains as the main concern in space-mission that use FPGA devices [33].

Nonetheless, in this work, we contradict the aforementioned mainstream hypothesis by asserting that permanent faults cannot be ignored in mission-critical applications because of the following reasons:

- 1. With the continuous effort to shrink the feature size in VLSI devices, the impact of agingrelated (wear out) faults such as *Time-Dependent Dielectric Breakdown (TDDB)* will significantly increase to levels that cannot be ignored [36]. TDDB depends on the operating temperature of the device, and the gate oxide thickness that shrinks with smaller process technologies. The charge trapped in the thin oxide layer keeps increasing until it reaches the threshold of breakdown; this effect is imminent for aggressively scaled technologies operating in thermally stressful environments. The resulting fault is destructive, meaning that the SRAM cell cannot be reconfigured to amend the fault effect.

- 2. Local Permanent Damage (LPD) is reported by [17] due to SELs or SEUs that cannot be corrected without system reset. This type of LPDs is manifested as hard faults in systems that cannot tolerate full system restart.

- Radiation testing is not guaranteed to exactly replicate space environment. Also no FPGA has been tested for more than 15 years, whereas space mission can go for more than that [17]

- Xilinx publicly reports that TDDB can start to happen in *as little as 3 years* in an XC3S 4000/5000 90-nm SRAM-based FPGA devices under a temperature of 125C [37].

- 5. Recently published work reported TDDB impacting 10% of total LUTs every year [36] in aggressive thermal conditions, based on Xilinx data referenced above. Other recently

published work reported TDDB MTTF of 476 days for a 2206-slice circuit on 150nm technology [29].

Therefore, we believe that it is not the best engineering practice to blindly ignore hard faults especially in multi-million mission-critical applications that needs to be equipped with inherent tolerance to any type of destructive events. Thus, we present the design and implementation of a generic autonomous fault-tolerance system that can handle both soft and hard faults, followed by evaluation metrics to demonstrate the benefits of such system compared to conventional TMR and scrubbing systems, in term of availability, power, and area

### 2.2. Application Related Work

This section surveys previous researches that present various fault-tolerance methods, successful prototypes and implementations of OC systems, and the application of GA as a repair method.

#### 2.2.1. Fault Tolerance in Reconfigurable Devices

FPGAs are popular platforms for reconfigurable computing applications especially pertaining to the field of embedded systems [38]. Run-time partial reconfiguration has many advantages, such as time-multiplexing different functionality designs to save power and resources without losing the basic functionality of the application [39, 40], and supporting adaptive architectures that scales based on resources availability and mission requirements to achieve improved algorithm performance while reducing power consumption [41].

The ability to perform partial reconfiguration for local and remote system has opened new domains in fault-tolerant hardware designs, especially for space applications [6]. These applications are susceptible to faults due to the harsh operating environments along with difficult, if not impossible, human intervention. Thus, runtime partial reconfiguration has been successfully utilized to autonomously repair faulty systems, and compensate for the absence of human intervention.

One of the most common techniques for mitigating unwanted configuration memory changes is scrubbing [17, 42]. Scrubbing involves overwriting of the configuration memory at periodic intervals with a configuration that is known to be fault-free. Moreover, this process can be augmented by reading back the configuration memory and comparing it with a configuration that is known to be good to isolate the erroneous frame(s) so that they can be re-written using PR. Scrubbing techniques fail when the stored configuration is damaged or when the fault is caused by permanent hardware resource failures, in which case more elaborate repair techniques targeting permanent faults are needed, such as the evolutionary repair algorithm presented in [15] and in this work.

Table 2 presents a comparison between SMART and other prominent fault-tolerance techniques. All surveyed techniques, except conventional TMR, employ some form of fault recovery mechanism to restore the original fault-free system status. TMR is a passive technique which employs spatial voting to mask the faults. The area and power overhead for the TMR approach is three times the area and power overhead associated with a single module ( $O_{FE}$ ) plus the overhead associated with the voting logic ( $O_V$ ).

|                   |                                                                   | Fault Detection                        |                | <b>Resource</b> Coverage |                  |                                                    |

|-------------------|-------------------------------------------------------------------|----------------------------------------|----------------|--------------------------|------------------|----------------------------------------------------|

| Approach          | Fault Handling<br>Method                                          | Latency                                | Hard<br>faults | Logic                    | Comparator       | Power overhead<br>Area cost                        |

| TMR               | Spatial Voting                                                    | Negligible                             | No             | Yes                      | No               | $3*O_{FE} + O_V$                                   |

| Vigander<br>[14]  | Spatial voting and offline evolutionary refurbishment             | Negligible                             | No             | Yes                      | No               | $3*O_{FE} + O_V + O_{GA}$                          |

| Lach [43]         | Design-time fine<br>grain redundancy<br>based reconfiguration     | Not<br>addressed                       | No             | Yes                      | Not<br>addressed | Fault detection<br>mechanism is not<br>addressed   |

| STARS<br>[44]     | Online BIST                                                       | Depends<br>on<br>geometry<br>of device | Yes            | Yes                      | Yes              | O <sub>FE</sub> +<br>Reconfiguration<br>controller |

| Garvie [17]       | Spatial Voting and online (1+1) ES                                | Negligible                             | Yes            | Yes                      | No               | $3*O_{FE} + O_V + O_{GA}$                          |

| Keymeulen<br>[45] | Design-time<br>population based<br>fault insensitive<br>designs   | Not<br>addressed                       | No             | Yes                      | Not<br>addressed | Fault detection<br>mechanism is not<br>addressed   |

| SMART             | Adaptive<br>redundancy,<br>diversity-based<br>configurations, OGA | Negligible                             | Yes            | Yes                      | No               | Analyzed in Section<br>6.3                         |

Table 2: Comparison between SMART and Other Prominent Fault-Tolerance Approaches

Vigander [14] presents an offline genetic algorithm refurbishment technique to handle hard faults. All the modules are simulated with faults representing a worst-case scenario, and the evolution-based refurbishment is performed on all three modules for recovery. The overhead associated with the GA based repair is represented as  $O_{GA}$ . This cost can be used to include all GA based control mechanisms, and the spare resource allocated for the GA-based refurbishment.

Lach [43] on the other hand presents a technique based on design-time allocation of fine-grain spares at the *Configurable Logic Blocks* (CLB) level. One CLB is allocated as spare for a design-time defined group of CLBs, and multiple configurations are generated such that one fault can be tolerated in each group. Average Area overhead of the chosen benchmarks is 5.4%, which is

considerably less than the TMR. This scheme however does not include any fault detection mechanism.

STARS [44] employs run-time *Built-In Self Testing (BIST)* by roving across the FPGA fabric. This technique covers fault detection, isolation and repair with minimal application area overhead. Dynamic PR has also been used in this approach to facilitate downloading the tested regions onto the fabric. Still, the time to detect a fault can be quiet high and as much as 8.5M erroneous outputs may be produced before being able to detect the fault [46]. Further, the fault detection process employs continuous reconfiguration and thus incurs huge power overhead, and potentially causes performance degradation due to clock stoppage, even when the system is fault-free.

Garvie [17] employs spatial TMR for masking the fault and an evolutionary strategy to refurbish the identified faulty module. The power and area overhead of this technique can be essentially considered same as that of TMR. The work concludes that hard-fault tolerance is essential for fault-tolerance of FPGA devices in harsh-environment deployments.

Keymeulen [45] introduces an evolutionary-based method to generate a population of individuals at design time that are resilient to a set of predetermined type of faults according to the planned mission. This design-time process is tested by employing the design-time generated configurations to overcome the expected fault pattern at run-time. This scheme requires accommodating all possible faults at design-time.

# 2.2.2. Organic Computing Approaches

Related works in the literature have explored techniques useful for the development of an OC system from various theoretical and practical perspectives. A frequent focus among these has been the design of OC architectures and development methodologies for systems with the potential to exhibit increased reliability and sustainability.

For example, in [47], the run-time reliability of System-on-a-Chip (SoC) architectures was evaluated. The objective was to design SoCs that can adapt to environmental changes and unpredictable failure scenarios by introducing dynamic reliability, power management, and security tradeoffs. The implementation included five-stage RISC pipeline architecture with globally-accessible error counters in fixed time intervals. This technique addressed self-monitoring in SoC applications with redundant parts; we expand on this by presenting a novel OC system that not only provides self-monitoring capability, but also self-repair and self-adaptation for increased reliability yet with reduced power consumption than conventional redundancy techniques.

In [48], an Observer/Controller architecture was developed to provide a generic template to design control architectures for OC systems without extension to a hardware prototype implementation. This organic framework mainly targeted self-organization in a simulated environment and recommended thorough empirical studies of OC systems in different application domains. We extend on these concepts and investigate more self-x properties in real-life application of an edge detection circuit running in error-prone environments.

In [49], an organic computing paradigm called "marching-pixels" targeting future CMOS camera chips is presented. This paradigm relies on a massive fine-grain processor array to autonomously execute image pre-processing tasks, such as center detection and the tracking of moving objects. The organic concept stems from the fact that each pixel that falls on the detection path (e.g., edge, center, moving object, and so on) can be the origin or birth of a virtual organic object, which can then travel through a grid of identical PEs where it may die or join other pixels. The C-based simulator used to demonstrate "marching-pixels" confirmed the emergence of self-organization and self-healing in software simulated CMOS environment.

In [5], the role of middleware that acts between the hardware system and the application software is discussed for OC systems based on dynamically reconfigurable FPGAs. A scalable data flowdriven virtual machine (SDVM) is introduced. It is able to schedule parallel computing assignments to a set of reconfigurable and heterogeneous processing elements on a FPGA. The middleware is also able to dynamically balance the workload of the entire system in order to optimize power management and cope with faults. To demonstrate the advantages of SDVM, the Romberg numerical integration algorithm is implemented on the FPGA where the soft cores are used as processing elements. The results show the speedups achieved by executing the task on a variable number of processing elements as allocated by the middleware; a comparison is conducted with respect to sequential execution. Furthermore, self-organization and self-optimization are investigated in the experimental work, with less emphasize on self-repair due to the nature of the application. SMART on the other hand targets hardware sustainability in mission critical applications; with the main emphasize being self-repair and self-optimization of power consumption. In robotic applications a control architecture for a robot based on organic computing principles is presented in [50]. Decentralized control is shown to achieve the global objective of movement for a six-legged platform. The platform is also able to manage the failure of a node through its local rules and demonstrate sustainability in a mechanical environment.

More generally, in [51], Digital on-demand Computing Organism (DoDOrg) targeting real-time systems is presented. The system model is based on biological principles to achieve the desired self-x properties; it is divided into processing cells representing human cell analogs, middleware control representing organ analogs, and high-level control representing brain analog. The system is based on heterogeneous mix of computing elements, including standard elements such as CPUs and reconfigurable cells. The work presents an approach to organic computing that shows many of its desired self-x properties along with power management demonstrated using a robot-controller example. While the viability of this system is shown in a simulated environment, the transfer to a real robot system is sought in a later phase. In our work, we aspire from and extend on the significant self-x properties demonstrated in DoDOrg robot simulation by using an actual FPGA implementation of edge detection circuit, where the OC paradigm demonstrates power-conservative fault-tolerance through adaptive redundancy and software monitoring and refurbishment of the reconfigurable logic.

In an attempt to practically realize DoDOrg on FPGAs, a framework to achieve a decentralized configuration and power management scheme is shown in [4]. This work considers FPGAs as the most viable computing platform for OC systems due to the enormous benefits of reconfigurability. However, the work identifies the centralized nature of the FPGA's ICAP as the

main contradiction to the crucial decentralized requirement of OC systems. Therefore, a platform in which each computing node can autonomously and independently request its reconfiguration through the ICAP is presented. Similarly, power consumption is managed individually by each node at run-time to attain the desired virtual decentralization of the ICAP. Though this work does not present a complete implementation of an OC system, it does point toward the idea that FPGAs can serve as a viable computing platform for these systems. In the experimental setup, each computing node is autonomously and independently able to request its reconfiguration through the ICAP. Similarly, power consumption is managed individually by each node at runtime.

#### 2.2.3. Genetic Algorithm Techniques

Evolutionary Algorithms are a family of intelligent, heuristic, search algorithms that are inspired by the Darwinian theory of natural evolution. Darwin's famous theory about the natural selection of the fittest individuals and the recombination of their genetic material to produce yet better individuals is imitated in the evolutionary algorithms.

#### 2.2.3.1.Standard GA Techniques

One of the widely used types of evolutionary algorithms is the *Genetic Algorithm* (GA). GA is an adaptive heuristic search based on initial set of individuals, called population; the selection process favors a subset of this population that shows better fitness according to a predefined function called the fitness function. This function must accurately quantify what a good solution

is for the problem in hand. Each individual is encoded into a genetic representation of the solution, called chromosome, which contain one or many blocks, each called a gene, which encodes a single physical trait of the individual. Once the fittest individuals in a generation are selected based on their fitness function, a set of genetic operators are applied on them to produce different chromosomes that might yield better solutions. The Genetic operators vary in their nature and usage, but two of them are used in almost all GA implementations, namely crossover and mutation.

Crossover is the recombination of genetic material to produce new chromosomes; the content of the genetic material is preserved, but only shuffled probabilistically hoping that this reshuffling could lead to the juxtaposition of some genes in such a way to increase the fitness of the offspring. Mutation on the other hand, is a probabilistic change in the chromosome to introduce new traits, this is similar to mutations in nature which produces better or worse individuals, but under any case, the selection pressure can pick the useful mutations and ignore the harmful ones by measuring the mutation impact on each individual.

Once the selected individuals are genetically operated, they get replaced into the population and another round of the algorithm is executed. In general, this approach is shown to converge into better fit solutions, based on the exploitation of the selection process and the exploration of the genetic operators.

Figure 2 depicts the GA process in a flow chart. The power of GA comes from the contradicting forces of exploitation and exploration [52]; the GA exploits the best solutions by picking them in

the selection process which favors the fittest individuals, then explores these selected solutions by recombining their genetic material and introducing limited randomness into them, in order to produce more diversity into the population.

Figure 2: Genetic Algorithm Flow Chart

There are two paradigms for implementing GA in reconfigurable applications: Extrinsic evolution via functional models that abstract the physical aspects of the real device, and intrinsic evolution on the actual devices. It is evident that extrinsic approaches simplify the evolution process as they operate on software models of the FPGAs.

For applications like fault handling in deep space missions, not all fault types can be readily accommodated by software models. Additionally, abstracting the physical aspects of the target device complicates rendering the final designs into actual on-board circuits, for instance, limitations such as routability of the design cannot be ensured until the final stages of the configuration process. For these reasons, intrinsic evolution can provide a direct approach to realizing physical designs for a specific FPGA device.

Several previous research efforts have addressed intrinsic evolution. A successful attempt on *Field Programmable Transistor Array (FPTA)* chips was implemented by [53]. FPTAs are transistor-level programmable devices configured by controlling the status of programmable switches interconnecting array of transistors. The work proposed new ideas for long-term hardware reliability using evolvable hardware techniques via an evolutionary design tool, called EHWPack, which facilitates intrinsic evolution by incorporating PGAPack genetic engine with Labview test-bed running on UNIX workstation. Digital XNOR Gate on two connected FPTA boards was intrinsically evolved.

Miller [54] addressed the importance of direct evolution on the Xilinx 6216 FPGA devices; the research explored the effect of the device physical constraints on evolving digital circuits. A

mapping between the representation genotype and the device phenotype was proposed, however, no implementation details were presented.

In [55], a *Multilayer Runtime Reconfiguration Architecture (MRRA)* framework illustrates the concept of a communication and reconfiguration interface with an embedded *System-on-Chip (SoC)*. This modular architecture has a hierarchical framework to support different functionalities as each functional layer can do its job independently of other working layers. It provides the logic, translation and reconfiguration layers with standardized interfaces for communication between these layers and the FPGA-based SoC. The bitstream was directly manipulated to efficiently realize different logic by modifying the content and/or reallocating the LUTs. SMART uses an enhanced version of MRRA based intrinsic evolution platform and introduces direct bitstream manipulation for Xilinx Virtex 4 devices as compared to Xilinx Virtex II Pro devices.

In this work, we test SMART using Sobel edge-detection algorithm on reconfigurable logic. There are various applications of edge-detection with main emphasis on identifying boundaries in an image; it is used for object recognition and quality monitoring in industrial applications, medical imaging applications such as magnetic resonance imaging (MRI), Ultrasound [56] and it is used for satellite imaging applications [57]. Numerous efforts have been made to accelerate this computationally expensive algorithm on specialized hardware using conventional design techniques [58-61]. Research has also been done on designing edge-detectors using evolutionary techniques [56, 62, 63]. A comparison between SMART edge-detection evolution results and the other edge-detection evolution techniques is shown in Table 11.

#### 2.2.3.2. Parallel GA Techniques

Traditional GA techniques have demonstrated outstanding capabilities in solving complex optimization problem since their introduction back in the 1970's. However, engineering and scientific applications have increasingly grown in complexity and criticality, demanding better solutions yet within strict optimization constraints such as time, cost, and power. For that, the research community targeted improving the GA performance in order to suit the nature of these complex mission critical applications. The most noticeable effort to improve on the SGA is the introduction of *Parallel Genetic Algorithms (PGA)*.

PGA adopts a divide-and-conquer approach to split the problems into pieces and thus exploits multiple processors to enhance the convergence time [64]. Among the many PGA subclasses that have emerged, *Island-Based Genetic Algorithm (IGA)* has been heavily studied and implemented in various scholar and practical domains.

IGA consists of several semi-isolated islands or demes, each of which hosts an independent GA implementation that runs in parallel with other demes' GAs. The islands exchange individuals from time to time in an effort to increase the chance of finding a better global solution. The IGA can apply global parameters, such as mutation rate, crossover rate, population size, to all islands or vary them across islands. IGA introduces new set of parameters such as the number of islands, the island topology, the migration rate, and the migration policy. Even though IGA appears to be a straight juxtaposition of many simple GA runs, the emergent behavior caused by speciation and migration entirely suits the organic theme of the OGA that we presented in this work.

The benefits of the IGA are many; some of them are listed below:

- 1- Understandability and Inherent Technical Support: IGA is the most popular approach among all PGA types [64]. This is partly attributed to the relative ease of this approach and its compatibility with the coarse-grain parallel computing paradigm.

- 2- Speedup and Quality of Solution: Many research efforts have shown the advantage of using IGA over SGA and other Parallel GA approaches [65-73]

- 3- More Diversified Population: Spatial distribution of individuals across multiple islands and allowing them to interact only through limited migrations will effectively reduce the chance that the best individuals take over the population rapidly and direct the GA toward local optima in the early stages of the search [74]

- 4- Closer Analogy to Natural Evolution: Although not necessarily an advantage, some advocates of the biological inspiration of computation algorithms believe that IGA represents a closer analogy to natural evolution, where the population is seldom a panmictic one; there are usually many niches that evolve separately and occasionally exchange individuals. [75]

- 5- Scalability and parallel-computation suitability: The effectiveness of IGA comes from the fact that the inter-process communication is minimal and only limited to the migration phase. Other Parallel GA paradigms, like a master-slave GA that distributes the selection knowledge [76], require heavy communication between the nodes in order to pick the

fittest among the entire population, this is not a problem in IGA as the selection process is limited to each island's subpopulation, the only time inter-process communication happens is when the individuals migrate, an event that sparsely occur in a traditional IGA (1% of population every 1 generation is a common choice [72])

6- Linearly separable problems and multi-objective optimization: The fact that subpopulations are evolved independently causes different islands to climb different peaks in the search space, provided that the migration rate is not too high to cause premature convergence for all islands. This finding amplifies the importance of IGA as it makes it a good candidate for achieving multi-objective optimizations, which are widely encountered in many scientific and engineering fields [77]

Examples of successful applications of IGA are shown in Table 3 below.

| Application                                                                        | Reference |

|------------------------------------------------------------------------------------|-----------|

| Database search using PGA                                                          | [78]      |

| Nuclear reactor optimization                                                       | [70] [69] |

| Travelling Salesman                                                                | [79]      |

| Royal Road functions (R1-R4)                                                       | [72]      |

| DeJong test suites [67], Goldberg, Korb, and Deb's ugly 3-bit deceptive problem    | [66]      |

| [71], and the zero-one knapsack problem [68].                                      |           |

| Total of eight functions:                                                          | [80]      |

| Four functions (IM1-IM4) are specially created to test properties of IGA; three of |           |

| them require that islands cooperate to find a good solution.                       |           |

| The remaining four are standard multimodal test functions, which are:              |           |

| Rosenbrock, Schwefel, Astrigin, and Griewangk.                                     |           |

| Optimal design of elastic flywheels                                                | [81]      |

| Optimization fine spatial grid of water pipes for groundwater remediation (pump-   | [82]      |

| and-treat technology)                                                              |           |

| Training a Recurrent Artificial Neural Network (RANN).                             | [83]      |

Table 3: Successful Applications of IGA

# **CHAPTER 3: SMART DESIGN OBJECTIVES**

In this section, we present the major design objectives of SMART. Each of these objectives, listed in Table 4, is analyzed in terms of motivation and how it has been approached in other studies; we then show the design decisions that each goal has prompted and how these decisions were manifested in the actual system design.

| Objective                | Motivation                                      | Impact on Design      |

|--------------------------|-------------------------------------------------|-----------------------|

| Exploit                  | tradeoff between reliability and overhead,      | RARS, Dynamic PR      |

| Reconfigurability to     | Incorporate run-time info in redundancy         |                       |

| Realize Adaptive Level   | decisions, make use of the reconfigurability of |                       |

| of Redundancy            | the FPGA as an adaptation technique             |                       |

| Develop Organically      | Account for hard-fault possibilities in space   | OGA, decoding Virtex- |

| Amenable Hard-Fault      | missions, Exploit reconfigurability to advance  | 4 CBS, AS, efficient  |

| Repair Techniques        | organic behavior, Utilize Evolutionary          | use of Xilinx Tools   |

|                          | Algorithms in the OC domain.                    |                       |

| Implement SMART and      | Discover and Mitigate difficulties in           | Sobel edge detector,  |

| Evaluate it Using Widely | implementing real OCs, provide test-bed for     | JTAG, GNAT, Verilog,  |

| Accepted Metrics         | future research, properly evaluate SMART        | JAVA GUI, CTMC,       |

|                          | against standard metrics                        | BL-TMR                |

Table 4: System Goals, Motivations, and Impacts

#### 3.1. Exploit Reconfigurability to Realize Adaptive Level of Redundancy

Traditional reliability techniques often rely on the concept of redundancy. Redundancy is the addition of resources, time and/or information beyond what is actually needed for normal system operation in order to maintain functionality and performance when faults occur. The tradeoff between overhead and reliability in redundant systems has been the focal interest of many research efforts in the past few decades [6]. Consequently, many redundancy schemes have emerged to support different reliability requirements. Some of the influential redundancy schemes are as follows.

- 1. TMR: This is a passive redundancy scheme that masks faults as they occur without isolating the faulty parts. TMR consists of three functionally-identical modules that perform the same task in tandem and a voter that outputs the majority vote of the three modules [84]. If one module fails, the other two can still overrule its erroneous output and maintain correct overall TMR output.

- 2. Duplex Configuration: Consists of two functional modules and a discrepancy detector that keeps track of any discrepancy between the outputs of the modules. The system should be able to tolerate a period of degraded operation until the fault is isolated and recovered by other means.

- 3. Stand-by Sparing. In this system, one module drives the system operation, while the others are hot spares in an idle state that are ready to be called into action. Cold spares, in contrast, are kept shut down and thus do not consume power, but they do incur some delay upon activation before they are able to replace the faulty module.