# NORMALLY-OFF COMPUTING DESIGN METHODOLOGY USING SPINTRONICS: FROM DEVICES TO ARCHITECTURES

by

#### ARMAN ROOHI

B.Sc. Shiraz University, 2008 M.S. Science and Research Branch, Azad University, 2011

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2019

Major Professor: Ronald F DeMara

© 2019 Arman Roohi

#### **ABSTRACT**

Energy-harvesting-powered computing offers intriguing and vast opportunities to dramatically transform the landscape of Internet of Things (IoT) devices and wireless sensor networks by utilizing ambient sources of light, thermal, kinetic, and electromagnetic energy to achieve battery-free computing. In order to operate within the restricted energy capacity and intermittency profile of battery-free operation, it is proposed to innovate *Elastic Intermittent Computation* (EIC) as a new duty-cycle-variable computing approach leveraging the non-volatility inherent in post-CMOS switching devices. The foundations of EIC will be advanced from the ground up by extending Spin Hall Effect Magnetic Tunnel Junction (SHE-MTJ) device models to realize SHE-MTJ-based Majority Gate (MG) and Polymorphic Gate (PG) logic approaches and libraries, that leverage intrinsic-non-volatility to realize middleware-coherent, intermittent computation without checkpointing, micro-tasking, or software bloat and energy overheads vital to IoT.

Device-level EIC research concentrates on encapsulating SHE-MTJ behavior with a compact model to leverage the non-volatility of the device for intrinsic provision of intermittent computation, and lifetime energy reduction. Based on this model, the circuit-level EIC contributions will entail the design, simulation, and analysis of PG-based spintronic logic which is adaptable at the gate-level to support variable duty cycle execution that is robust to brief and extended supply outages or unscheduled dropouts, and development of spin-based research synthesis and optimization routines compatible with existing commercial toolchains. These tools will be employed to design a hybrid post-CMOS processing unit utilizing pipelining and power-gating through state-holding properties within the datapath itself, thus eliminating checkpointing and data transfer operations.

"Dedicated to my beloved parents, my lovely wife, and my older brothers," for their love, endless support, encouragement & sacrifices.

# **ACKNOWLEDGMENTS**

I would like to express my sincere gratitude to Dr. DeMara who provided an opportunity for me to join the Computer Architecture Laboratory (CAL) research team, and conduct my research under his supervision. He has kindly supported me during this project, and his insightful comments helped me to proceed my research along the right direction leading to several publications in prestigious journals. I would also like to thank my committee members Dr. Enrique del Barco, Dr. Reza Abdolvand, Dr. Jun Wang, and Dr. Deliang Fan for supporting me and my research.

# TABLE OF CONTENTS

| LIST OF FIGURES                                          | . X   |

|----------------------------------------------------------|-------|

| LIST OF TABLES                                           | . xvi |

| CHAPTER 1: INTRODUCTION AND MOTIVATION                   | . 1   |

| Introduction                                             | . 1   |

| Motivation                                               | . 2   |

| Contributions                                            | . 4   |

| CHAPTER 2: BACKGROUND                                    | . 7   |

| Spintronic Concepts, Behaviors, and Switching Operations | . 7   |

| Magnetic Tunnel Junction (MTJ)                           | . 10  |

| MTJ Switching Approaches                                 | . 12  |

| Field-induced magnetic switching (FIMS)                  | . 12  |

| Thermal-assisted switching (TAS)                         | . 13  |

| Spin-transfer Torque (SST)                               | . 14  |

| Non-volatile spin-based logic                            | . 18  |

| Intermittent Approaches                                           | 19 |

|-------------------------------------------------------------------|----|

| CHAPTER 3: COMPACT MODEL OF STT/SHE                               |    |

| FOR BOTH IMTJ AND PMTJ                                            | 22 |

| Compact Model Of STT-MTJ                                          | 22 |

| MTJ Resistive Model                                               | 22 |

| Spin-Transfer Torque (STT) Switching Model                        | 25 |

| STT-MTJ Based Look-Up Table                                       | 28 |

| Compact Model Of SHE-MTJ                                          | 32 |

| SHE-MTJ Based Look-Up Table                                       | 37 |

| CHAPTER 4: SPINTRONICS MAJORITY GATE BASED DESIGNS                | 40 |

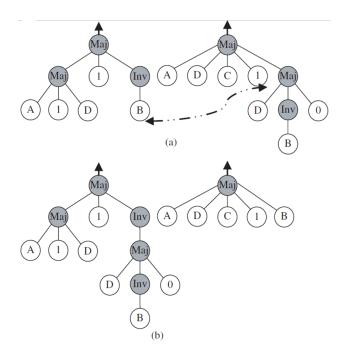

| MG-based Synthesis and Optimization Research Tool                 | 40 |

| Spintronics MG-based Circuit Designs                              | 43 |

| MG-based Full Adder using Current-Induced Domain Wall Nanomagnets | 45 |

| MG-based Full Adder using Spin Hall Effect Switching              | 58 |

| CHAPTER 5: SPIN-BASED NORMALLY-OFF COMPUTING APPROACHES           | 68 |

| NV FFs For Normally-Off Computing                                 | 69 |

| NV-Assisted Power Gating                                          | 70 |

| NV-Enabled Intermittent Computing                                | 71  |

|------------------------------------------------------------------|-----|

| SHE-based Majority Gate Cell Library                             | 73  |

| Proposed SORT Approach and SHE Technology Library Generation     | 75  |

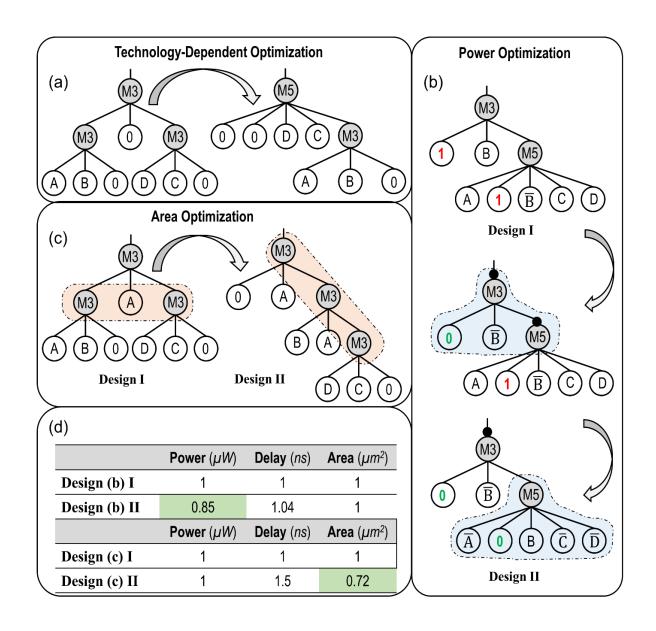

| Technology-Dependent Optimization                                | 77  |

| Power and Delay Optimization                                     | 79  |

| Area Optimization                                                | 82  |

| Simulation Results                                               | 82  |

| NV-Clustering Design Methodology                                 | 87  |

| Logic-Embedded FF (LE-FF) Design                                 | 88  |

| NV-Clustering Methodology                                        | 91  |

| Simulation Results                                               | 96  |

| Area Analysis                                                    | 98  |

| Power Analysis                                                   | 101 |

| Delay Analysis                                                   | 103 |

| Resumption Overhead                                              | 104 |

| CHAPTER 6: SECURE INTERMITTENT-ROBUST POLYMORPHIC GATE-BASED DE- |     |

| SIGN 1                                                           | 108 |

| Secure Intermittent-Robust Computation for IoT Devices                |

|-----------------------------------------------------------------------|

| Vulnerabilities under Charging Attacks                                |

| 111section*.51                                                        |

| Logic-Encrypted Synthesis for Spintronic-Embedded Datapath Design 110 |

| 116section*.53                                                        |

| Secure PG-FF design                                                   |

| PG insertion methodology                                              |

| Simulation Results                                                    |

| Area Analysis                                                         |

| Power-Delay Analysis                                                  |

| CHAPTER 7: CONCLUSION AND FUTURE WORK                                 |

| Technical Summary                                                     |

| Future Work                                                           |

| APPENDIX A: COPYRIGHT PERMISSIONS                                     |

| LIST OF DEFEDENCES                                                    |

# LIST OF FIGURES

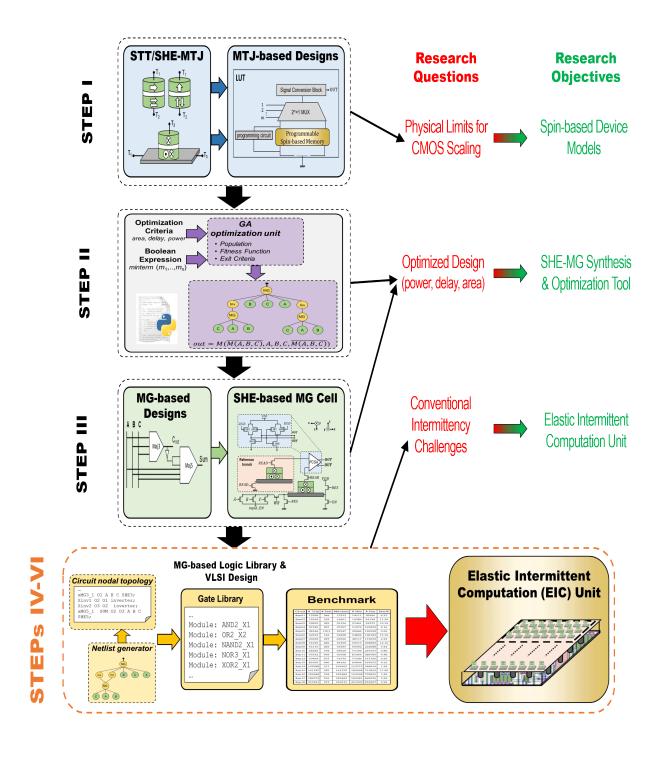

| Figure 1.1: Five required STEPs in the thesis to implement a new intermittent computing  |    |

|------------------------------------------------------------------------------------------|----|

| method for IoT applications                                                              | 6  |

| Figure 2.1: Energy barrier of a spin-based device                                        | 8  |

| Figure 2.2: GMR effect, (a) parallel state, and (b) anti-parallel state                  | 9  |

| Figure 2.3: Parallel and anti-parallel configurations of a TMR device                    | 10 |

| Figure 2.4: (a) MTJ vertical structure [1], (b) In-plane MTJ (IMTJ), and (c) Perpendicu- |    |

| lar MTJ (PMTJ).                                                                          | 12 |

| Figure 2.5: FIMS approach for MTJ                                                        | 13 |

| Figure 2.6: TAS approach for MTJ                                                         | 14 |

| Figure 2.7: Spin-transfer torque concept, (a) if electrons flow from the PL to FL, the   |    |

| magnet is switched to P state, and (b) if electrons flow from the FL to PL, the          |    |

| magnet is switched to AP state                                                           | 15 |

| Figure 2.8: Magnetization dynamics for a magnet in the presence of STT                   | 16 |

| Figure 2.9: (a) Positive current along +x induces a spin injection current +z direction. |    |

| The injected spin current produces the required spin torque for aligning the             |    |

| magnetic direction of the FM in +y directions, (b) Top view                              | 18 |

| Figure 2.10Main magnetic logic architectures, (a) MQCA [2], (b) DWL [3], (c) ASL [4],    |    |

| and (d) MTJ-based logic cell [5, 6]                                                      | 19 |

| Figure 3.1: Resistance hysteresis of an MTJ, red arrow shows switching from AP to P,    |    |

|-----------------------------------------------------------------------------------------|----|

| while blue arrow indicates switching from P to AP                                       | 24 |

| Figure 3.2: Illustrations (a) in-plane and (b) out-of-plane or perpendicular magnetized | 27 |

| MTJ                                                                                     | 21 |

| Figure 3.3: Four-input STT-LUT functional diagram.                                      | 29 |

| Figure 3.4: Reference MTJ cell and LUT MTJ cell dimensions                              | 30 |

| Figure 3.5: Transient response of STT-LUT for four-input NAND operation for (top)       |    |

| ABCD = "1111" and (middle) ABCD = "0000"                                                | 32 |

| Figure 3.6: SHE-MTJ vertical structure. Positive current along +x induces a spin injec- |    |

| tion current +z direction. The injected spin current produces the required spin         |    |

| torque for aligning the magnetic direction of the free layer in +y directions,          |    |

| and vice versa. (b) SHE-MTJ Top view                                                    | 33 |

| Figure 3.7: (a) 2-terminal MTJ (STT-MTJ) bit-cell, (b) 3-terminal (SHE-MTJ) bit-cell    | 36 |

| Figure 3.8: Circuit-level design of proposed SHE-LUT                                    | 37 |

| Figure 4.1: Two chromosomes (a) before crossover, and (b) after crossover               | 44 |

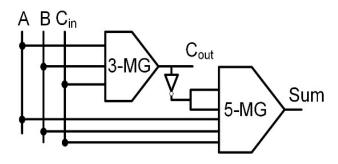

| Figure 4.2: Schematic of a 1-bit full adder using 3- and 5- input MGs                   | 45 |

| Figure 4.3: STT-driven Domain Wall motion                                               | 46 |

| Figure 4.4: (a) Schematic illustration of DWNM device, (b) construction of a DWNM       |    |

| logic gate suitable for Boolean logic implementation.                                   | 47 |

| Figure 4.5: DWNM (a) cell design, and (b) cross sectional view                             | 48 |

|--------------------------------------------------------------------------------------------|----|

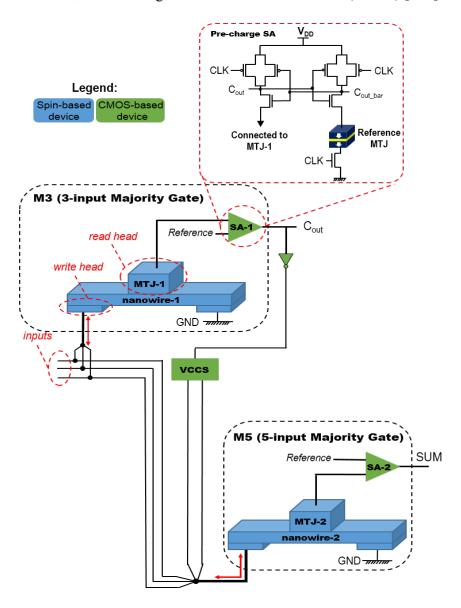

| Figure 4.6: Schematic of DWNM based Full-Adder Circuit. The main structure is com-         |    |

| prised of two DWNMs and two SAs, which operate as the functional building                  |    |

| blocks and the decision-making elements, respectively                                      | 49 |

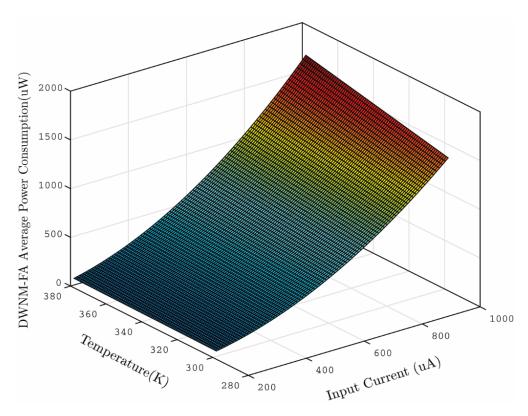

| Figure 4.7: Simulation results of 1-bit DWNM based FA. Logic 0/1 levels of inputs (A,      |    |

| B, and C) correspond to applied currents of -200A and +200A whereas bits 0                 |    |

| and 1 for outputs, Cout and SUM, correspond to the voltage of 0V and 1.8V.                 |    |

| For instance, input current pulses ABC=011 nucleate the DW in nanowire-1,                  |    |

| Cout=1, and cannot unpin the DW in nanowire-2, SUM=0                                       | 51 |

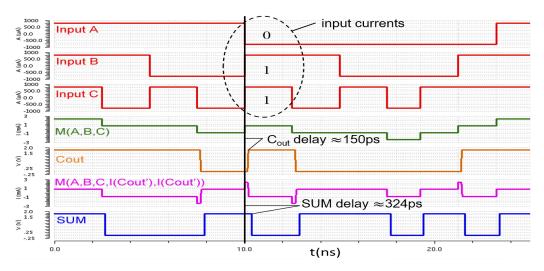

| Figure 4.8: Dependence of DWNM-FA Average Delay on Input Current are depicted for          |    |

| circuit outputs Cout and SUM                                                               | 54 |

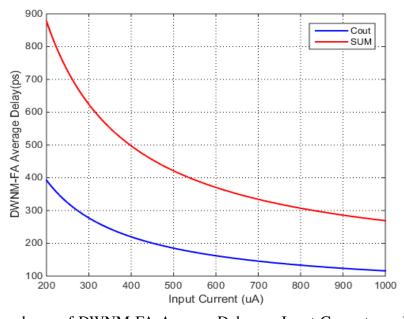

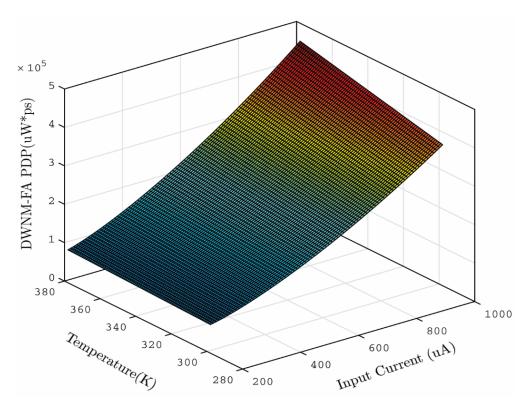

| Figure 4.9: Power Consumption of DWNM-FA versus temperature and applied current            | 56 |

| Figure 4.10PDP of DWNM-FA versus temperature and applied current                           | 57 |

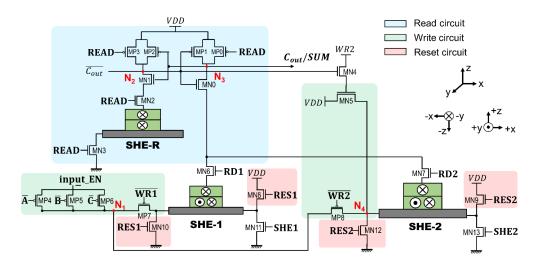

| Figure 4.11Circuit-view of SHE-based FA design. SHE-1 functions as a 3-input MG,           |    |

| while SHE-2 performs 5-input MG function                                                   | 58 |

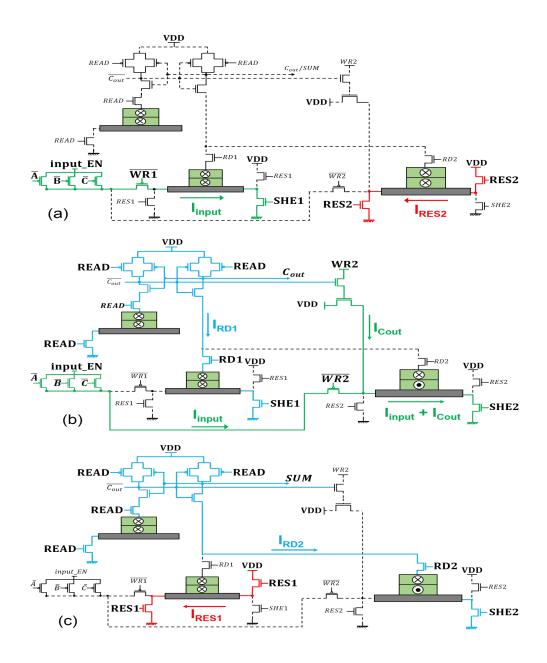

| Figure 4.12SHE-based functionality for input ABC = "010" (a) write and reset operations    |    |

| for SHE-1 and SHE-2 occurred, respectively, $I_{input}$ = 94 $\mu A < I_{C-SHE1}$ ; hence, |    |

| FL of SHE-1 remains in P state, then (b) read and write operation for SHE-1                |    |

| and SHE-2 perform simultaneously, in which injected current through SHE-                   |    |

| 2 is 146 $\mu A > I_{\text{C-SHE2}}$ , so FL of SHE-2 changes to AP state, and finally (c) |    |

| SHE-1 is reset along with reading SHE-2 state.                                             | 63 |

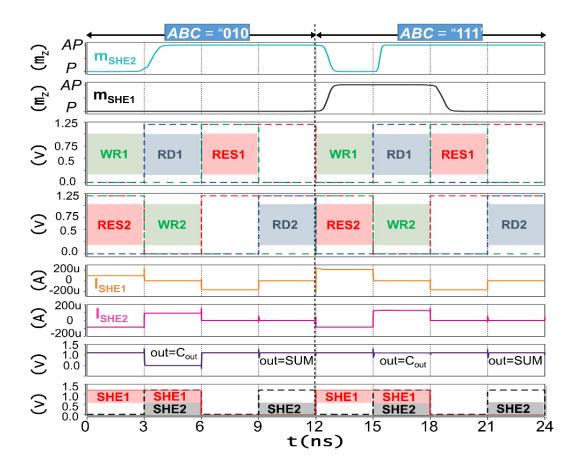

| Figure 4.135 imulation results of 1-bit SHE-based FA for two input sequences, 010 and                                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| "111"                                                                                                                                                                                                                 | 64 |

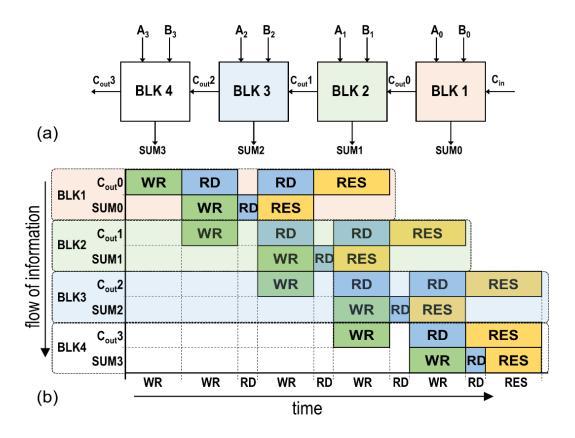

| Figure 4.14Schematic of 4-bit SHE-based FA and its timing diagram                                                                                                                                                     | 66 |

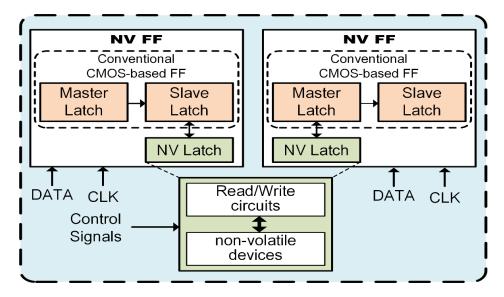

| Figure 5.1: Block diagram of NV-FFs, (left) modified slave stage, and (right) modified master stage                                                                                                                   | 71 |

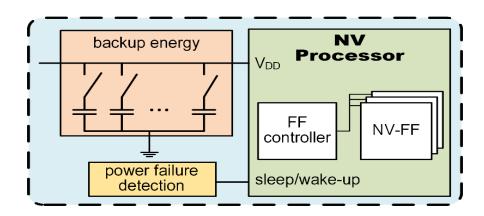

| Figure 5.2: Overall structure of intermittent resilient architecture                                                                                                                                                  | 72 |

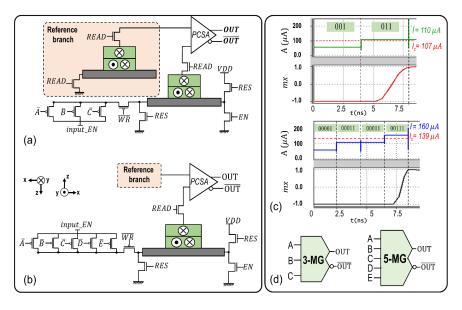

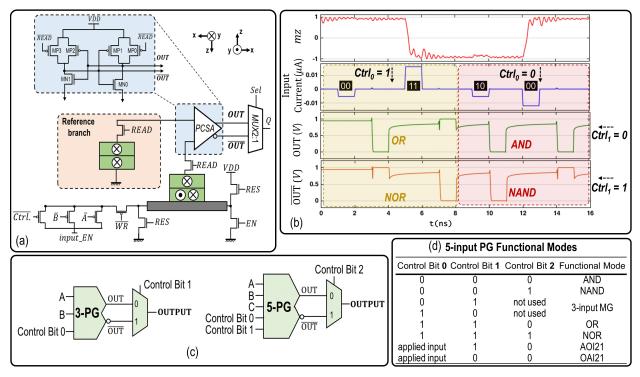

| Figure 5.3: (a) SHE-MTJ based 3-input MG, (b) SHE-MTJ based 5-input MG. Simulation results for (c) 2-input OR logic, and 3-input AND logic using MG3 and MG5, respectively, (d) 3-input and 5-input SHE-MTJ based MGs | 74 |

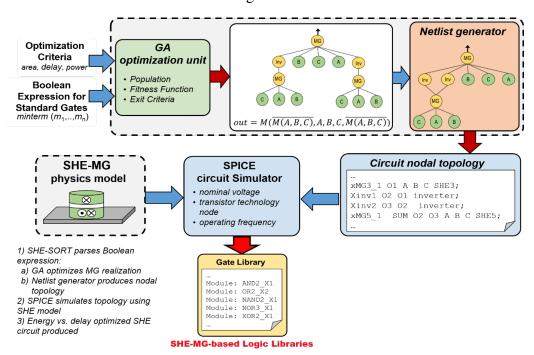

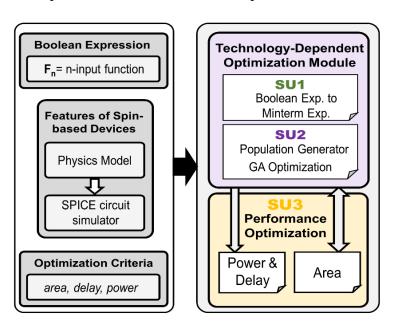

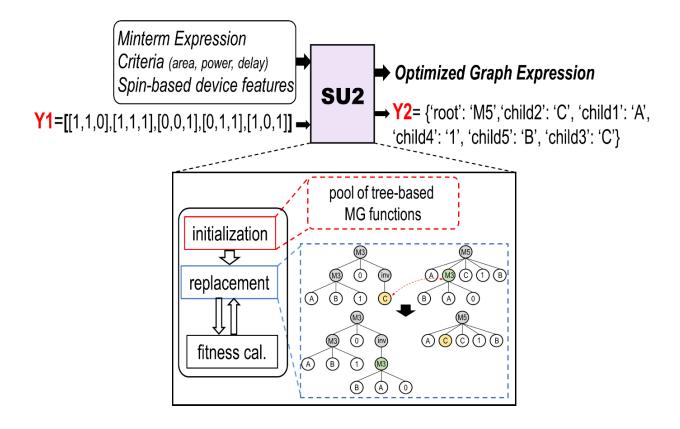

| Figure 5.4: Proposed MG synthesis approach to realize SHE-based Boolean Logic, including SHE-MG based gate libraries                                                                                                  | 75 |

| Figure 5.5: Schematic of the proposed evolutionary approach to realize MG- based NoC circuit                                                                                                                          | 76 |

| Figure 5.6: Operations of F1 and F2 blocks for AB+C in technology-dependent optimization process                                                                                                                      | 79 |

| Figure 5.7: (a) technology-dependent optimization for $F=A.B.C.D$ , (b) power optimization for $F=A+B+C+D$ , (c) area optimization for $F=A(B+CD)$ , and (d) comparison results for Designs in (b) and (c)            | 84 |

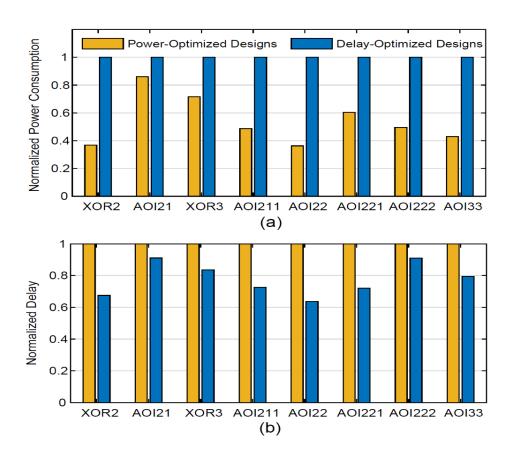

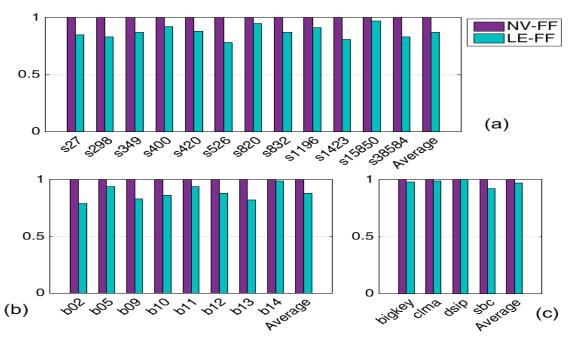

| Figure 5.8: Normalized results for (a) power consumption, and (b) delay leveraging two optimization approaches                                                                                                        | 85 |

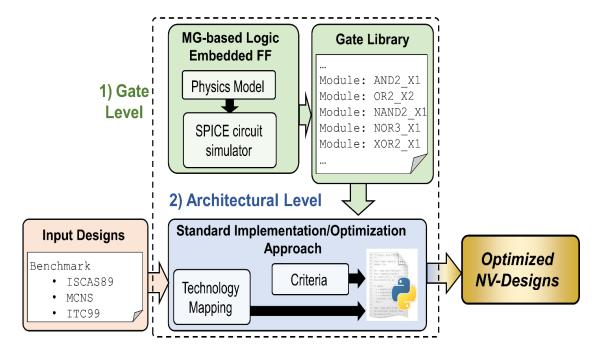

| Figure 5.9: Optimized NV implementation methodology diagram                                                                                                                                                                                                                | 87  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

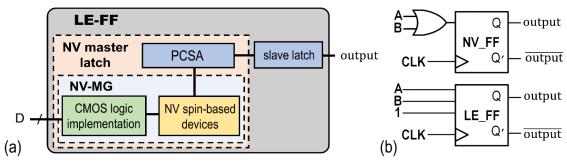

| Figure 5.10(a) Schematic of proposed MG-based LE-FF, and (b) different implementations using NV-FF (top), and proposed LE-FF (bottom)                                                                                                                                      | 90  |

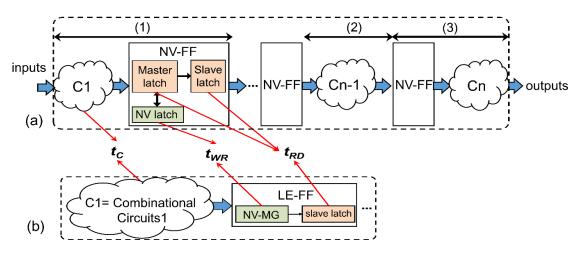

| Figure 5.11All three sensitive time durations for (a) NV-FF based implementation, and for (b) proposed implementation approach, in which $C1(b) < C1(a)$                                                                                                                   | 90  |

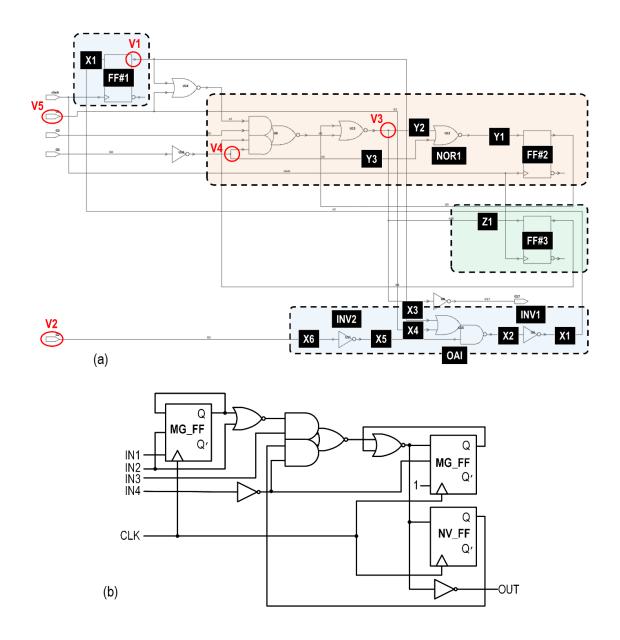

| Figure 5.12(a) s27 schematic with highlighted FFs, and (b) optimized LE-FF based design after NV-Clustering.                                                                                                                                                               | 95  |

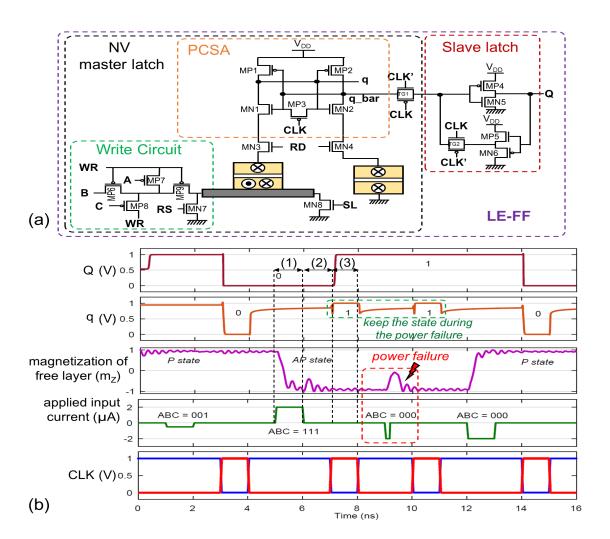

| Figure 5.13Circuit-level design of proposed 3-input SHE-based LE-FF, and (b) transient response for three different input ABC= "001", "111", and "000" in presence of power failure. Three different modes are shown: (1) store mode, (2) standby mode, and (3) sense mode | 98  |

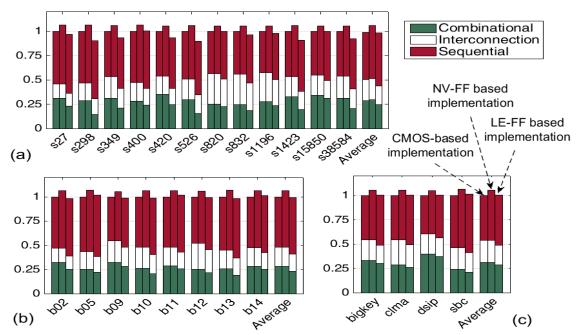

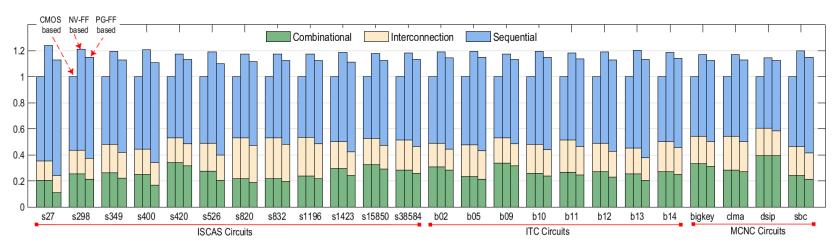

| Figure 5.14Normalized area consumption compared to CMOS-based implementations for different benchmarks.                                                                                                                                                                    | 100 |

| Figure 5.15Normalized power dissipation compared to NV-FF. Results based on realization of combinational components                                                                                                                                                        | 102 |

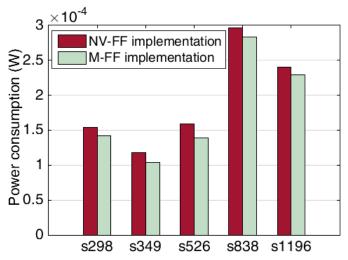

| Figure 5.16Total power consumption for selected ISCAS-89 circuits                                                                                                                                                                                                          | 102 |

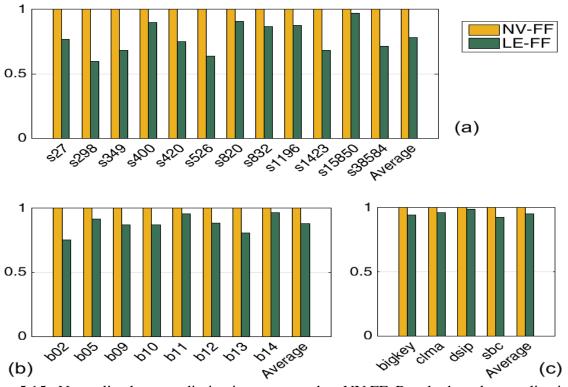

| Figure 5.17Normalized delay compared to NV-FF based implementations for different benchmarks                                                                                                                                                                               | 103 |

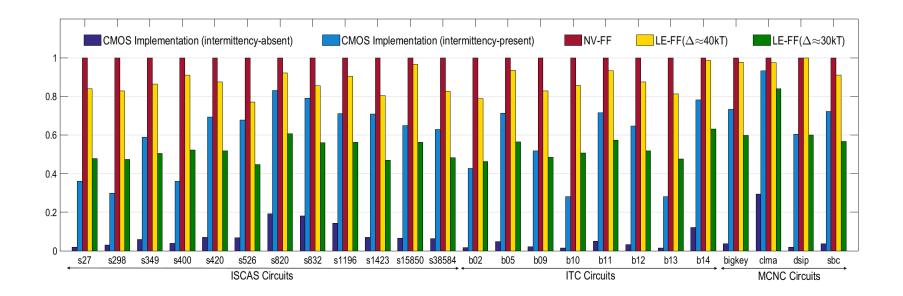

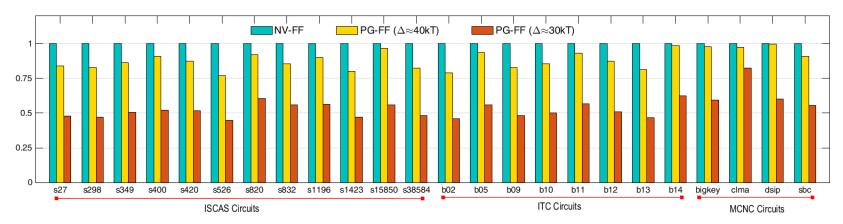

| Figure 5.18Normalized PDP compared to NV-FF based implementations for <i>intermittency-</i>                                                                                                                                                                                | 107 |

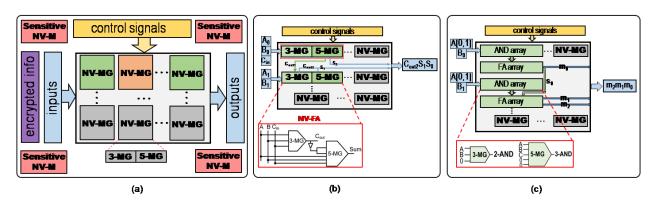

| Figure 6.1: (a) SIRC computation pool of NV-MGs, (b) NV-FA arrangement using 3-MG            |

|----------------------------------------------------------------------------------------------|

| and 5-MG, and (c) 2-bit NVM multiplier                                                       |

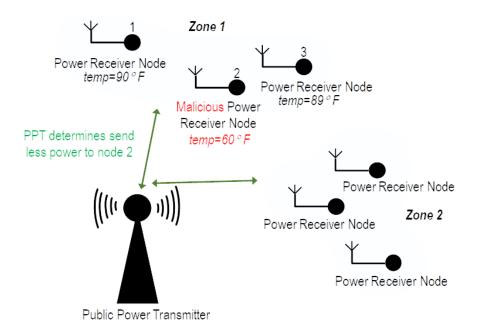

| Figure 6.2: Feasible countermeasure for charging attack by marking a possible malicious node |

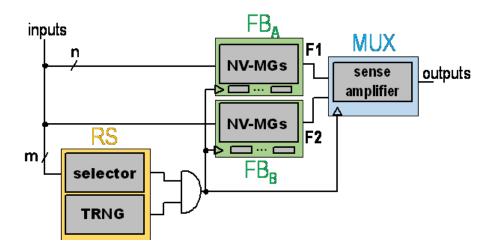

| Figure 6.3: Power masking countermeasure for possible power analysis attack. F1 and          |

| F2 perform the same function with different power consumption                                |

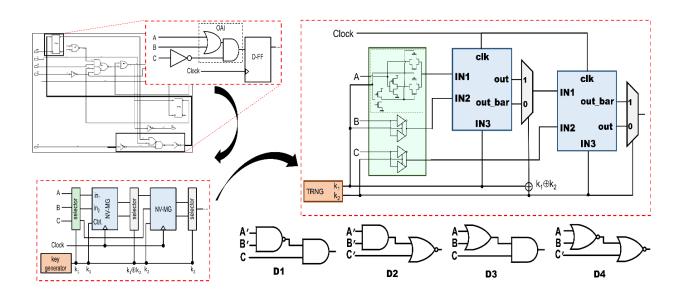

| Figure 6.4: s27 schematic (top left), selected cone gate (bottom left), developed MG-FF      |

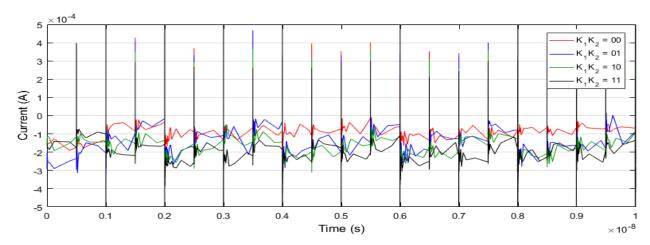

| based design (top right), and equivalent logic realizations (bottom right) 11:               |

| Figure 6.5: Power traces results for all possible $K_1K_2$ combinations                      |

| Figure 6.6: (a) SH-MTJ based 3-input PG, (b) 2-input OR, NOR, AND and NAND logic             |

| using 3-input PG, (c) 3-input and 5- input SHE-MTJ based PGs, (d) 5-input                    |

| PG Functional Modes                                                                          |

| Figure 6.7: Normalized area consumption compared to CMOS-based implementations               |

| for ISCAS, ITC, and MCNC benchmarks                                                          |

| Figure 6.8: Normalized PDP compared to NV-FF based implementations for ISCAS,                |

| ITC, and MCNC benchmarks                                                                     |

# LIST OF TABLES

| Table 2.1: | Characteristics of enabling technologies. "√" or "-" indicates strength/limitation |    |

|------------|------------------------------------------------------------------------------------|----|

|            | relative to CMOS                                                                   | 20 |

| Table 2.2: | Selected previous works with significant contributions towards intermittent        |    |

|            | processor design.                                                                  | 21 |

| Table 3.1: | performance comparison between STT-LUT and SRAM-LUT for four-input                 |    |

|            | NAND operation                                                                     | 30 |

| Table 3.2: | Performance comparison for four-input NAND operation                               | 31 |

| Table 3.3: | Parameters of SHE-MTJ-based LUT                                                    | 35 |

| Table 3.4: | Switching Characteristics of a Single MTJ Cell Including Clocking Require-         |    |

|            | ments                                                                              | 36 |

| Table 3.5: | Performance comparison for the Reconfiguration Operation of 4-input MTJ-           |    |

|            | LUTs Involving 16 MTJs                                                             | 39 |

| Table 4.1: | Optimization of three standard functions                                           | 43 |

| Table 4.2: | Simulation Parameters of DWNM and MTJs                                             | 52 |

| Table 4.3: | Nanowire-1( for Cout) and Nanowire-2 (for SUM) Switching Delays                    | 53 |

| Table 4.4: | Comparison of 1-bit Full Adders                                                    | 57 |

| Table 4.5: | Simulation Parameters of SHE-based FA                                              | 60 |

| Table 4.6: | Required signaling for 1-bit SHE-based FA 61                               |

|------------|----------------------------------------------------------------------------|

| Table 4.7: | SHE-based FA Performances for all Input Combinations                       |

| Table 4.8: | Comparison of logic-in-memory 1-bit full adder circuits                    |

| Table 5.1: | Switching results for 3-input SHE-MG                                       |

| Table 5.2: | Switching results for 5-input SHE-MG                                       |

| Table 5.3: | Read operation results for 3- and 5- input SHE-MGs                         |

| Table 5.4: | Optimized implementation of the functionally-complete set of Boolean logic |

|            | gates using SHE-MGs                                                        |

| Table 5.5: | Boolean Expressions using 3 and 5 -input MGs                               |

| Table 5.6: | Gate Counts for s27 Benchmark Circuit                                      |

| Table 5.7: | NV-Clustering Gate Equivalent Reduction                                    |

| Table 6.1: | Generated Keys and Their Corresponding Average Power Consumption 115       |

| Table 6.2: | PG-insertion results for ISCAS benchmarks                                  |

### **CHAPTER 1: INTRODUCTION AND MOTIVATION**

#### Introduction

For the past five decades, complementary metal-oxide-semiconductor (CMOS) has been the dominant technology and it has provided the demanded dimension scaling for implementing highperformance and low-power circuits. The evolution of this charge-based CMOS devices is described and predicted by Moore's law [7], this prediction, that number of transistors in integrated circuits (ICs) doubles roughly every two years, has continued for many years. On the other hand, by the inevitable scaling down of the feature size of the CMOS transistors which are deeper in nanoranges, the CMOS technology has encountered many critical challenges such as high leakage currents, reduced gate control, high power density, increased circuit noise sensitivity and high lithography costs which obstruct the continuous dimension scaling and consequently degrade the suitability of the CMOS technology for the near future high-density and energy efficient applications. Explaining in more details about the first aforementioned restriction, due to the quantum mechanical tunneling of electrons from the gate electrode into the transistor channel through the gate oxide, leakage current occurs. Owing to the Moor's law's and mentioned problems as well as the increasing chip complexity, researchers have to start seeking novel technologies to replace the charge-based devices. Among promising devices, 2015 International Technology Roadmap for Semiconductors (ITRS) [8] identifies nanoscale devices as capable post-CMOS candidates such as Quantum-Dot Cellular Automata (QCA) [9, 10], and Spintronics [11, 12] (feasible competitive alternative). Spintronics devices show promising features such as non-volatility, near-zero static power, and high integration density. The non-volatility means that the data can be maintained even if the power is off, so the standby power is reduced significantly. Moreover, due to the possibility of 3D integration above CMOS designs at the back-end process, distances between logic and memory can be shortened, which reduces considerably the dynamic power. The scalability feature of spin-based devices in addition to their low power characteristic, make the Spintronics as a promising alternative for CMOS architectures.

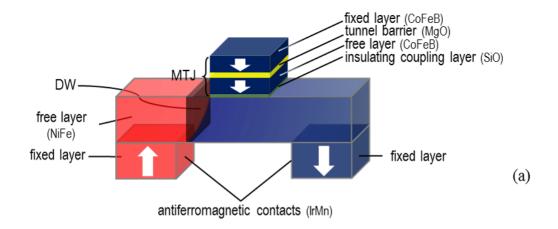

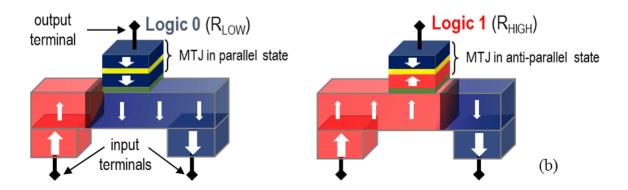

Recently, magnetic tunnel junction (MTJ) devices are one of the most important components of any spin-based structures, which can be configured into two different stable configurations. Due to the tunnel magnetoresistance (TMR) effect, these two parallel and anti-parallel states show low and high resistance, which can be denoted "0" and "1" in binary information, respectively. Two of developed switching approaches for MTJs are spin-transfer torque (STT) [13] and spin-Hall effect (SHE) [1], in which only one bidirectional current is required. In the STT switching approach, the bidirectional current passes through an MTJ according to which it can be configured into P or AP state. Although STT offers several advantages over previous switching methods like field-induced magnetic switching (FIMS) [14] and thermally assisted switching (TAS) [15], it suffers from some challenges such as high write current, and switching asymmetry [16, 17]. Moreover, STT-MTJ is a two-terminal device with a shared write and read path. Consequently, undesirable switching may occur during the read operation, and stored data can be flipped accidentally. Recently, SHE-MTJ, a 3-terminal device, has been researched as a potential alternative offering some benefits such as decoupled read and write paths, as well as energy efficient and high-speed write [18, 19, 20].

#### Motivation

Intermittent computation approach offers intriguing and vast opportunities to dramatically transform the landscape of IoT devices. The Internet of Things (IoT) devices require drastically-reduced energy consumption such that they are able to operate using only ambient sources of light [21, 22], thermal [21, 23], kinetic [21, 24], and electromagnetic energy [25] as a means to achieve battery-free computing [26]. If lightweight embedded computing could be realized with free and/or inex-

haustible sources of energy, new classes of maintenance-free, compact, and inexpensive computing applications would become possible [27]. Thus, energy-harvesting-powered devices could enable a sustainable computing platform for future medical [28], aerospace [29], and IoT [30] applications. Energy-harvesting devices are projected to develop towards a \$2.6B market by 2024, thus automating human interaction with everyday items in our environment or even life-saving medical implants within our bodies [31].

Therefore, it is proposed to research a promising class of rudimentary processing elements which utilize switching devices capable of leveraging (1) the restricted energy capacity and (2) the intermittent temporal energy profile, of energy harvesting schemes. A typical energy harvesting system converts ambient energy via rectification and charge-trapping. Then energy is accumulated on capacitor to generate a supply voltage. Once the voltage of the capacitor attains a sufficient level, then a lightweight embedded processing element can commence its operation. However, the stored energy will be rapidly consumed, which consequently precludes the continuation of execution due to an insufficient supply voltage. Hence, the supply voltage of the processor experiences intermittent behavior. This results in an interval,  $\tau_{idle}$ , of unpredictable unavailability that can interrupt the datapath and the processor clock. This charge/discharge cycle, which is an intrinsic characteristic of energy harvesting devices, may occur more than hundreds of times per second for RF-based sources, and unpredictably for extended durations with kinetic and light-powered sources. Furthermore, the interval  $\tau_{idle}$  can occur irregularly and vary in duration leading us to research methods to achieve a new Elastic Model of Computation described herein. Hardware realization of elastic computing addresses one of the major hurdles to the propagation of energy harvesting systems: robust operation despite discontinuities in the ambient energy supplied from its environment. Robust intermittent operation presents a new and difficult technical challenge that precludes assumptions of conventional processor design of the last several decades. Intermittent behavior can result in disturbances in the execution of programs, data loss, glitch conditions, and lack of execution progress

that may lead to irregular and unpredictable results [32]. Therefore, most of the existing energy harvesting systems are envisioned for rudimentary signal detection and sensing applications such as monitoring blood pressure or accumulating temperature readings [33]. This proposed herein could realize these at improved lifetime energy and area metrics.

Grand Hypothesis: The proposed circuits employing spintronic devices realize Elastic Intermittent Computation enabling a non-deterministic duty cycle, while reducing leakage energy by 90% and circuit lifetime energy-delay-product by 60% compared to existing designs of comparable area.

Regardless if the hypothesis is validated or not, the proposed research will advance multiple promising directions towards beyond-CMOS devices and architectures for next energy harvesting powered processors.

#### Contributions

Due to the abovementioned research background and motivation, four objectives are addressed: First, to explore the energy and delay characteristics of spin-based VLSI circuits as well as innovate novel architectural schemes utilizing non-volatile logic, by integrating Verilog-A and SPICE models, a compact model for STT-IMTJ, STT-PMTJ, and SHE-IMTJ are developed. They express the underlying both static and dynamic switching behavior and encapsulate their characteristics, while allowing straightforward integration with VLSI circuits in SPICE-like platforms. To validate the model, two STT and SHE Look-up Table (LUT) circuits are designed and their functionalities are verified.

Second, a Genetic Algorithm (GA)-driven research synthesis and optimization MG-based is developed. Extracting the fan-in optimized design based on 3- and 5- input MGs to design Boolean logic

gates and logic circuits such as Full-Adders (FAs). Two novel designs of the 1-bit majority gate (MG) based full adder (FA) using domain wall nanomagnet (DWN) and SHE-MTJ are proposed. These emerging designs achieve significant improvements in terms of area, complexity and power consumptions. Then SHE-based 3- and 5- input MGs library developed.

Third, Then, preliminary results of the modeled SHE-MTJ devices will be utilized to delineate the power, delay, and area costs of the spin-based building blocks in the synthesis and optimization tool. The Boolean functions and criteria can be applied as inputs into the tool, which outputs a SPICE syntax compatible file that can be utilized by circuit simulation toolchain.

Forth, the developed tool is used to extract an optimized netlist for standard majority logic-based gates such as AND, OR, NAND. New libraries containing a functionally-complete set of Boolean logic gates required for implementing representative VLSI designs will be defined and populated using the developed device models. To verify the functionality and demonstrate energy and performance characteristics, we will implement MCNC benchmark circuits in commercial synthesis tools utilizing the developed spin-based gate libraries.

Finally, circuit-level results will be extended towards benchmark studies corresponding to lifetime energy reduction and intermittent operational behavior demanded by IoT applications. Both goals can be achieved by utilizing the non-volatility of the targeted devices to enable gate-level pipelining, without requiring registers for each stage. Thus, an intermittent operation is supported without the burden of additional circuitry otherwise required for checkpoint-restore, backup, etc. Avoiding registers also provides significant area reduction, which is important to achieve IoT size/cost constraints.

The steps of the work in this document can be depicted in Figure 1.1 from the device to the architecture hierarchy.

Figure 1.1: Five required STEPs in the thesis to implement a new intermittent computing method for IoT applications.

## **CHAPTER 2: BACKGROUND**

### Spintronic Concepts, Behaviors, and Switching Operations

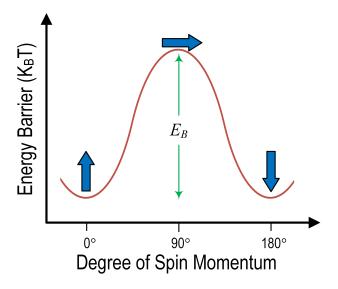

Spin transport electronics (Spintronics) is a novel computing paradigm, which functions regarding the degree of electron spin in solid-state electronics using spin-polarized current [34]. Since spin-based devices are built on magnets, they have two stable polarizations,  $0^{\circ}$  and  $180^{\circ}$  magnet spin momentum, which denote up-spin and down-spin, respectively. These two states can be maintained in a magnet without any electrical power, non-volatility, due to its energy barrier ( $E_B$ ). The relation between the information retention time and the energy barrier is expressed by Equation 2.1:

$$T_{retention} = T_0 e^{\left(\frac{E_B}{K_B T}\right)}, \quad E_B = K_u V \tag{2.1}$$

where  $T_0$  is the characteristic time  $K_B$  is the Boltzmann's constant, T is the temperature,  $K_u$  is the magnetic anisotropy, and V is the magnet volume. In most spin-based memory and logic implementations,  $E_B$  set to 40 which results in ten years for  $T_{retention}$ . The two stable states regarding  $E_B$  are shown in Figure 2.1.

Concept of Spintronics can be defined by two main aspects: (1) spin polarization and (2) magnetoresistance, which are utilized to perform write and read operations, respectively. The imbalance of up-pin  $(n \uparrow)$  and down-spin  $(n \downarrow)$  population in ferromagnetic (FM) devices can be considered as spin population, which is defined as

$$P = \frac{|n \uparrow - n \downarrow|}{n \uparrow + n \downarrow} \tag{2.2}$$

Figure 2.1: Energy barrier of a spin-based device.

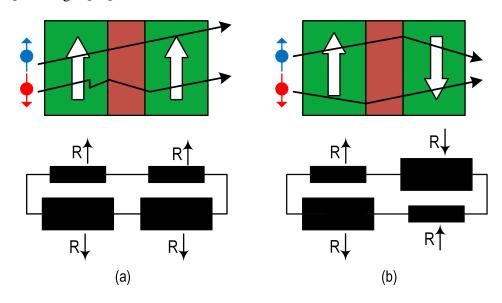

When a charge current passing through an FM, it can be polarized according to the local magnetic momentum, hence, a spin-polarized current can be produced. The magnetoresistance is affected by scattering of electrons on the FM layers. There is a high or low magnetoresistance (MR) for magnetic materials, which is used to detect the states of magnetic devices. The two most important MR effects in metal multilayer films are Giant Magnetoresistance (GMR) [35, 36] and Tunneling Magnetoresistance (TMR) [37, 38]. The GMR devices are composed of two FM layers which are separated by a nonmagnetic metal layer such as copper. If magnetization directions of two FM layers are same, parallel (P) configuration, one of the spin-up or spin-down electrons pass through the device without scattering, which leads to lower resistance. Whereas, if magnetization directions of these FM layers are in the anti-parallel configuration (AP), both spin-up and spin-down electrons face scattering issue, which results in higher resistance. Due to the difference between the P and AP configurations, which can reach 100%, this MR effect named giant magnetoresistance. The highly-used GMR-based application is a spin valve concept, which has been leveraged in conventional hard disk drives as reading heads. Figure 2.2 depicts the GMR effect in two-channel multilayer

films. If we replace the non-magnetic layer in a GMR structure by a thin oxide insulator such as AlxOy [39] and MgO [40], TMR effect can be detected.

Figure 2.2: GMR effect, (a) parallel state, and (b) anti-parallel state.

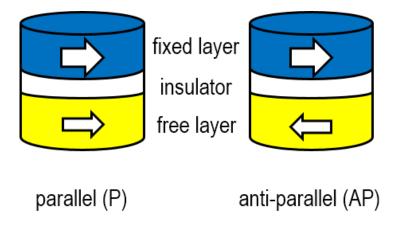

This spacer is enough thin to allow tunneling effect for the electrons. Figure 2.3 shows a TMR device and its two stable states. Similar to the GMR effect, TMR can define P and AP magnetization orientations by two different low and high resistances, respectively. However, in addition to the difference in barrier material for GMR and TMR devices, there are two main differences.

First, in GMR structure, current flows in both "in the layer plane" (CIP) or "perpendicular to plane" (CPP) [41], however, in TMR, current can pass only in a perpendicular way. Second, in GMR, all its layers are a conductor, which means the larger current is transferred, nonetheless, in TMR devices, we have an insulator, which is preferable in non-volatile memory and logic designs.

Figure 2.3: Parallel and anti-parallel configurations of a TMR device.

#### Magnetic Tunnel Junction (MTJ)

The vertical structure of an MTJ is shown in Figure 2.4 (a), where an insulating barrier is sand-wiched between two FM layers, Pinned Layer (PL) and Free Layer (FL) [42]. The barrier is enough thin to enable the electron tunneling effect. Each FM layer has a magnetization which can be switched by a magnetic field between two stable directions along the anisotropy axis. Because these layers have different coercivities, which is defined as the magnetic field to switch the magnetization, PL is magnetically-pinned and utilized as a reference layer, while the FL magnetic orientation can be switched to be parallel (P) or anti-parallel (AP) to that of the PL, which gives a low (RP) or high (RAP) tunneling resistance, respectively, as shown in Figure 2.4 (b). This resistance is specially called tunneling magnetoresistance (TMR) and the mechanisms behind the TMR effect is spin-dependent tunneling, which actually was observed and proposed by Jullière as early as 1975 [42]. The primary performance for an MTJ is determined by TMR ratio which can be defined as

$$TMR = \frac{\Delta R}{R_P} = \frac{R_{AP} - R_P}{R_P} = \frac{G_P - G_{AP}}{G_{AP}}$$

(2.3)

where  $G_P$  and  $G_{AP}$  are the conductances of parallel and anti-parallel states. The expressions of conductance are given by

$$G_P = N_{M1}N_{M2} + N_{m1}N_{m2}$$

$$G_{AP} = N_{M1}N_{m2} + N_{m1}N_{M2}$$

(2.4)

where  $N_{M1}$  and  $N_{m1}$  are the effective densities of states of majority and minority electrons at the Fermi energy in both magnetic layers. As a result, the TMR ratio can be calculated using Equations 2.2, 2.3 and 2.4, which is expressed in terms of the spin polarization by

$$TMR = \frac{2P_1P_2}{1 - P_1P_2} = \begin{cases} R_P = \frac{2}{1 + P_1P_2} \\ R_{AP} = \frac{2}{1 - P_1P_2} \end{cases}$$

(2.5)

where  $P_1$  and  $P_2$  are spin-polarizations in two layers. The significant progress was occurred in 1994 by using amorphous  $Al_2O_3$  as the tunneling barrier to realizing the room temperature magnetic tunneling transport [38, 43]. By optimizing the material and fabrication condition, the TMR ratio of this structure can reach up to 70% [39]. Although this value is already much larger than GMR in spin valve, it is still far away from the requirement for spintronic applications, for example, high-density MRAM requires at least 150% TMR at room temperature. Another considerable leap of MTJ is using a single-crystal MgO tunnel barrier that can provide even larger TMR, which is sometime called the giant TMR effect [44, 45]. So far, the TMR ratio record of MgO based MTJ can reach as high as 600% at room temperature [46]. These results are of great importance not only to avoid the CMOS process mismatch and parameter variation, but also to miniaturize the sense amplifier circuit area [47].

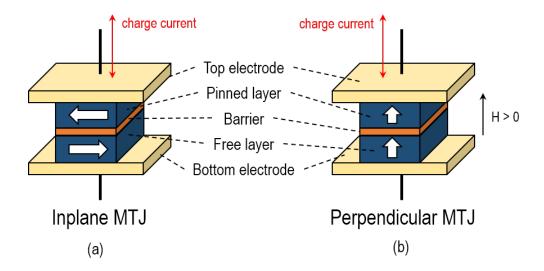

The magnetic direction of MTJ layers can be in the film plane, in-plane MTJ (IMA), or out of the film plane referred to as perpendicular MTJ (PMA) structure, as shown in Figure 2.4 (b) and

2.4(c), respectively. PMAs have advantages over IMAs such as lower switching critical current and higher thermal stability.<sup>1</sup>.

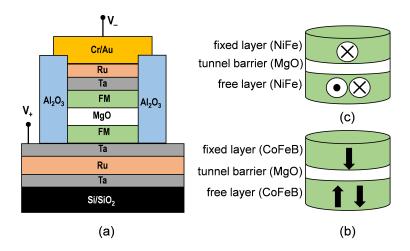

Figure 2.4: (a) MTJ vertical structure [1], (b) In-plane MTJ (IMTJ), and (c) Perpendicular MTJ (PMTJ).

#### MTJ Switching Approaches

The write operation of an MTJ is achieved by switching the FL magnetization. Herein, brief efficient write methods for MTJ are introduced.

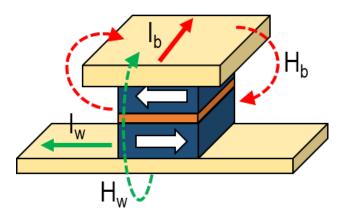

#### Field-induced magnetic switching (FIMS)

In this approach, the magnetization orientation of the free layer is switched by applying an external magnetic field, which is generated by two orthogonal current lines, the word line (WL) and bit line (BL), as shown in Figure 2.5. To perform a write operation, two currents,  $I_w$  and  $I_b$ , are applied to

<sup>&</sup>lt;sup>1</sup>©2016 IEEE. Reprinted, with permission, from [48, 49]

WL and BL, which generate the hard-axis,  $H_w$ , and easy-axis,  $H_b$ , switching fields, respectively. Herein,  $H_w$  equals  $2K_u/M_s$  where  $M_s$  is the saturation magnetization is applied perpendicular to the easy axis. Then this field is removed and a smaller bias field is applied along the easy axis to complete the switching process. The read operation of this written structure is performed by the current passing through BL. Independent sensing path with writing line is the main advantage of this approach. Nonetheless, in the write operation, a combination of two perpendicular currents results leads to the narrow write margin and half-selectivity issues. Moreover, in order to perform a proper write operation in FIMS, generating magnetic fields is require high currents,  $\sim 10$  mA, which limits the scalability of FIMS, due to the electromigration effect. To alleviate these issues, there are several solutions were proposed [50], however, the FIMS still suffers from low speed, large area overhead, and high power consumption.

Figure 2.5: FIMS approach for MTJ.

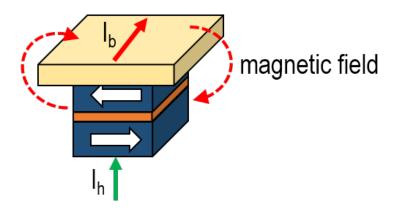

#### *Thermal-assisted switching (TAS)*

Thermal-assisted switching (TAS) improves the performance of the FIMS approach in terms of power consumption and thermal stability [15], as shown in Figure 2.6. Its concept is that a current

flowing through MTJ heats the magnetic free layer and reduces greatly the required switching field [51]. Similar to the FIMS structure, two orthogonal current lines are applied to achieve write selectivity; However, one line  $(I_h)$  is used to heat the MTJ FL and the other  $(I_b)$  is used to generate the switching field. This approach promises relatively lower power, higher density, and higher thermal stability compared with the pioneering FIMS approach. Nevertheless, due to the heating and cooling processes, TAS has a lower operation speed than FIMS.

Figure 2.6: TAS approach for MTJ.

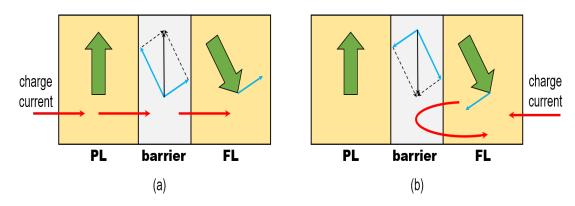

#### *Spin-transfer Torque (SST)*

In addition to the aforementioned switching approaches, magnets can be switched with spin-torque induced by applying spin-polarized current. This spin-polarized current can be produced using a spin-polarizer (PL) or leveraging spin-Hall effect (SHE) [1, 52]. This non-magnetic field switching idea was fulfilled by Berger and Slonczewski [13] to eliminate the drawbacks of FIMS and TAS. While electrons flow from the PL to FL, they are spin-polarized by the PL and acquire a spin angular momentum nearly aligned to the PL magnetization. After these spin-polarized electrons pass into the FL, their transverse angular momentum must be transferred to the FL magnetization due

to the conservation of angular momentum. Once the amount of electrons exceeding the threshold value, critical current, the spin-transfer torque (STT) exerted by the current will switch the magnetization of the FL to parallel with respect to the PL. If the charge current flows along the opposite direction, they will be spin-polarized against the PL magnetization by the reflection from the RL. In this case, the magnet is switched to AP state by the STT. Figure 2.7 illustrates the principle of STT switching.

Figure 2.7: Spin-transfer torque concept, (a) if electrons flow from the PL to FL, the magnet is switched to P state, and (b) if electrons flow from the FL to PL, the magnet is switched to AP state.

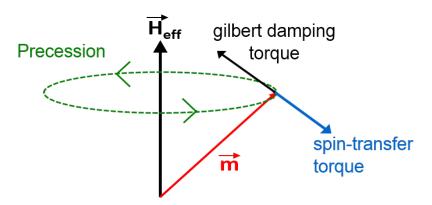

To understand the STT-induced magnetization switching, the FL magnetization is abstracted to a unit magnetic moment  $\vec{m}$  under the macrospin approximation. Then the dynamics of magnetization switching can be described by a Landau-Lifshitz-Gilbert (LLG) equation [53] including the STT, as:

$$\frac{\partial \vec{m}}{\partial t} = -\gamma \mu_0 \vec{m} \times \vec{H}_{eff} + a \left( \vec{m} \times \frac{d\vec{m}}{dt} \right) - \frac{\gamma \hbar J P}{2e t_{or} M_s} \vec{m} \times (\vec{m} \times \vec{m}_r)$$

(2.6)

where  $\vec{H}_{eff}$  is the effective magnetic field, which is the sum of different magnetic fields, such as the external magnetic field, the demagnetization field and the anisotropy field.  $\gamma$  is the gyromagnetic ratio.  $\mu_0$  is the permeability in the free space. a is the Gilbert damping constant.  $\hbar$  is the reduced Planck constant, P is the spin-polarization, e is the elementary charge,  $t_{ox}$  is the FL thickness,

$M_s$  is the saturation magnetization,  $\vec{m}$  is the unit vector along the PL magnetization, J is the write current density. Three torques are introduced in Equation 2.6, which are shown in Figure 2.8 [54, 55]. The first torque is the field-induced torque which causes the magnetic moment to process around the effective magnetic field. The second torque is the Gilbert damping torque which relaxes the precession. The final torque term is the STT, which is proportional to the charge current density and due to the polarity of injected current, it can help or resist the Gilbert damping torque. For instance, if the applied current density is larger than the critical current density, the exerted STT can compensate the Gilbert damping torque and switches the FL magnetization. Due to the simplicity of STT implementation, scalability, lower read energy, and higher read speed than FIMS and TAS, it has become the main switching approach for two-terminal Spintronics devices including GMR [41, 56] and TMR devices [57, 58]. In this approach, the common path is utilized for both write and read operations, which can lead to accidental write operation during reading. Moreover, a significant incubation delay due to the pre-switching oscillation [16, 59] incurs high switching energy. Therefore, recently, SHE is proposed for 3-terminal spin-based TMR devices as an alternative, which provides separate paths for reading and write operations, while expending significantly less switching energy [18, 19, 60].

Figure 2.8: Magnetization dynamics for a magnet in the presence of STT.

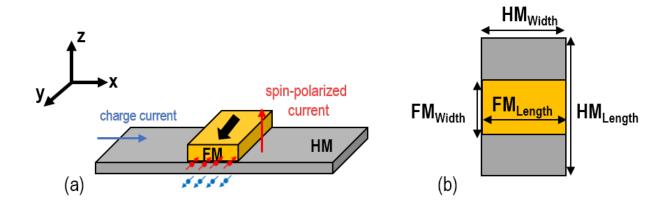

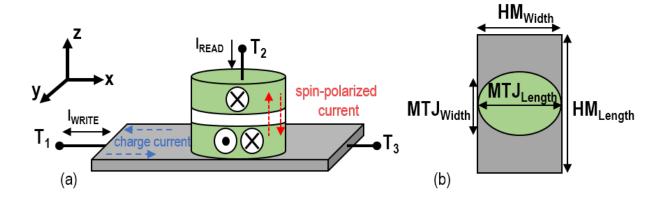

It is shown in [61] that a spin-polarized current, which is used to generate torque, can be produced in nanomagnetic devices by the spin-Hall effect (SHE) rather than passing charge current through an FM in spin polarizer approach. Figure 2.9 shows the spin-Hall effect phenomenon. The FM layer is directly connected to heavy metal (HM) which is normally made of  $\beta$ -tantalum ( $\beta$ -Ta) [1],  $\beta$ -tungsten ( $\beta$ -W) [62] or Pt [63]. By applying charge current to the left terminal of HM, electrons flow through an HM in  $\pm x$  direction. The spin-orbit coupling in HM deflects the electrons with different spins in opposite directions, which results in a spin injection current in the  $\pm z$  direction transverse to the applied charge current. This generated spin-polarized current exerts STT on the above FM and based on the direction of the injected charge current the FM magnetization can be switched to P or AP states, as shown in Figure 2.9. Ratio of the injected spin current to the applied charge current, called spin Hall injection efficiency (SHIE), is defined by Equation 2.7:

$$SHIE = \frac{I_S}{I_C} = \frac{A_{FM}}{A_{HM}} \times \sigma\theta_{SH}$$

(2.7)

where  $A_{FM}$  and  $A_{FM}$  are the cross-sectional areas of the HM, and the adjacent FM area, respectively.  $\theta_{SH}$  is the spin Hall angle, the ratio of generated spin current density to the applied charge current density, and  $\sigma$  is the electron spin polarization. If the right side of the above equation is larger than 1, then the spin-polarized current is larger than the charge current. Due to the difference in scattering ratio of electrons at the HM and FM interface, the spin-transfer efficiency in FM is lower than HM; Hence, the SHIE is larger than 1, which shows high efficiency for SHE usage. STT and SHE switching approaches for MTJ will be discussed in more details in the next chapters.

Figure 2.9: (a) Positive current along +x induces a spin injection current +z direction. The injected spin current produces the required spin torque for aligning the magnetic direction of the FM in +y directions, (b) Top view.

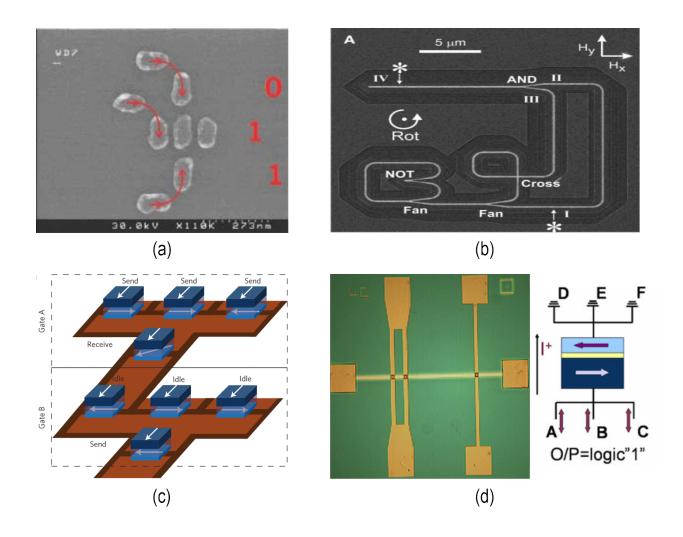

## Non-volatile spin-based logic

The potential of spin-based memories such as STT-MRAM is relatively well known, whereas realizing logic remains an open challenge. There are several magnetic-based logic architectures have been proposed, such as Magnetic Quantum-dot Cellular Automata (MQCA) [2, 64, 65, 66], Domain Wall Logic (DWL) [3, 67], All-Spin-Logic (ASL) [4, 68], and MTJ-based logics [69, 70, 5], as shown in Figure 2.10. MQCA consists of multiple nanomagnets located closely and operates based on the states of applied inputs. DWL uses domain wall to store and compute information. ASL stores information using the spin of electrons of magnets and propagate the state using spin-polarized currents. MTJ-based designs are similar to MRAM in functionalities [5]. For all the architectures, magnetic field or spin-polarized current is utilized. Table 2.1 summarizes strength/limitation characteristics of the highly-used spin-based devices relative to CMOS.

Figure 2.10: Main magnetic logic architectures, (a) MQCA [2], (b) DWL [3], (c) ASL [4], and (d) MTJ-based logic cell [5, 6].

# **Intermittent Approaches**

Table 2.2 lists some of the prior efforts addressing the intermittency challenge facing energy-harvesting-powered designs. In [71, 72], a traditional *checkpointing* approach is utilized to ensure the accurate forward progress of computation, whereby any volatile execution context is proac-

tively preserved in Non-Volatile Memory (NVM) prior to anticipated periods of power failure. A checkpointing approach may suffer from internal and external inconsistencies after each power loss. Internal inconsistency occurs when the execution context is partially-retained in NVM, while external inconsistency arises when the power failure occurs between two checkpoints [73]. DINO [74] innovated a checkpointing-based approach that utilizes non-volatile versioning to retain memory consistency, as delineated in Table 2.2.

Table 2.1: Characteristics of enabling technologies. " $\checkmark$ " or "-" indicates strength/limitation relative to CMOS.

| Technology  |         | CMOS | MTJ        | SHE        | DWL        | ASL        | NML       |  |

|-------------|---------|------|------------|------------|------------|------------|-----------|--|

| Attributes  |         |      |            |            | DWL        | ASL        | 1 414117  |  |

|             | Static  | 0    | <b>√</b> √ | <b>√</b> √ | <b>√</b> √ | <b>√</b> √ | <b>√√</b> |  |

| Power       | Dynamic | 0    | -          | -          | -          | -          | -         |  |

|             | Write   | 0    | -          | 0          | -          | -          | -         |  |

| Memory      |         | 0    | ✓          | ✓          | ✓          | -          | -         |  |

| logic       |         | 0    | -          | -          | -          | ✓          | <b>√</b>  |  |

| Density     |         | 0    | ✓          | ✓          | ✓          | ✓          | <b>√√</b> |  |

| Speed       |         | 0    | -          |            | _          | -          | -         |  |

| Reliability |         | 0    | ✓          | <b>√</b> √ | ✓          | -          | -         |  |

Duty Cycling with Scheduling [75, 76] offers another approach for tolerating intermittence. In this method, critical states of the processor will be partially-retained before the power failure, then the device will enter an extremely-low power mode. However, this results in full availability of the device only when a power interruption is unlikely, which can incur relatively long sleeping periods due to the inevitable power outages in many energy harvesting-powered systems. Chain [77] is another model for programming intermittent devices, in which forward-progress is ensured at the task granularity level. It utilizes *idempotent processing* concepts to make tasks restartable that never experience inconsistency to keep NVM consistent. In [32], a Non-Volatile MIPS Processor (NVP) is introduced in which specific blocks such as register files and pipeline registers were replaced by non-volatile elements. As listed in the last row of Table 2.2, NVP utilizes a checkpointing

approach to retain the processor volatile states resulting in possible above-mentioned internal and external inconsistencies in non-volatile elements. Advancing beyond previous intermittent processors which utilize NVM resources that are distinct from the processing datapath, we propose a new paradigm for energy-harvesting-powered processing, referred to as *Elastic Intermittent Computing* (EIC).

Table 2.2: Selected previous works with significant contributions towards intermittent processor design.

| Approach      | Methodology                                                 | Features                                                                                                           | Robust Element              | Challenges                                                                                                       |

|---------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------|

| Mementos [71] | checkpointing                                               | Run-time energy estimation<br>Periodic system snapshots<br>340 Byte footprint illustrated<br>VON = 4.5V, VOFF = 2V | Flash                       | New programming paradigms and Languages Data movement overhead Low endurance                                     |

| Hibernus [75] | duty-cycling<br>reactive<br>hibernating                     | Snapshot before outage 76%-100% less processing time and 49%-79% lower energy overhead than Mementos               | Ferroelectric<br>RAM (FRAM) | NVMs to save all processor register/states Need for sufficient energy to save a full snapshot Long sleeping time |

| DINO<br>[74]  | Checkpointing<br>Data versioning                            | 582 Byte footprint<br>illustrated<br>Atomic tasks<br>Reduced flow<br>complexity                                    | Ferroelectric<br>RAM (FRAM) | Large NVM versioning info New programming paradigm Data movement ~4KB average storage overhead                   |

| Chain<br>[77] | task-based<br>control flow<br>Channel-based<br>memory model | Idempotent tasks;<br>no checkpoints<br>2x to 7.6x performance<br>compared to DINO                                  | Ferroelectric<br>RAM (FRAM) | Hardware redundancy New programming paradigms 42% larger code than DINO ~8KB average storage overhead            |

| NVP<br>[32]   | PC/register store<br>Partial backup                         | NV flip-flops in MIPS ISA 1 KHz square waveform 3 MHz clk; 470nF store capacitor                                   | Ferroelectric<br>RAM (FRAM) | Non-volatile internal<br>and external coherence<br>Overhead of checkpointing                                     |

# CHAPTER 3: COMPACT MODEL OF STT/SHE FOR BOTH IMTJ AND PMTJ

As mentioned in previous chapters, spintronic devices show promising features such as non-volatility. Hence, in order to design, analyze and compare the performance of spin-based devices with previously proposed architectures, a compact model is required. Moreover, as presented in Chapter 2, STT/SHE MTJs are the most promising components for spin-based designs. Hence, in this chapter, a SPICE-compatible model for both STT-MTJ and SHE-MTJ is developed. A number of realistic material parameters and physical models have been integrated into the models to achieve good agreement with experimental measurements. Our model consists of two sub-models: (1) MTJ resistive behavior, and (2) STT switching model.

## Compact Model Of STT-MTJ

We considered NiFe/MgO and CoFeB/MgO stack for IMTJ and PMTJ, respectively, to gain the best performance of write and read operations.

#### MTJ Resistive Model

The tunneling conductance of barriers was proposed in [78], in which the conductance is voltage-dependent. [78] shows that the resistive behavior for this kind of structure, two ferromagnetic layers separated by a trapezoidal barrier, depends on its oxide barrier height and the effects between these layers. To simplify the proposed approximation, we considered that the oxide barrier is symmetric. Hence, simplified equations which are integrated into our model to calculate the

resistance of the MTJ are expressed as below [79]:

$$R_{MTJ} = \frac{t_{ox}}{Factor \times Area\sqrt{\phi}} \cdot exp(1.025 \times t_{ox}\sqrt{\phi})$$

(3.1)

where  $t_{ox}$  is the oxide thickness of MTJ, Factor is obtained from the resistance-area product value of the MTJ that relies on the material composition of its layers, Area is the surface of MTJ, and  $\phi$  is the oxide layer energy barrier height. The energy barrier between P and AP configurations of MTJ is in a range such that it can switch between configurations, while also retaining thermal stability. The energy barrier for IMTJ and PMTJ are expressed by the following equations [80]:

$$E_{IMTJ} = \frac{\mu_0 M_s V H_C}{2} \tag{3.2}$$

$$E_{PMTJ} = \frac{\mu_0 M_s V H_K}{2} \tag{3.3}$$

The V is the volume of the free layer, Ms is the saturation magnetization,  $H_C$  is the in-plane coercive field, and  $H_K$  is the perpendicular magnetic anisotropy field. Since  $H_K$  is higher than  $H_C$ , PMTJ provides high energy barrier which leads to higher thermal stability.

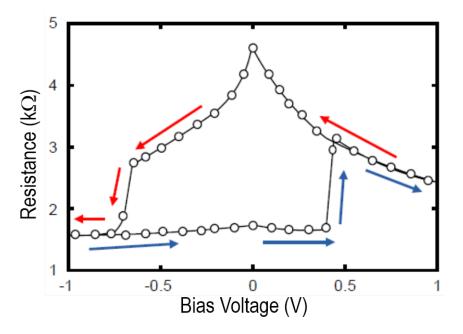

There are two different magnetization configurations for ferromagnetic layers, parallel (P) and antiparallel (AP), according to which MTJ resistance changes between RP and RAP, respectively. MTJ resistance is determined by the angle ( $\theta$ ) between the magnetization orientations of the fixed layer and free layer due to the tunnel magnetoresistance (TMR) effect. As previously mentioned, TMR is the primary aspect to perform the reading operation. In order to decrease read disturbance, in our design, TMR ration is set to 100% and 120%. In our model, we determine RMTJ as the resistance of the RP. The MTJ resistance in P ( $\theta$ =0°), and AP ( $\theta$ =180°) states is obtained and

expressed by the Equation 3.4 [81].

where  $V_b$  is the bias voltage, and  $V_h = 0.5$ V is the bias voltage when TMR is half of the TMR<sub>0</sub>. Figure 3.1 depicts a large resistance hysteresis of an MTJ by sweeping the bias voltage, which makes MTJ-based devices suitable for non-volatile designs.

Figure 3.1: Resistance hysteresis of an MTJ, red arrow shows switching from AP to P, while blue arrow indicates switching from P to AP.

## Spin-Transfer Torque (STT) Switching Model

Herein, first, we explain the required critical current for both MTJ types and then use them to calculate the switching delay for switching between P and AP states. As aforementioned, the magnetic direction of MTJ layers can be in the film plane, IMTJ (in-plane MT), or PMTJ (out of the film plane referred to as perpendicular MTJ) structure, as shown in Figure 3.2 (a) and (b), respectively. Equations 3.5 and 3.6 express the switching critical current for IMTJ [82] and PMTJ [83], respectively.

$$I_{c-IMTJ} = \frac{2\alpha e M_s V \left(H_c + \frac{H_{eff}}{2}\right)}{q(\theta) P \hbar}$$

(3.5)

$$I_{c-PMTJ} = \frac{\alpha \gamma e M_s V H_K}{\mu_B g(\theta)} \tag{3.6}$$

The parameter  $\alpha$  is the magnetic damping constant,  $\mu_B$  is the Bohr magneton, P is the spin polarization percentage of the tunnel current,  $\gamma$  is the gyromagnetic ratio, e is the electric charge,  $\hbar$  is the reduced Planck's constant, and  $H_{eff}$  is the effective out-of-plane demagnetization field, which consists of external field, in-plane uniaxial magnetic anisotropy field, and out-of-plane magnetic anisotropy. The effective demagnetization field in IMTJ is approximately equal to the saturation magnetization, which is normally larger than the anisotropy field in PMTJ. Thus, switching current for PMA is smaller than that of the IMA devices. Moreover, spin polarization efficiency factor,  $g(\theta)$ , is a function of the angle between the free layer and fixed layer magnetization directions  $(\theta)$  and is obtained by the Equations 3.7 and 3.8 [83] for IMTJ and PMTJ devices, respectively.

$$g_{IMTJ} = \left[ -4 + \frac{(P^{-1/2} + P^{1/2}) \times (3 + \cos\theta)}{4} \right]^{-1}$$

$$g_{PMTJ} = g_{SV} \pm g_{tunnel}$$

(3.7)

$$g_{SV} = \left[ -4 + \frac{(P^{-1/2} + P^{1/2})^3 \times (3 + \cos\theta)}{4} \right]^{-1}$$

$$g_{tunnel} = \frac{P}{2(1 + P^2 \cos\theta)}$$

(3.8)

where  $g_{SV}$  is the spin polarization efficiency in a spin valve and  $g_{tunnel}$  is the spin polarization efficiency in tunnel junction nanopillars.

As explained in previous chapters, based on the STT approach, a bidirectional spin-polarized current ( $I_{MTJ}$ ) is required for switching MTJ nanomagnet configuration, as shown in Figure 3.2. Electrons that flow through the MTJ free layer will experience an exchange field which aligns the spin of the electron with the magnetization direction of the nanomagnet. This phenomenon is called spin-filtering effect. The conservation of the angular momentum results in the exertion of an opposite sign torque with the equal magnitude on the free layer which eventually changes its magnetization direction. The P or AP configuration of the MTJ is determined by the direction of the current that flows through it. The required bidirectional current could be produced by means of simple MOS-based circuits. Due to the vertical structure of the MTJ, it can be readily integrated at the back-end process of the CMOS fabrication [84, 12]. According to the relative amplitude of the IMTJ and the switching critical current ( $I_C$ ), STT switching behavior can be categorized into two main regions: (1) precessional region ( $I_{MTJ}$   $I_C$ ), and (2) thermal activation region ( $I_{MTJ}$   $I_C$ ) which are described by Sun model [85] and Neél-Brown model [86], respectively.

In the precessional region, MTJ experiences rapid precessional switching. Equation 3.9 describes the switching duration of the MTJ in this region[84].

$$\frac{1}{\langle \tau_{STT} \rangle} = \left[ \frac{2}{C + \ln(\pi^2 \Delta)} \right] \frac{\mu_B P}{em(1 + P^2)} (I_{MTJ} - I_C)$$

(3.9)

where  $\tau_{STT}$  is the mean duration for the precessional switching region, C=0.577 is the Euler's constant,  $\Delta = E/(4k_BT)$  is the thermal stability factor, and m is the free layer magnetic moment. In the thermal activation region, although the current is less than the critical value, the switching can occur with a long input current pulse due to the thermal activation. The switching duration in the thermal activation region is described by the below equation [84]:

$$\frac{1}{\langle \tau_{STT} \rangle} = \tau_0 exp \left( \Delta \times \left( -\frac{I_{MTJ}}{I_C} \right) \right)$$

(3.10)

where  $\tau_{STT}$  is the mean pulse duration for the thermal activation region, and  $tau_0$  is the attempt period. In practice, in order to have high switching speed, MTJ is required to work in the precessional region with a current amplitude larger than critical current.

Figure 3.2: Illustrations (a) in-plane and (b) out-of-plane or perpendicular magnetized MTJ.

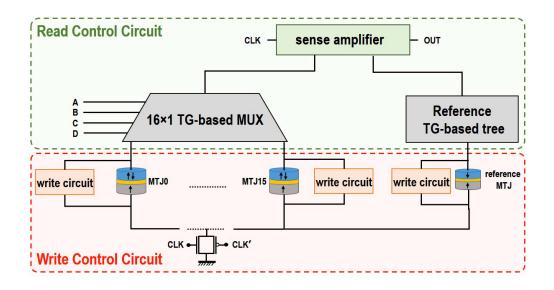

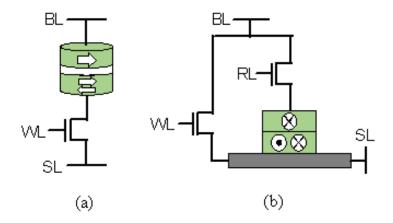

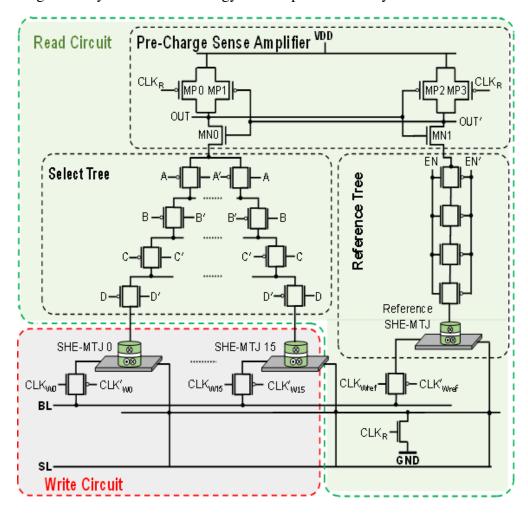

## STT-MTJ Based Look-Up Table

To validate our develop STT-MTJ model, a four-input STT-LUT, as shown in Figure 3.3, is introduced and its functionality is verified. It consists of read and write circuits. The write circuit includes two transmission gates (TGs), which provide the desired charge current for STT switching, whereas the read circuit is composed of a pre-charge sense amplifier (SA) [47], a TG-based multiplexer (MUX), and a reference tree. Each MTJ cell of LUT could be accessed according to the input signals A, B, C, and D, through MUX, which employs TGs instead of pass transistors (PTs). LUT is utilized in reconfigurable fabrics to implement combinational logic. In general, LUT is a memory with 2<sup>m</sup> cells in which the truth table of an m-input Boolean function is stored. Inputs can be considered as the address according to which corresponding output of the Boolean function will be returned.

The reference tree in read circuit is designed to provide SA with required reference resistance to properly sense each MTJ cell state. The reference tree consists of four TGs in a series configuration to compensate for the select tree active resistance. Reference MTJ resistance is designed in a manner such that its value in the parallel configuration is between low resistance, i.e.,  $R_P$ , and high resistance, i.e.,  $R_{AP}$ , of the LUT MTJ cells, as shown in the following equation:

$$R_{P-referenceMTJ} \cong \frac{1}{2}(R_P + A_{AP})$$

(3.11)

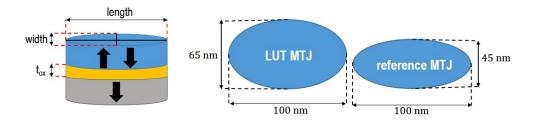

According to Equation 3.4, the resistance of MTJ can be altered by changing  $t_{ox}$  or Area. Oxide thickness could be only changed between 0.7 and 2.5 nm to keep the low-resistance value and show the TMR effect. Additionally, as established in [87], fabricating MTJs with various oxide thicknesses requires different magnetic processes, which leads to a significant increase in fabrication cost.

Figure 3.3: Four-input STT-LUT functional diagram.

Thus, in this brief, the other effective factor, i.e., Area, is examined to determine the desired value of reference MTJ resistance. The dimensions of LUT and reference MTJ cells are shown in Figure 3.4, according to which  $R_{PreferenceMTJ}$ ,  $R_{AP}$ , and  $R_{P}$  are equal to 1.8, 2.5, and 1.25 k $\Omega$ , respectively. The proposed design is simulated for LUTs with different numbers of inputs using SPICE simulator in 90-nm library. Delay and power consumption results are summarized in Table 3.1. As listed in the table, power and delay of STT-LUT are larger [88] when the MTJ state is P, due to the inequality shown in the following equation, which results in a longer time required for SA to be completely discharged:

$$R_{AP} - R_{P-referenceMTJ} > R_{P-referenceMTJ} - R_P \tag{3.12}$$

Herein, the developed STT-LUT circuit is implemented utilizing both PTs and TGs. The performances of our STT-LUT implementations are compared with SRAM-LUT [89] and two afore-

mentioned MTJ-based LUTs and summarized in Tables 3.1 and 3.2, respectively. The STT-LUT provides high-speed and ultra-low power circuits with improved PDP values, shown in the seventh row in Table 3.2. Furthermore, TG-based STT-LUT exhibits least PDP value while it leverages a larger number of MOS transistors compared with PT-based STT-LUT, which is the optimum choice from the area efficiency point of view.

Figure 3.4: Reference MTJ cell and LUT MTJ cell dimensions.

Table 3.1: performance comparison between STT-LUT and SRAM-LUT for four-input NAND operation.

| Parameter   |                     | SRAM-LUT [89] | PT-based STT-LUT [48] | TG-based STT-LUT [48] |

|-------------|---------------------|---------------|-----------------------|-----------------------|

| Area        |                     | 14.3×16.55    | 7.2×8.35              | 13.5×15.75            |

| Power       | Leakage             | 1.030         | 0                     | 0                     |

| Consumption | Consumption Dynamic |               | 4.30                  | 4.27                  |

| () Total    |                     | 2.247         | 4.30                  | 4.27                  |

| Delay (ps)  |                     | 85.86         | 94                    | 83                    |

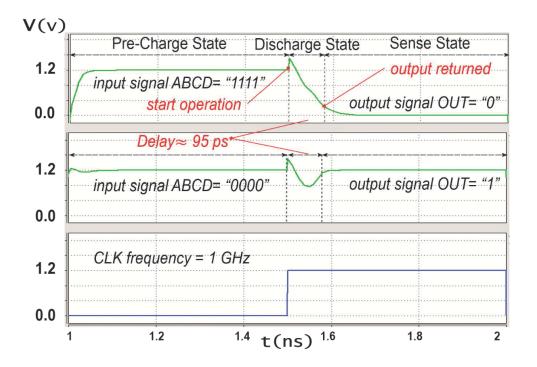

Figure 3.5 elaborates the functionality of the proposed STT-LUT for a four-input NAND operation when ABCD = "1111" and ABCD = "0000" inputs are applied. The former set of inputs selects MTJ15, which has a parallel configuration that denotes logic "0", whereas the latter input selects MTJ0 with antiparallel configuration representing logic "1".

Table 3.2: Performance comparison for four-input NAND operation.

| Eastung           | 7h a a [00] | C           | PT-based    | TG-based     |  |

|-------------------|-------------|-------------|-------------|--------------|--|

| Features          | Zhao [90]   | Suzuki [91] | STT-LUT[48] | STT-LUT [48] |  |

| NO. of MTJs       | 32          | 36          | 17          | 17           |  |

| NO. of MOSs       | 154         | 74          | 59          | 112          |  |

| Delay (ps)        | 88          | 81          | 94          | 83           |  |

| Active Power (µW) | 13.40       | 7.58        | 4.30        | 4.27         |  |

| PDP (p× $\mu$ W)  | 1179.2      | 613.98      | 404.20      | 354.41       |  |

| Standby Power     | 0           | 0           | 0           | 0            |  |

| PDP               | -           | 48%         | 65.7%       | 70%          |  |

| Improvement       | -           | -           | 34%         | 42%          |  |

While STT approach offers significant advantages in terms of read energy and speed, a significant incubation delay due to the pre-switching oscillation [16, 17] incurs high switching energy. Hence, to achieve a high-speed write operation, we can enlarge the write transistor width, or/and reduce the critical current. The former one leads to large area overhead and also increases risk of MTJ barrier breakdown. While the latter solution decreases the thermal stability. Recently, SHE-MTJ is introduced as an alternative for 2-terminal MTJs, which provides separate paths for read and write operations, while expending significantly less switching energy [18, 19, 20].

Figure 3.5: Transient response of STT-LUT for four-input NAND operation for (top) ABCD = "1111" and (middle) ABCD = "0000".

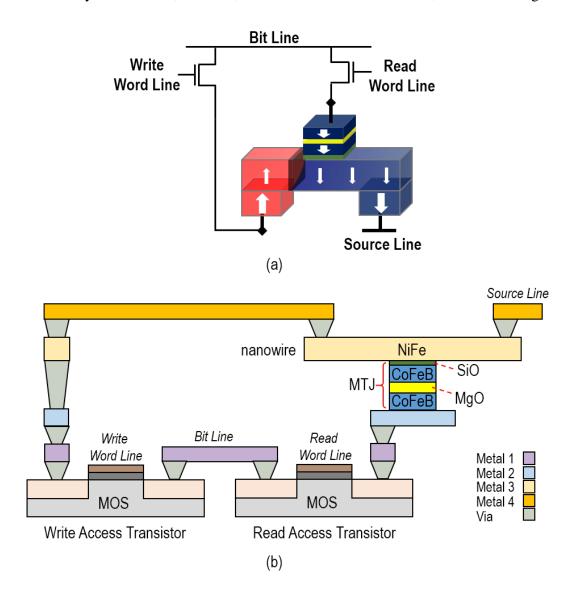

#### Compact Model Of SHE-MTJ

As mentioned, spin-polarized currents can be utilized to generate the torque required for switching the magnetization directions of the free layer in MTJs. It is shown in [1] that spin current can be produced in nanomagnetic devices by the spin-Hall effect. In [19], Manipatruni et al. have provided the physical equations of the three-terminal SHE-MTJ device behavior. Figure 3.6 shows the structure of the SHE-MTJ device, in which the magnetic orientation of the free layer changes by passing a charge current through a heavy metal (HM). MTJ free layer is directly connected to HM which is normally made of  $\beta$ -tantalum ( $\beta$ -Ta) [1],  $\beta$ -tungsten ( $\beta$ -W) [62] or Pt [63]. The MTJ

logic state that is defined by the free layer magnetic direction is determined by the direction of the applied charge current. The spin-orbit coupling in HM deflects the electrons with different spins in opposite directions, which results in a spin injection current transverse to the applied charge current. The injected current produces the required spin torque for aligning the magnetic direction of the free layer.

Ratio of the injected spin current to the applied charge current, called spin Hall injection efficiency (SHIE), is defined by Equation 3.13:

$$SHIE = \frac{I_{sz}}{I_{Icx}} = \frac{\pi . MTJ_{width}}{2HM_{thickness}} \theta_{SHE} \left[ 1 - sech\left(\frac{HM_{thickness}}{\lambda_{sf}}\right) \right]$$

(3.13)

where  $MTJ_{width}$  is the width of the MTJ,  $HM_{thickness}$  is the thickness of the HM,  $\lambda_{sf}$  is the spin flip length in HM, and  $\theta_{SHE}$  is the SHE angle [19]. This equation is valid for SHE-MTJ devices in which the length of the MTJ equals the width of the HM.

Figure 3.6: SHE-MTJ vertical structure. Positive current along +x induces a spin injection current +z direction. The injected spin current produces the required spin torque for aligning the magnetic direction of the free layer in +y directions, and vice versa. (b) SHE-MTJ Top view.

Herein, SHIE value is equal to 1.73 that is extracted using Equation 3.13. Thus, the generated spin current is larger than the applied charge current. Whereas the spin injection efficiency of a 2-terminal MTJ (STT-MTJ) is normally less than one resulting in a favorable write switching energy for SHE-MTJs used in LUTs herein, as quantified by Equation 3.13. The critical spin current required for switching the free layer magnetization orientation is expressed by Equation 3.14:

$$I_{s,critical} = \frac{2q\alpha M_S V_{MTJ} (H_k + 2\pi M_S)}{\hbar}$$

(3.14)

where VMTJ is the MTJ free layer volume. Thus, SHE-MTJ critical charge current can be calculated using Equations 3.13 and 3.14. Equation 3.15 shows the relation between SHE-MTJ switching time and the voltage applied to the HM terminals with the critical voltage  $v_c$  given by Equation 3.16 [19].

$$\tau_{SHE} = \frac{\tau_0 ln(\pi/2\theta_0)}{\left(\frac{v}{v_c}\right) - 1} \tag{3.15}$$

$$v_c = 8\rho I_c \left\{ \theta_{SHE} \left[ 1 - sech\left(\frac{HM_{thickness}}{\lambda_{sf}}\right) \right]_{length} \right\}^{-1}$$

(3.16)

where,  $\theta_0 = \sqrt{k_B/2E_b}$  is the effect of stochastic variation,  $E_b$  is the thermal barrier of the magnet of volume V,  $HM_{length}$  is the length of the HM, and  $I_c$  is the critical charge current for spin-torque induced switching. In order to model the SHE-MTJ, the HM resistance is also required, which is expressed by Equation 3.17, where  $\rho_{HM}$  is the electrical resistivity of HM.

$$R_{HM} = \frac{\rho_{HM} \times HM_{length}}{HM_{width} \times HM_{thickness}}$$

(3.17)

Verilog-AMS is utilized to model the behavior of SHE-MTJ devices based on the aforementioned physical equations. Then, the model is leveraged in SPICE circuit simulator to validate the functionality of the designed circuits using experimental parameters listed in Table 3.3.

Figure 3.7 (a) and 3.7 (b) show the MOS-based bit-cell of the 2-terminal MTJ (STT-MTJ) and 3-terminal MTJ (SHE-MTJ), respectively. In SHE-MTJ, the spin current can be significantly larger than the applied charge current. Therefore, the transistor utilized in the bit-cell of the STT-MTJ should be larger than that of the SHE-MTJ to be able to provide equal switching delay. Thus, although SHE-MTJ bit-cell requires two MOS transistors, its integration density is comparable to the STT-MTJs.

Table 3.3: Parameters of SHE-MTJ-based LUT.

| Parameter      | Description                                           | Value                                      |

|----------------|-------------------------------------------------------|--------------------------------------------|

| HM Volume      | $HM_{Length} \times HM_{Width} \times HM_{Thickness}$ | $100\times60\times3~nm^3$                  |

| MTJ Area       | $MTJ_{Length} \times HM_{Width} \times \pi/4$         | $60\times30\times\pi/4\ nm^2$              |

| MTJ Area       | Reference MTJ Surface                                 | $50 \times 25 \times \pi/4 \ nm^3$         |