# SOFT-ERROR RESILIENCE FRAMEWORK FOR RELIABLE AND ENERGY-EFFICIENT CMOS LOGIC AND SPINTRONIC MEMORY ARCHITECTURES

by

FARIS S. ALGHAREB B.S. University of Mosul, 2007 M.S. University of Mosul, 2009

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2019

Major Professor: Ronald F. DeMara

© 2019 Faris S. Alghareb

## **ABSTRACT**

The revolution in chip manufacturing processes spanning five decades has proliferated high performance and energy-efficient nano-electronic devices across all aspects of daily life. In recent years, CMOS technology scaling has realized billions of transistors within large-scale VLSI chips to elevate performance. However, these advancements have also continually augmented the impact of Single-Event Transient (SET) and Single-Event Upset (SEU) occurrences which precipitate a range of Soft-Error (SE) dependability issues. Consequently, soft-error mitigation techniques have become essential to improve systems' reliability. Herein, first, we proposed optimized soft-error resilience designs to improve robustness of sub-micron computing systems. The proposed approaches were developed to deliver energy-efficiency and tolerate double/multiple errors simultaneously while incurring acceptable speed performance degradation compared to the prior work. Secondly, the impact of Process Variation (PV) at the Near-Threshold Voltage (NTV) region on redundancy-based SE-mitigation approaches for High-Performance Computing (HPC) systems was investigated to highlight the approach that can realize favorable attributes, such as reduced critical datapath delay variation and low speed degradation. Finally, recently, spin-based devices have been widely used to design Non-Volatile (NV) elements such as NV latches and flip-flops, which can be leveraged in normally-off computing architectures for Internet-of-Things (IoT) and energy-harvesting-powered applications. Thus, in the last portion of this dissertation, we design and evaluate for soft-error resilience NV-latching circuits that can achieve intriguing features, such as low energy consumption, high computing performance, and superior soft errors tolerance, i.e., concurrently able to tolerate Multiple Node Upset (MNU), to potentially become a mainstream solution for the aerospace and avionic nanoelectronics. Together, these objectives cooperate to increase energy-efficiency and soft errors mitigation resiliency of larger-scale emerging NV latching circuits within iso-energy constraints. In summary, addressing these reliability concerns is

paramount to successful deployment of future reliable and energy-efficient CMOS logic and spin-tronic memory architectures with deeply-scaled devices operating at low-voltages.

Dedicated to my lovely family

# **ACKNOWLEDGMENTS**

I would like to thank my advisor, Prof. Ronald F. DeMara, for his strong support, guidance, and encouragement that truly guided me to achieve this dissertation. I really appreciate his passion and dedication to research and feel proud and fortunate to have worked with him throughout my graduate studies.

I extend my thanks to the Ph.D. dissertation committee members: Dr. Mingjie Lin, Dr. Sumit Jha, Dr. Cliff Zou, and Dr. Zixia Song for their time to evaluate the contents of this dissertation and provide valuable comments. I also would like to express my deep appreciation to Diana Camerino for her kind help throughout my course of study.

I would also like to acknowledge the financial support from the Ministry of Higher Education and Scientific Research in Iraq (MOHESR). Their support was fundamental for the completion of the Ph.D. program requirements; for that I am deeply grateful.

My sincere thanks are due to my family, relatives and friends for their continuous support, especially my mother, uncle Dr. Khamees, sister Dr. Nibras, and brother Dr. Safwan for their support, inspiration, and love that assisted making my dreams came true. Other brothers and sisters for their many years of support and love during my studies.

Finally, I would like to thank other students in CAL group. I really enjoyed working with all of you.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                                                   |

|-----------------------------------------------------------------------------------|

| LIST OF TABLES                                                                    |

| LIST OF ACRONYMS                                                                  |

| CHAPTER 1: INTRODUCTION                                                           |

| 1.1 Categories of Single-Event                                                    |

| 1.2 Soft Error Rate in Nanometer-scaled VLSI Devices                              |

| 1.3 Why Are Soft Errors Important? Needs for Soft-Error Resilience Logic Circuits |

| 1.4 FinFET Structure Devices                                                      |

| 1.5 Contributions of the Dissertation                                             |

| CHAPTER 2: LITERATURE REVIEW                                                      |

| 2.1 SER-Induced System Dependability Issues                                       |

| 2.1.1 Reliability at Multiple Abstraction Levels                                  |

| 2.1.2 Radiation-Induced Soft Errors                                               |

| 2.1.3 Sources of Variations                                                       |

| 2.2 Soft Errors in Logic Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.2.1 Logic Path Masking Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17         |

| 2.2.2 SET Characterizing and Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21         |

| 2.3 SER Mitigation Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26         |

| 2.3.1 Device-Level Mitigation Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28         |

| 2.3.2 Gate-Level Mitigation Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30         |

| 2.3.3 Circuit-Level Mitigation Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31         |

| 2.3.3.1 State of the Art Redundancy-based Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32         |

| 2.3.3.2 The Conventional Redundancy-based Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36         |

| 2.3.4 System-Level Mitigation Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47         |

| 2.3.4.1 Soft Error Masking for Other Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50         |

| 2.3.4.2 Multi-Bit Upsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51         |

| 2.4 SER Recent Trends and Technology Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55         |

| 2.4.1 Trends of Technology Scaling on SER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56         |

| 2.4.2 Trends of Voltage Scaling on SER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57         |

| 2.4.3 Trends of Multi-Gate FinFET Devices on SER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58         |

| 2.5. \$\cdot \cdot \ | <b>5</b> 0 |

| CHAPTER 3: TEMPORAL SELF-VOTING CHECKERS: ENERGY VS. RESILIENCE               |    |

|-------------------------------------------------------------------------------|----|

| TRADEOFFS                                                                     | 60 |

| 3.1 Energy-Efficiency vs Fault Resilience                                     | 60 |

| 3.2 The Proposed Approaches                                                   | 61 |

| 3.2.1 Temporal Self-Voting Logic (TSVL) Approach                              | 61 |

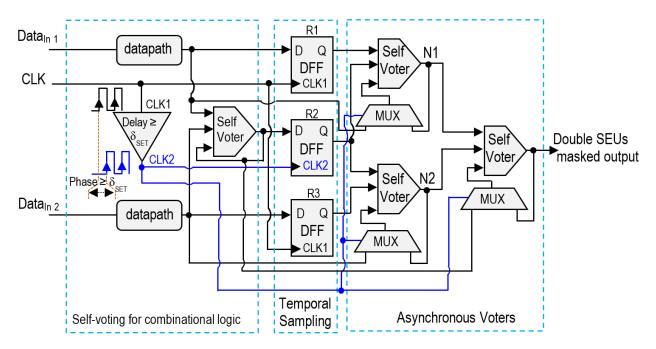

| 3.2.2 Hybrid Spatial and Temporal Redundancy Double-Error Correction Approach | 65 |

| 3.3 Experimental Results and Analysis                                         | 67 |

| 3.3.1 Quantifying Fault Resilience for Proposed Techniques                    | 67 |

| 3.3.2 Performance Evaluation for Proposed Techniques                          | 69 |

| 3.4 Summary                                                                   | 73 |

| CHAPTER 4: IMPACT OF PROCESS VARIATION IN THE NVT REGION ON SOFT              |    |

| ERROR RATE                                                                    | 74 |

| 4.1 Energy-Efficiency Through Near-Threshold Computing                        | 75 |

| 4.2 Trends of SER in NTV Region                                               | 76 |

| 4.3 Technology Scaling and PV Trends for SET                                  | 77 |

| 4.4 Experimental Setup                                                        | 79 |

| 4.4.1 Simulation Objectives, Tools and Workflow                               | 79 |

| 4.5 Experimental Results and Analysis                                         | 82 |

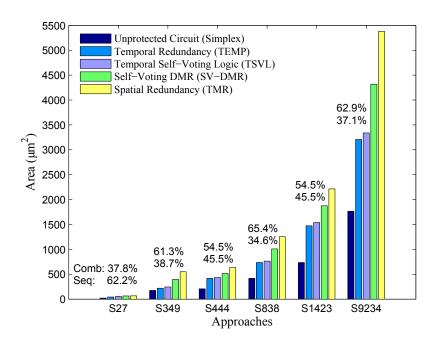

| 4.5.1 Quantifying Area Overhead for SE-Mitigation Techniques 82     |

|---------------------------------------------------------------------|

| 4.5.2 Comparison of Delay and Energy Consumption                    |

| 4.5.3 Impact of Process Variation in NTV Region                     |

| 4.5.4 Impact of Supply Voltage in NTV Region                        |

| 4.5.5 Constraints of Temporal Redundancy Approach                   |

| 4.6 Energy Efficency versus Fault Resiliency                        |

| 4.6.1 FCER Evaluation of Redundancy-based Approaches                |

| 4.6.2 Design and Analysis using FCER                                |

| 4.6.3 Evaluation of Fault Coverage                                  |

| 4.6.4 Summary of Fault-tolerant Design using FCER                   |

| 4.7 Relationship of Area and FCER                                   |

| 4.8 Design Diversity and Spatial Reduandancy                        |

| 4.9 Summary                                                         |

| CHAPTER 5: HIGH-PERFORMANCE DOUBLE NODE UPSET-TOLERANT NON-VOLATILE |

| FLIP-FLOP DESIGN                                                    |

| 5.1 Hybrid CMOS/Spintronics: Alleviating CMOS Challenges            |

| 5.2 Fundamentals of Magnetic Tunnel Junctions                       |

| 5.3 Technology Scaling Trends on Data Bit Upset                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|

| 5.4 Radiation-Induced Transient Faults Emulation                                                                             |

| 5.5 Proposed DNU-Tolerant NV Flip-Flop Circuit                                                                               |

| 5.5.1 Functionality Analysis of the Proposed NV Flip-Flop                                                                    |

| 5.6 Experiments and Results                                                                                                  |

| 5.6.1 Evaluation of Area, Power, and Delay Overheads                                                                         |

| 5.6.2 Evaluation of SEU and DNU Immunity                                                                                     |

| 5.7 Summary                                                                                                                  |

| CHAPTER 6: ENERGY-AWARE AND RELIABILITY-AWARE NON-VOLATILE SPIN-<br>TRONIC REGISTERS FOR RESILIENT ARCHITECTURAL STATE STOR- |

| AGE118                                                                                                                       |

| 6.1 Writing Mechanisoms for Switching the MTJs States                                                                        |

| 6.2 Soft Fault Coverage Analysis of Latching Circuits                                                                        |

| 6.3 Proposed Soft-Error Resilient NV-FF Designs                                                                              |

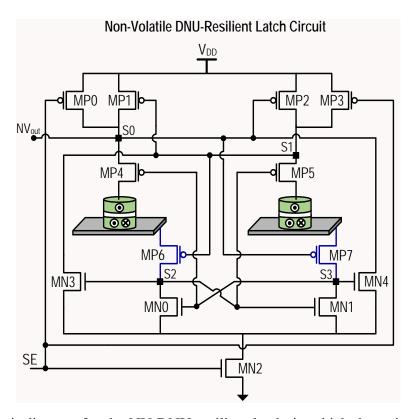

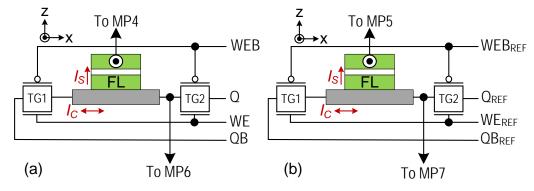

| 6.3.1 DNU-Resilient Non-Volatile Latch Circuit                                                                               |

| 6.3.2 SEU-Resilient Non-Volatile Flip-Flop Circuit                                                                           |

| 6.3.3 DNU-Resilient Non-Volatile Flip-Flop Circuit                                                                           |

| 6.4 Results and Discussion                                                                                                   |

| 6.4.1 Performance Analysis of Proposed Latching Circuits  | 134 |

|-----------------------------------------------------------|-----|

| 6.4.2 Performance Analysis of SEUR and DNUR NV-FF Designs | 135 |

| 6.5 Summary                                               | 138 |

| CHAPTER 7: CONCLUSION AND FUTURE WORK                     | 140 |

| 7.1 Technical Summary                                     | 140 |

| 7.2 Future Work                                           | 144 |

| APPENDIX: PERMISSION TO REUSE PUBLISHED MATERIAL          | 146 |

| LIST OF REFERENCES                                        | 152 |

# LIST OF FIGURES

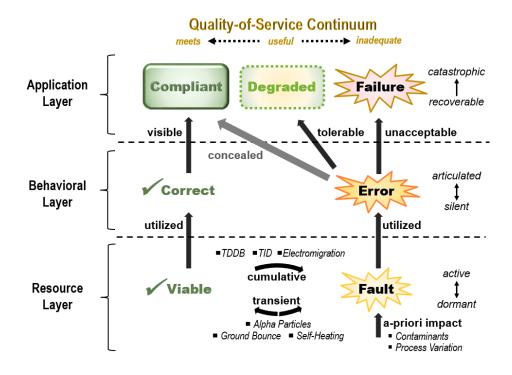

| 2.1  | Layered model of permanent and soft error sources and impacts                                                              | 11 |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

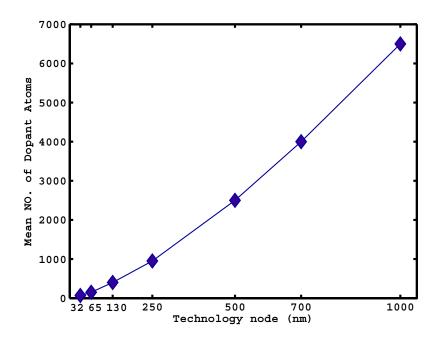

| 2.2  | Random dopant fluctuation as a function of technology generations [1]                                                      | 16 |

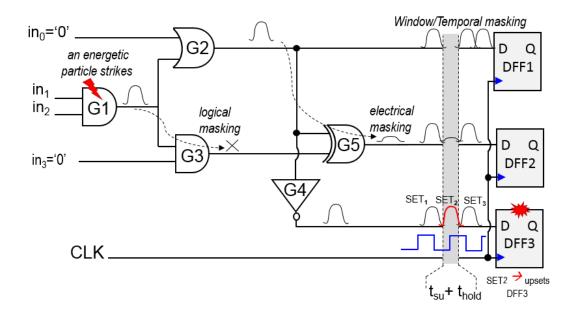

| 2.3  | An example of logic datapath masking mechanisms                                                                            | 18 |

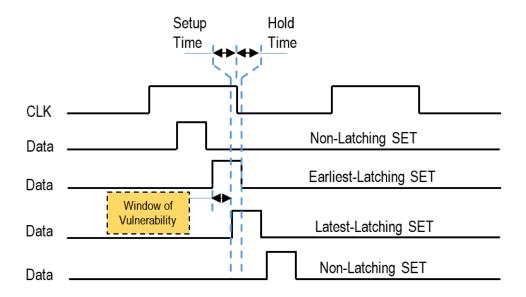

| 2.4  | SET latching window of vulnerability [2]                                                                                   | 20 |

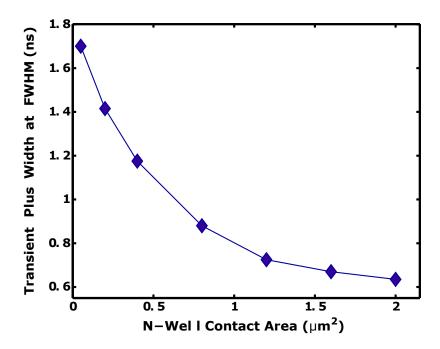

| 2.5  | Estimated maximum SET widths based on modifying the n-well contact size of the pMOS device for 90nm technology process [3] | 24 |

| 2.6  | Soft error rate of a logic and memory [1]                                                                                  | 27 |

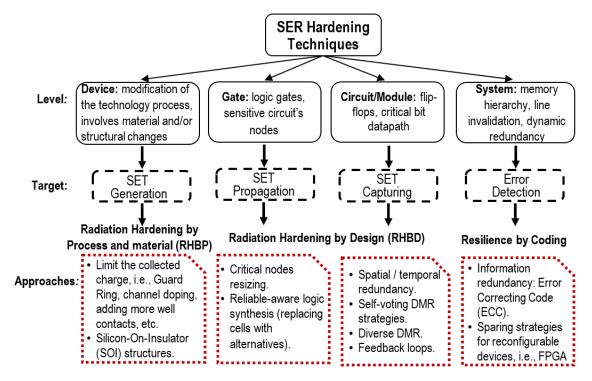

| 2.7  | Taxonomy of design levels for soft-error mitigation schemes                                                                | 29 |

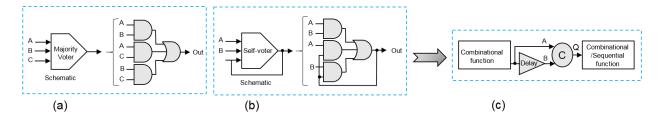

| 2.8  | Voting Circuits; (a) Majority voter circuit, (b) Self-voter circuit [4], (c) C-                                            |    |

|      | element in a temporal filter structure [5]                                                                                 | 37 |

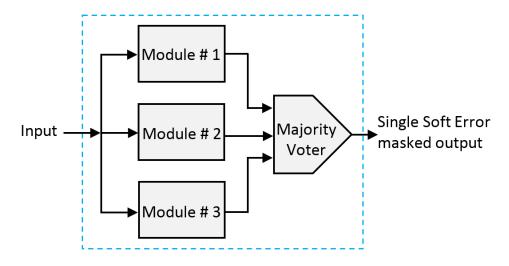

| 2.9  | Triple Module Redundancy (TMR) approach                                                                                    | 39 |

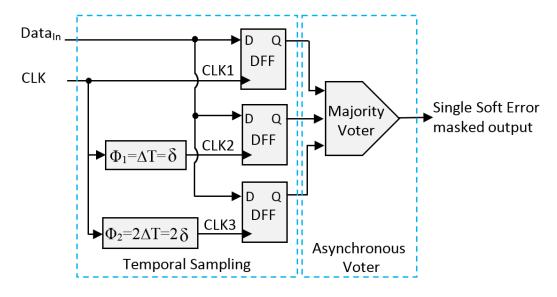

| 2.10 | Temporal redundancy approach [2]                                                                                           | 41 |

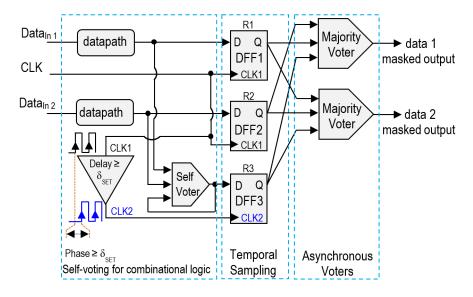

| 2.11 | Self-voting DMR logic circuit [4]                                                                                          | 43 |

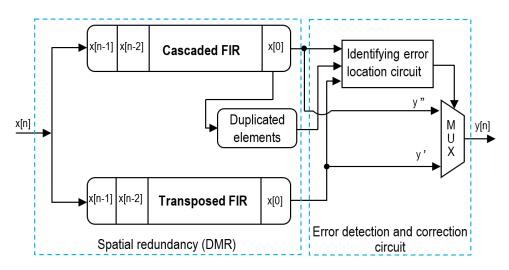

| 2.12 | Structural DMR design for FIR filter [6]                                                                                   | 46 |

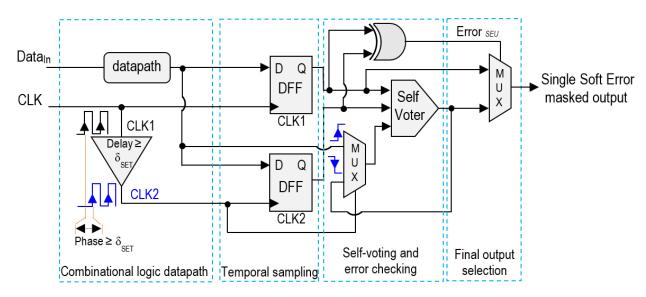

| 3.1  | Temporal Self-Voting Logic (TSVL) approach                                                                                 | 62 |

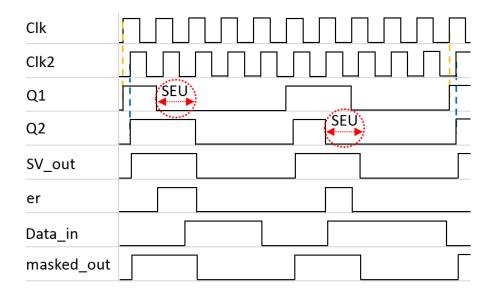

| 3.2 | Timing diagram of TSVL approach with SEU recovery occurred in the orig-      |    |

|-----|------------------------------------------------------------------------------|----|

|     | inal, $Q1$ , and redundant, $Q2$ , flip-flop consecutively, masked_out is an |    |

|     | <pre>inverse of data_in</pre>                                                | 63 |

| 3.3 | Hybrid Spatial and Temporal Redundancy Double-Error Correction approach.     | 65 |

| 3.4 | Area overhead evaluation of redundancy-based soft error masking techniques.  | 70 |

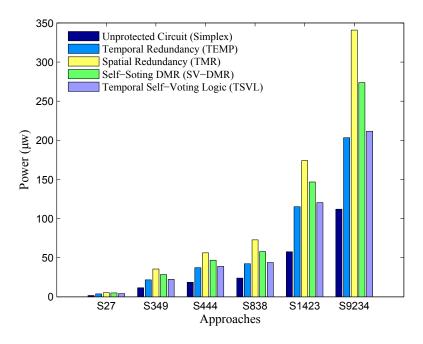

| 3.5 | Power consumption analysis of redundancy-based soft error masking techniques | 70 |

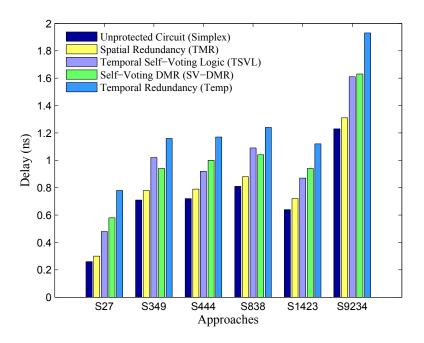

| 3.6 | Performance evaluation of redundancy-based soft error masking techniques     | 71 |

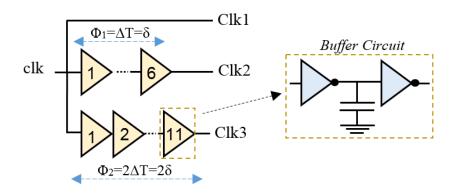

| 4.1 | Local Clock Manager (LCM) to generate CLK2 and CLK3                          | 80 |

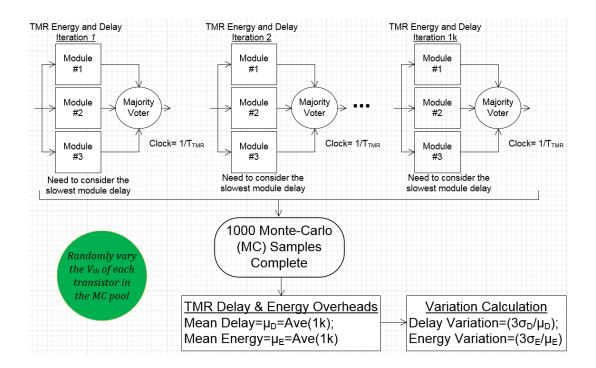

| 4.2 | Simulation framework developed to estimate the delay and energy for TMR.     |    |

|     | At least 1,000 samples are synthesized for each redundant system to conduct  |    |

|     | the statistical analysis                                                     | 82 |

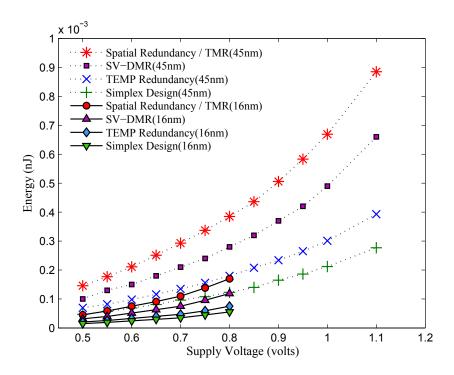

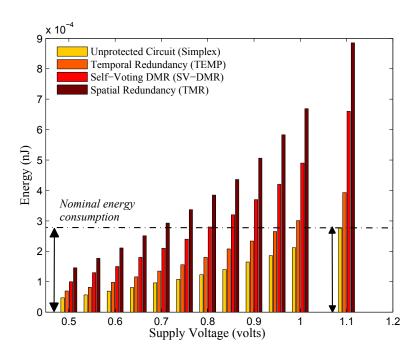

| 4.3 | Mean energy consumption for redundant systems using 45-nm and 16-nm          |    |

|     | technologies                                                                 | 83 |

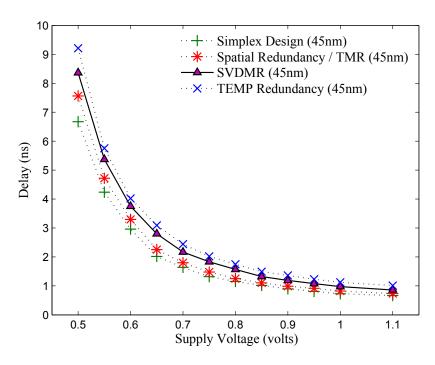

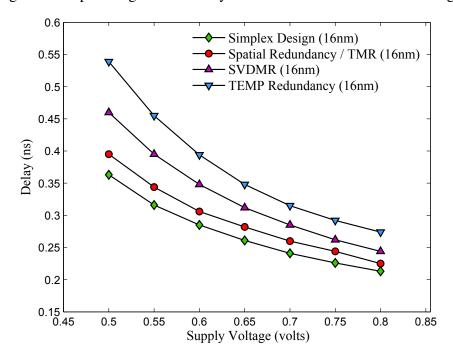

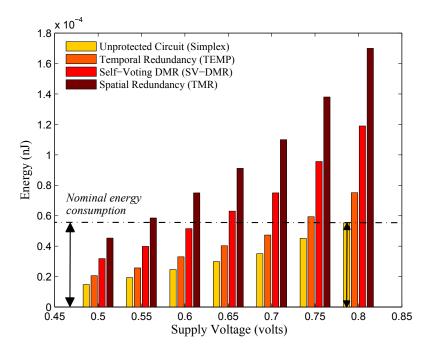

| 4.4 | Speed degradation analysis at NTV for the 45-nm technology                   | 85 |

| 4.5 | Speed degradation analysis at NTV for the 16-nm technology                   | 85 |

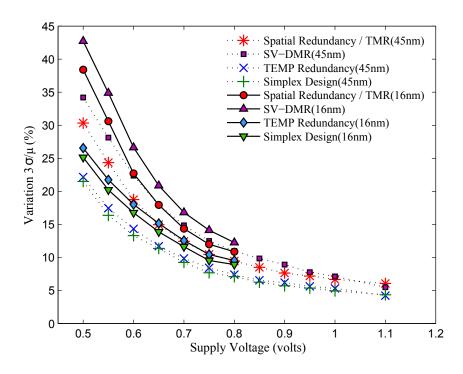

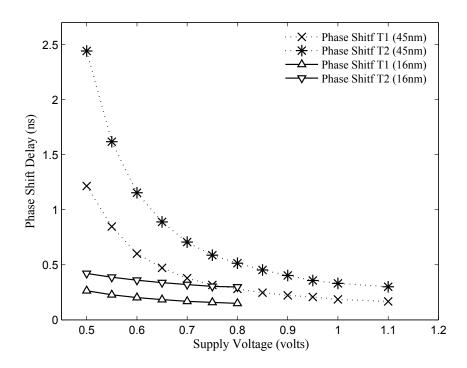

| 4.6 | Delay variation for redundant systems using 45-nm and 16-nm technologies     | 88 |

| 4.7 | Maintaining energy consumption at NTV using 45-nm technology process         | 90 |

| 4.8 | Maintaining energy consumption at NTV using 16-nm technology process         | 9( |

| 4.9  | SETS pulse width rejection at NTV for 43-nm planar MOSFET and tri-gate               |

|------|--------------------------------------------------------------------------------------|

|      | 16-nm bulk FinFET                                                                    |

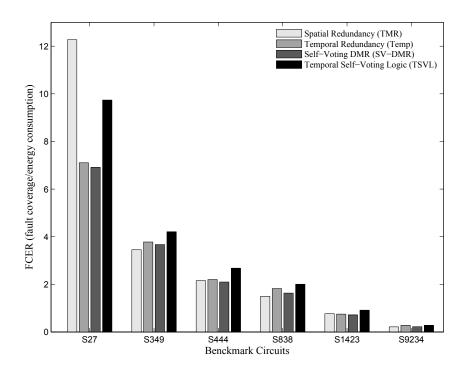

| 4.10 | Mean fault coverage energy ratio analysis for benchmark circuits realizing           |

|      | different redundancy-based approaches. Each point is obtained by average             |

|      | of FCERs obtained by scaling $V_{DD}$ from nominal level (1.1V) to the NTV           |

|      | region (0.5V) with decrements of 0.1V                                                |

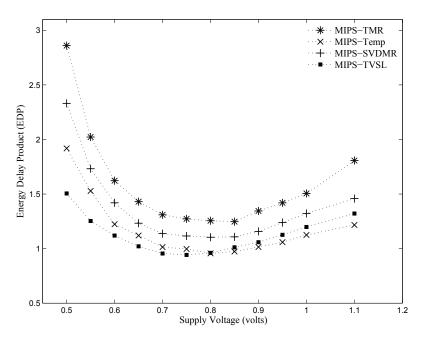

| 4.11 | Energy Delay Product (EDP) analysis with varying supply voltage for multi-           |

|      | ple redundant arrangements using a 32-bit 5-stage pipelined MIPS processor. 9        |

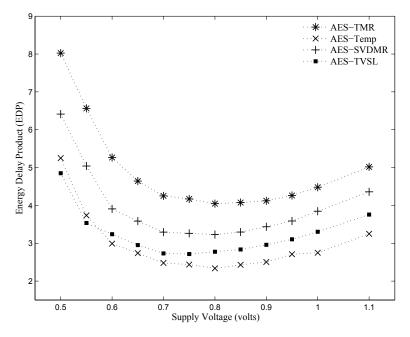

| 4.12 | Energy Delay Product (EDP) analysis with varying supply voltage for mul-             |

|      | tiple redundant arrangements using a 128-bit Advanced Encryption Standard            |

|      | (AES) algorithm                                                                      |

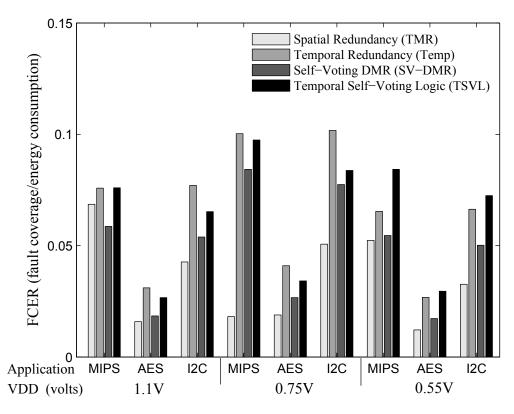

| 4.13 | Fault coverage energy ratio analysis of multiple application circuits protected      |

|      | using multiple redundancy-based approaches, ${\cal V}_{DD}$ is scaled from nominal   |

|      | level (1.1V) to the NTV region (0.55V)                                               |

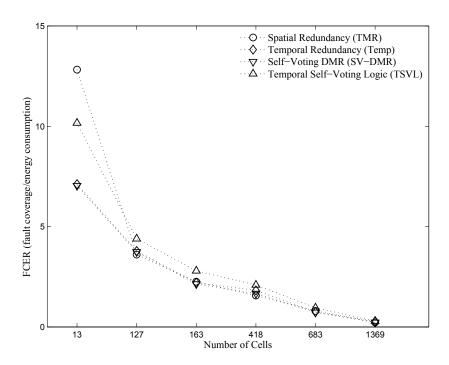

| 4.14 | Relationship between area (number of cells) and FCER for each benchmark circuit      |

|      | realized using multiple redundancy approaches, at nominal supply voltage ( $V_{DD}=$ |

|      | 1.1V)                                                                                |

| 5.1  | Spin transfer torque switching mechanism                                             |

| 5.2  | The proposed DNU-tolerant soft-error resilient nonvolatile flip-flop circuit 11      |

| 5 3  | Timing waveforms of the proposed DNII-tolerant NVFF                                  |

| 6.1 | (a) SHE-MTJ vertical structure, (b) SHE-MTJ top view                        |

|-----|-----------------------------------------------------------------------------|

| 6.2 | Circuit diagram for the NV DNU-resilient latch, in which the write circuits |

|     | have not been depicted for simplicity (refer to Figure 6.3)                 |

| 6.3 | Write circuit for (a) NV-latch's MTJ cell, (b) Reference MTJ cell 124       |

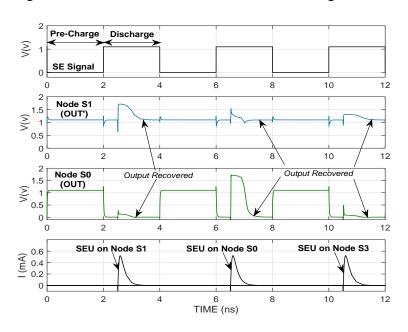

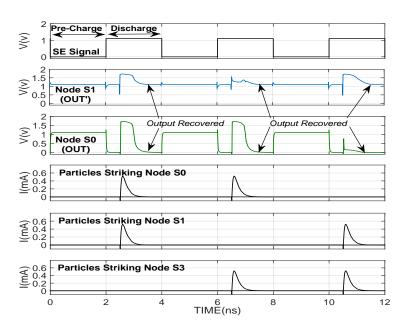

| 6.4 | Transient response of the proposed NV-latch to SEUs                         |

| 6.5 | Transient response of the proposed NV-latch to DNUs                         |

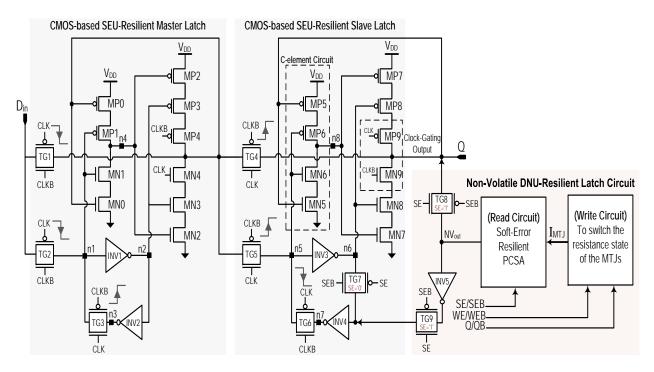

| 6.6 | Circuit diagram of the proposed high-performance shadow-based SEU-resilient |

|     | NV flip-flop                                                                |

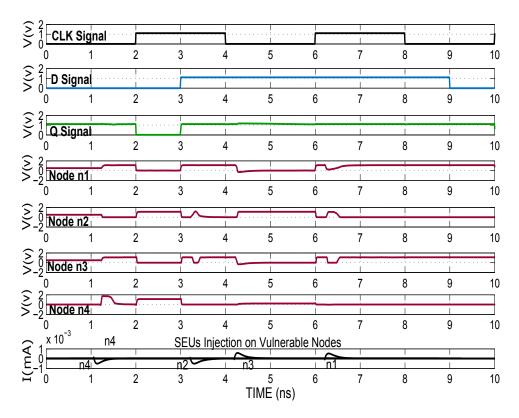

| 6.7 | Simulation waveforms for the proposed SEU-resilient latch when a transient  |

|     | fault strikes a sensitive node                                              |

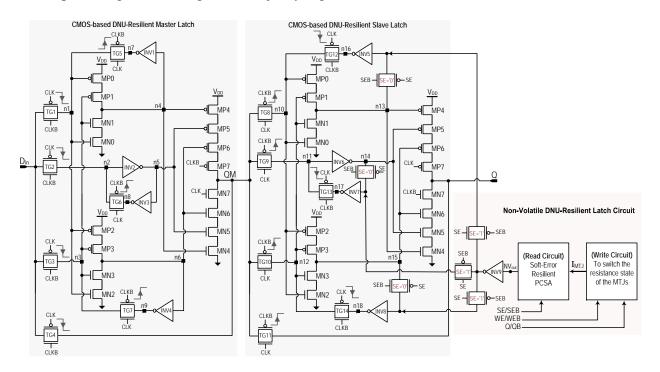

| 6.8 | Circuit diagram of the proposed high-performance shadow-based DNU-resilient |

|     | NV flip-flop                                                                |

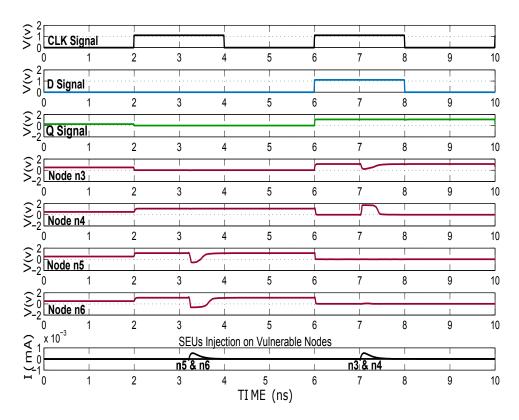

| 6.9 | Simulation waveforms for the proposed DNU-resilient latch design when       |

|     | transient faults hit double vulnerable nodes                                |

# LIST OF TABLES

| 1.1 | Trends of SER as impacted by technology scaling [7, 8]. However, vertical            |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | channel devices, i.e., FinFETs, can offer alternatives that achieve increased        |    |

|     | tolerance to SER for technologies beyond 22nm. For instance, Intel recently          |    |

|     | released its processors within 14nm technology node                                  | 5  |

| 2.1 | Categories of exposures facing highly-scaled CMOS logic circuit design               | 14 |

| 2.2 | Estimated maximum SET widths based on linear energy transfer (LET) [9];              |    |

|     | taking into concentration the effect of Propagation-Induced Pulse Broadening         |    |

|     | (PIPB) and without the effect of PIPB phenomena.                                     | 22 |

| 2.3 | Comparison of selected circuit-level protection techniques                           | 32 |

| 2.4 | SBU and MCU ratio trends under technology scaling [10]                               | 52 |

| 2.5 | Summary of SER mitigation techniques proposed at different abstraction               |    |

|     | design-level                                                                         | 54 |

| 2.6 | Comparison between design-level abstraction of SE-mitigation approaches,             |    |

|     | where by each ( $\checkmark$ , –) indicates relative (strength, limitation/weakness) | 55 |

| 3.1 | Possible error scenarios of HSTR-DEC approach; (NE = No Error; UE =                  |    |

|     | Upset Error).                                                                        | 66 |

| 3.2 | Fault coverage analysis of TSVL approach                                             | 68 |

| 3.3 | w.r.t. simplex design                                                                                         |

|-----|---------------------------------------------------------------------------------------------------------------|

| 4.1 | Mean energy reduction and speed degradation of temporal redundancy and SV-DMR approach versus TMR             |

| 4.2 | Mean energy consumption and speed degradation of spatial, temporal, and hybrid redundancy approaches          |

| 4.3 | Normalized speed degradation of spatial, temporal, and hybrid redundancy (SV-DMR) w.r.t. simplex design       |

| 4.4 | Effect of reducing supply voltage under iso-energy constraints                                                |

| 4.5 | Fault coverage energy ratio analysis of redundancy-based soft-error mitigation approaches.{FC=Fault Coverage} |

| 4.6 | Fault coverage energy ratio analysis of diverse-TMR arrangements 103                                          |

| 5.1 | Parameters of STT-MTJ devices                                                                                 |

| 5.2 | Performance penalties of the proposed NVFF circuit w.r.t. conventional CMOS-based flip-flop                   |

| 5.3 | Soft-error tolerance analysis of the proposed NVFF design                                                     |

| 6.1 | Parameters of SHE-MTJ devices [11, 12]                                                                        |

| 6.2 | Comparison of the proposed soft-error resilient latches and previously presented radiation-hardened designs   |

| 6.3 | Radiation-tolerance analysis of the proposed NV-FF Designs. {ML=Master- |     |  |  |

|-----|-------------------------------------------------------------------------|-----|--|--|

|     | Latch, SL=Slave-Latch, ShL=Shadow-Latch}                                | 136 |  |  |

| 6.4 | Performance comparison of the proposed NV-FFs                           | 137 |  |  |

# LIST OF ACRONYMS

AES Advanced Encryption Standard

ALU Arithmetic Logic Unit

**ASIC** Application-Specific Integrated Circuit

**BISER** Built-In Soft-Error Resilience

CLK Clock

**CMFs** Common Mode Failures

**CMOS** Complementary Metal Oxide Semiconductor

**DICE** Dual Interlocked-storage Cell

**DMR** Dual Modular Redundancy

**DNU** Double Node Upset

**DSP** Digital Signal Processing

**DVFS** Dynamic Voltage Frequency Scaling

**ECC** Error Correcting Code

**EDP** Energy Delay Product

FF Flip-Flop

FCER Fault Coverage Energy Ratio

**FinFETs** Fin-typed Field-Effect Transistors

**FIT** Failure In Time

**FPGAs** Field-Programmable Gate Arrays

**HPC** High-Performance Computing

**HSTR-DEC** Hybrid Spatial-Temporal Redundancy-Double Error Correction

LCM Local Clock Manager

**LET** Linear Energy Transfer

MBU Multi-Bit Upset

MTJ Magnetic Tunnel Junction

NMR N-Module Redundancy

**NTV** Near-Threshold Voltage

**NV** Non-Volatile

**PCSA** Pre-Charge Sense Amplifier

**PIPB** Propagation-Induced Pulse Broadening

PTM Predictive Technology Model

**PV** Process Variation

**RCC** Reinforcing Charge Collection

**RDF** Random Dopant Fluctuation

**RHBD** Radiation-Hardening By Design

**RHBP** Radiation-Hardening By Process

SDC Silent Data Corruption

**SE** Soft-Error

**SEE** Soft Error Effect

**SEMT** Single-Event Multiple Transients

**SER** Soft Error Rate

**SEFI** Single-Event Functional Interrupt

**SET** Single-Event Transient

**SEU** Single-Event Upset

SFC Soft Fault Coverage

**SHE** Spin Hall-Effect

**SOI** Silicon-On-Insulator

**STT** Spin Transfer Torque

**SV** Self-Voting

TDDB Time Dependent Dielectric Breakdown

**TG** Transmission Gate

**TID** Total Ionizing Dose

**TMR** Triple Module Redundancy

TSVL Temporal Self-Voting Logic

# **CHAPTER 1: INTRODUCTION**

This dissertation evaluates and presents the necessity for radiation-induced soft-error mitigation techniques of nano-electronic computing system architectures. As technology trends of Complementary Metal Oxide Semiconductor (CMOS) devices have improved the capability of contemporary processors. However, it has increased the susceptibility of VLSI circuits to transient faults. Thus, Soft Error Rate (SER) masking approaches are sought to increase reliability within area, speed, energy consumption, and fault masking resilience constraints. In this dissertation, energyefficient and cost-effective redundancy-based soft error mitigation techniques to achieve resilience in VLSI circuits and systems are proposed. In particular, resilient approaches are introduced to deal with radiation-induced transient effects, i.e., Single-Event Transient (SET) and Single-Event Upset (SEU), by carrying out tradeoffs between energy consumption and fault resilience. In addition, the effects of process variation at Near-Threshold Voltage (NTV) region on the redundancybased soft error mitigation approaches were investigated to leverage the technique that achieves an increased performance, satisfies the user specified objective metrics, within an iso-energy constraints. Whereas, the later part of this dissertation seeks to cover reliability of deeply-scaled hybrid CMOS/spintronic (MTJs) nonvolatile latching circuits, due to the radiation-induced soft errors in the CMOS-based logic portion that is utilized for read/write access operations. A study to completely and more efficiently address these transient effects to improve reliability will be conducted to make this emerging technology feasible. This chapter discusses the necessity and motivation for techniques presented in this dissertation, and concludes with a list of contributions to the state-of-the-art as a result of this work.

## 1.1 Categories of Single-Event

As Complementary Metal Oxide Semiconductor (CMOS) technology continues to scale towards fundamental physical limits, its immunity against charged particle strikes decreases significantly. This implies that the continued scaling of CMOS technology process reduces the quantity of critical charge,  $Q_{crit}$ , transistor's threshold voltage, a node capacitance, and the supply voltage ( $V_{DD}$ ). This gives rise to increase the susceptibility towards radiation-induced soft errors caused by numerous energetic particles, such as protons and heavy ions in space and alpha particles from packaging materials and cosmic rays neutrons at sea level [13]. Thus, soft errors at the chip level has become a major reliability challenge for VLSI designs [14]. In order to achieve high-reliability for contemporary computing systems, memory protection techniques, i.e., Error Correcting Code (ECC), have been utilized. However, such techniques are inadequate to completely and efficiently protect the reliability of VLSI circuits and systems operating at NTV. In particular, soft error effects (SEE) in logic circuits, i.e., latches/flip-flops and combinational logic, have become significant contributors to increase Soft Error Rate (SER) at the system-level [15, 16]. Therefore, it has become essential to ensure the integrity of logic paths by utilizing efficient soft-error mitigation techniques.

At the chip-level, various types of soft error effects can occur in CMOS logic circuits due to incident energetic particles, including 1) particles that hit inside combinational logic and generate a transient pulse, the Single-Event Transient (SET) [17], which propagates through downstream logic, and eventually it might be captured by a storage element, i.e., latch/flip-flop, thereby causing an upset, 2) energetic particles that strike node(s) inside a storage element to cause a Single-Event Upset (SEU) that flips the bit state in a DRAM memory cell or a SRAM-based register, resulting in a soft error, and 3) energetic particle strikes on global signal lines, such as control signals or instruction lines, can result in Single-Event Functional Interrupt (SEFI) that causes a temporary malfunction, i.e., interruption of normal operation [18], as the wrong instruction might

be executed. The corrupted data can be rewritten with new legitimate data and can circumvent the effect of incorrect state. When the physical device is not destructed, any such temporary glitches are considered to constitute soft errors. Altogether, these events can cause catastrophic failures in mission-critical applications. Thus, efficient protection schemes need to be evaluated with higher priority as moving towards NTC for energy-efficient operation.

#### 1.2 Soft Error Rate in Nanometer-scaled VLSI Devices

Practically speaking, soft errors occur when an energetic charged particle strikes a sensitive node of a circuit. This induces electron-hole pairs that cause charge/discharge at the struck transistor junction [19], which depends on the amount of charge collected at the node. The effect of such transient pulse depends on its duration, the state of the struck device (ON/OFF), and the type of struck node, i.e. drain side [20]. If the collected charge exceeds the critical amount of charge,  $Q_{crit}$ , then it produces some momentary charge and flips the voltage state of some circuit node(s), thereby causing a temporary glitch condition. The rate of these errors defined as Soft Error Rate (SER), which is a measurement metric that is used to evaluate the sensitivity of a digital circuit to transient and upset faults [17].

#### 1.3 Why Are Soft Errors Important? Needs for Soft-Error Resilience Logic Circuits

The revolution in chip manufacturing processes spanning five decades has proliferated high performance and energy-efficient nano-electronic devices across all aspects of daily life. In recent years, CMOS technology scaling has realized billions of transistors within large-scale VLSI chips to elevate performance. However, these advancements have also continually augmented the impact of SET and SEU occurrences which precipitate a range of Soft-Error (SE) dependability

issues [14, 21]. In the earlier technologies, soft errors were a major concern to the reliability of Integrated Circuits (ICs) for space applications. Moving forward to advanced technology node, the susceptibility of sub-micron electronics to radiation-induced transient effects has been of increased interest, and this phenomenon dominates the overall SER of large-scale logic circuits [1, 22]. In addition, the trend toward using smaller, denser, and faster CMOS devices has influenced logic circuits to experience larger leakage currents, thereby negatively impacting the reliability of deeply-scaled circuits by degrading their performance and robustness [23]. This is because the heat that results from large leakage currents can induce thermal noise, which can lead to bit upset in a memory element [24, 25]. Thus, as technology has advanced and transistors have become smaller, soft errors have become a major contributor to reliability issues at sea level [20].

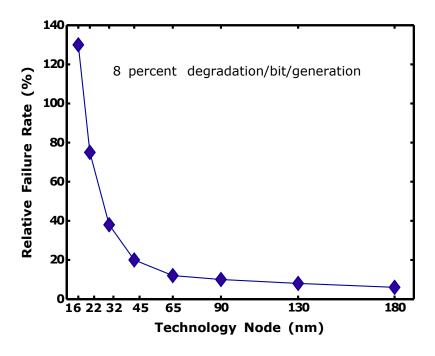

Taking all of these reliability-impacting factors into consideration, soft errors have been assessed to dominate a variety of failure mechanisms, whereby the SER might exceed the Failure In Time (FIT) metric [16,26,27]. As listed in Table 1.1, the SER of logic and memory per chip has increased 100-fold with technology scaling, especially for recent generations. In addition, due to the increasing integration density and growing complexity of ICs, the number of susceptible nodes to transients faults have increased. This leads to a higher SER that has recently been considered a serious concern for reliable memory and logic circuits [14, 28]. If such transient errors are not budgeted or compensated for, then the circuit can fail to perform correctly. Therefore, soft-error suppression becomes essential to improve the reliability of resilient systems operating in harsh environments like space, marine, military, and even in commercial applications [16, 20, 26, 29].

#### 1.4 FinFET Structure Devices

The High- $\kappa$ /Metal Gate (HK-MG) devices with vertical channels, i.e., the fin-typed Field-Effect Transistors (FinFETs) have been introduced to continue scaling and also show improved low-

leakage and high performance over planar MOSFET devices [30,31]. The tri-gate FinFET devices have been adopted by Intel at the 22nm technology node and beyond since they handle the problems of Short-Channel Effect (SCE) and provide more robust gate controllability than planar MOSFET devices, while offering improved switching characteristics for potential scalability beyond 10nm half-pitch [30,32,33]. Additionally, multi-gate bulk FinFET devices improve variations and thus the system's overall performance has significantly improved. Moreover, FinFET devices have exhibited higher tolerance to soft error effects, while being less prone to particle strikes compared to planar structure CMOS devices, thereby they have assisted in increasing the robustness of large-scale logic circuits [16,34]. In contrast, even though scaling the transistor volume helps in reducing the susceptible area, there exists an increased SER. This is due to two major factors including: the critical quantity of charge,  $Q_{crit}$ , of a node capacitance has aggressively diminished, while the other factor is that the density of integration is doubling the number of transistors per unit area over time, leading to an increased SER as low energy particles potentially can deposit an adequate amount of charge, i.e., sufficient Linear Energy Transfer (LET), to cause soft errors.

Table 1.1: Trends of SER as impacted by technology scaling [7,8]. However, vertical channel devices, i.e., FinFETs, can offer alternatives that achieve increased tolerance to SER for technologies beyond 22nm. For instance, Intel recently released its processors within 14nm technology node.

| Design Rule (nm) | SER<br>(Logic+Memory) | Total SER<br>(Data Center) | Chip Count  |

|------------------|-----------------------|----------------------------|-------------|

| 180              | 1                     | _                          | _           |

| 130              | 15                    | _                          | _           |

| 90               | 25                    | $10^{5}$                   | $10^{4.4}$  |

| 65               | 50                    | $10^{5.5}$                 | $10^{4.8}$  |

| 45               | 60                    | $10^{6.25}$                | $10^{5.3}$  |

| 32               | 75                    | $10^{7}$                   | $10^{5.7}$  |

| 22               | 90                    | $10^{7.5}$                 | $10^{6.15}$ |

| 16               | $10^{2}$              | $10^{8.8}$                 | $10^{6.75}$ |

#### 1.5 Contributions of the Dissertation

The dissertation's inspiration is partly to give an insight into the soft-error mitigation techniques and their challenges related to the design of reliable systems, to assist in selecting the proper technique for satisfying specific SER constraints. The main contributions of this dissertation are highlighted below.

Energy-efficiency vs fault resilience: In this work, a reliable and cost-effective, area and energy efficient, redundancy-based approaches have been developed to mitigate soft errors at the circuit/module-level. The proposed SE-tolerant techniques are able to tolerate both transient and upset faults and provide complete SEU protection, detection, and masking. The presented schemes impose comparable speed performance compared to the previously presented self-voting DMR hybrid redundancy approach. In addition, the proposed approach incurs reduced area overhead as compared to the conventional TMR, aside from its ability to tolerate double SEUs simultaneously. The efficacy of these approaches is quantified using Fault Coverage Power Ratio metric. This work is presented in Chapter 3.

Impact of PV at NTV on redundancy-based soft error mitigation techniques: The energy and performance costs, which are crucial design considerations due to prevalent use of low-voltage operation in current computing systems, were deeper investigated. In particular, detailed energy and performance tradeoffs of redundancy-based approaches for soft error mitigation in 16-nm non-planar FinFET and 45-nm planar CMOS structures are provided. For process variation, a comparison between 45-nm planar CMOS and 16-nm FinFET CMOS structure was carried out regarding energy-efficiency. Furthermore, the effects of both delay variation and technology node scaling on redundancy-based soft error mitigation techniques at NTV for iso-energy constraints have been revealed to depict the quantitative results. Additional important insight of this work was to identify and quantify the increase in energy cost of spatial redundancy at contemporary and future tech-

nology nodes such as 16 nm. Monte-Carlo simulation results demonstrate that energy-efficiency benefits of scaled technology devices (16-nm) as compared to 45-nm node due to increase in performance variations. The highlights of work presented in Chapter 4 are given below:

- 1. Assessing Resilience vs Area of Soft-Error Masking schemes: determining empirically the costs of spatial and temporal redundancy under the impact of technology scaling.

- 2. Evaluating the Energy and Delay Cost of Redundancy at NTV: determining the delay of redundant systems at NTV within a given energy budget.

- 3. Soft-Error Resilience Sensitivity to Process Variation: identifying the increased impact of  $\sigma V_{th}$  on alternative SER reduction strategies for 45-nm planar and tri-gate 16-nm bulk Fin-FET CMOS devices.

- 4. *Fault Coverage Energy Ration:* employing the FCER metric as an optimization parameter for design of resilient circuits, and its applicability to guide circuit synthesis algorithms while meeting performance goals.

- 5. *Design Diversity and Spatial Redundancy:* quantify the pros and cons of design diversity for redundancy-based soft error mitigation approaches.

**Soft-error resilient hybrid CMOS/spintronic STT-MTJ latching circuit:** Emerging spin-based devices are under intensive developments and investigations to improve their reliability. In this work, we design and evaluate soft-error resilience hybrid CMOS/spin-based latching circuit for nonvolatile high-performance applications. The proposed approach can achieve intriguing features, such as low energy consumption, high computing performance, superior soft error effects resilience, i.e., concurrently can tolerate MNU, to potentially become as a mainstream solution for the aerospace and avionic nanoelectronics.

**Soft-error resilient NVFF circuits for energy-aware and reliability-aware architectural state storage:** In this chapter, radiation hardening Non-Volitale Flip-Flop (NVFF) circuits are developed using spin-based devices that deliver reduced power dissipation and optimized CLK-to-Q delay, while achieving complete soft errors masking coverage for both SEUs and DNUs. It identifies the need for energy-aware and reliability-aware soft-error resilient latching circuits to improve soft errors masking robustness of emerging large-scale NVFF circuits while concurrently reducing its power dissipation to realize energy efficiency. Specifically, the contributions of chapter 6 are as follows:

- 1. Develop an NV-latch using Spin Hall Effect (SHE)-based Magnetic Tunnel Junctions (MTJs) that can tolerate multiple node upsets.

- 2. Design of low energy and high-performance SEU and DNU tolerant CMOS-based latches.

- 3. Develop four different NVFFs, which can be utilized in normally-off and NV computing architectures.

# **CHAPTER 2: LITERATURE REVIEW**

In this chapter, a wide range of resilient SER mitigation techniques that exploit specific attributes of different levels of a design for energy-savings to attain reliable protection capabilities are discussed. These techniques have been adopted to mitigate soft errors at different levels of abstraction. To highlight the characteristics of each technique and demonstrate the accuracy of soft error mitigation schemes, the protection techniques are categorized based on the design level of the protection scheme. The taxonomy of SER masking techniques relies on the Single Event Transient (SET) pulse generation at the device-level, propagation at the circuit-level, and capturing at the circuit/module-level. Also developed is a concise taxonomy for the sources of induced soft errors and variation. A comparison among the predominant mitigation schemes in terms of area, energy consumption, fault coverage, and design complexity is carried out to leverage the robustness of schemes that achieve the highest performance over the stated issues. Likewise, a review of the impact of technology and voltage scaling trends on the SER and its masking techniques are discussed. The inspiration of this survey chapter has been to provide a compendium of design insights for soft error mitigation techniques to identify the most efficient hardening schemes, in order to serve as a guide for researchers and designers of reliable CMOS circuits and systems.

## 2.1 SER-Induced System Dependability Issues

In the nanometric technologies, integrated circuits are associated with the diminishing of device feature size, massive growth in integration density, and lower supply voltages. Thus, these desirable attributes have raised the vulnerability of the integrated circuits to soft errors as they impose risks for terrestrial and space applications. Next, system reliability at different abstraction layers and the sources of transient and permanent faults are discussed.

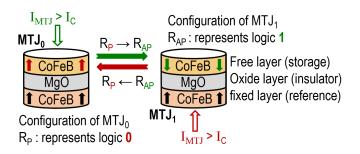

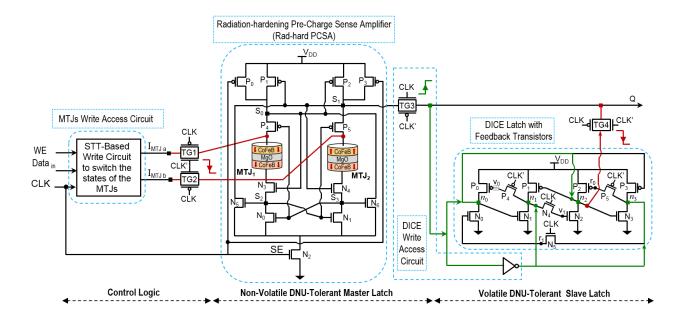

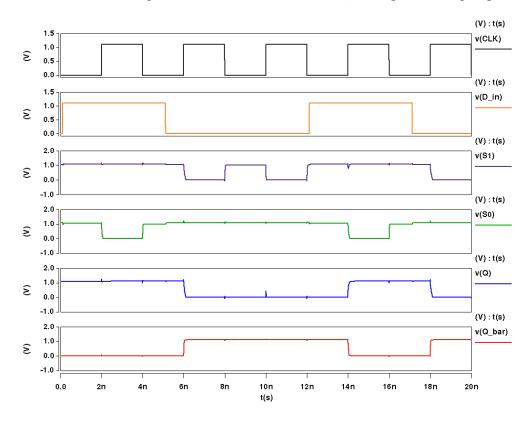

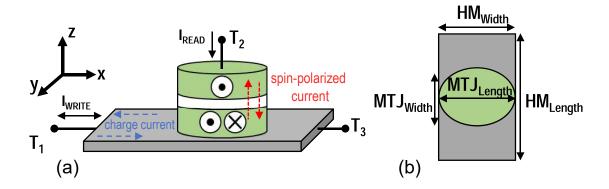

### 2.1.1 Reliability at Multiple Abstraction Levels