# A MULTI-LAYER FPGA FRAMEWORK SUPPORTING AUTONOMOUS RUNTIME PARTIAL RECONFIGURATION

by

HENG TAN

B.S. Dalian University of Technology, 2000

M.S. University of Central Florida, 2004

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Fall Term 2007

Major Professor: Ronald F. DeMara

© 2007 Heng Tan

#### **ABSTRACT**

Partial reconfiguration is a unique capability provided by several Field Programmable Gate Array (FPGA) vendors recently, which involves altering part of the programmed design within an SRAM-based FPGA at run-time. In this dissertation, a Multilayer Runtime Reconfiguration Architecture (MRRA) is developed, evaluated, and refined for Autonomous Runtime Partial Reconfiguration of FPGA devices. Under the proposed MRRA paradigm, FPGA configurations can be manipulated at runtime using on-chip resources. Operations are partitioned into Logic, Translation, and Reconfiguration layers along with a standardized set of Application Programming Interfaces (APIs). At each level, resource details are encapsulated and managed for efficiency and portability during operation. An MRRA mapping theory is developed to link the general logic function and area allocation information to the device related physical configuration level data by using mathematical data structure and physical constraints. In certain scenarios, configuration bit stream data can be read and modified directly for fast operations, relying on the use of similar logic functions and common interconnection resources for communication. A corresponding logic control flow is also developed to make the entire process autonomous.

Several prototype MRRA systems are developed on a Xilinx Virtex II Pro platform. The Virtex II Pro on-chip PowerPC core and block RAM are employed to manage control operations while multiple physical interfaces establish and supplement autonomous reconfiguration capabilities. Area, speed and power optimization techniques are developed based on the developed Xilinx prototype. Evaluations and analysis of these prototype and techniques are performed on a number of benchmark and hashing algorithm case studies. The results indicate

that based on a variety of test benches, up to 70% reduction in the resource utilization, up to 50% improvement in power consumption, and up to 10 times increase in run-time performance are achieved using the developed architecture and approaches compared with Xilinx baseline reconfiguration flow.

Finally, a Genetic Algorithm (GA) for a FPGA fault tolerance case study is evaluated as a ultimate high-level application running on this architecture. It demonstrated that this is a hardware and software infrastructure that enables an FPGA to dynamically reconfigure itself efficiently under the control of a soft microprocessor core that is instantiated within the FPGA fabric. Such a system contributes to the observed benefits of intelligent control, fast reconfiguration, and low overhead.

To my parents

#### **ACKNOWLEDGMENTS**

I would like to thank NASA, for their financial support and the opportunity to work with such advanced and exciting technology. I would like to thank Dr. DeMara, for his many technical and editorial suggestions that have helped shaping this work and his constant encouragement and support during the research. I would like to thank the committee members who have taken the time to review and comment on this dissertation. But most of all I would like to thank my parents, who raised me, give me unconditional love and constantly support and encourage me to pursue my dream even when I am far way from home, from my country.

# **TABLE OF CONTENTS**

| TABLE OF CONTENTS                                           | vii |

|-------------------------------------------------------------|-----|

| LIST OF FIGURES                                             | X   |

| LIST OF TABLES                                              | xii |

| LIST OF TABLES                                              | xii |

| CHAPTER 1: INTRODUCTION                                     | 1   |

| 1.1 Overview                                                | 1   |

| 1.2 Partial Reconfiguration Technology                      | 4   |

| 1.3 Need for Autonomous Partial Reconfiguration             | 6   |

| 1.4 Dissertation Outline                                    | 9   |

| 1.5 Contribution of Dissertation                            | 11  |

| CHAPTER 2: PREVIOUS WORK                                    | 13  |

| 2.1 Commercial Partial Reconfiguration Tools                | 13  |

| 2.2 Partial Reconfiguration Tools and Framework             | 16  |

| 2.3 Hardware Optimization Technique                         | 18  |

| 2.4 Software Control Optimization                           | 21  |

| 2.5 Chapter Summary                                         | 25  |

| CHAPTER 3: MULTI-LAYER RUNTIME RECONFIGURATION ARCHITECTURE | 26  |

| 3.1 Architecture Design Definition                          | 26  |

| 3.2 Hierarchical Architecture Design                        | 28  |

| 3.3 Dynamic Control Flow                                    | 34  |

| 3.3.1 Adopted Module Based Partial Reconfiguration Flow     | 36  |

| 3.3.2 Frame Based Partial Reconfiguration Flow          | 39 |

|---------------------------------------------------------|----|

| 3.3.3 Physical Area Management                          | 42 |

| 3.4 Logic Layer Application                             | 45 |

| 3.4.1 Low-Level Crossover Operator                      | 47 |

| 3.4.2 Low-Level Mutation Operator                       | 47 |

| 3.5 Chapter Summary                                     | 48 |

| CHAPTER 4: RECONFIGURATION AND VERIFICATION METHODOLOGY | 51 |

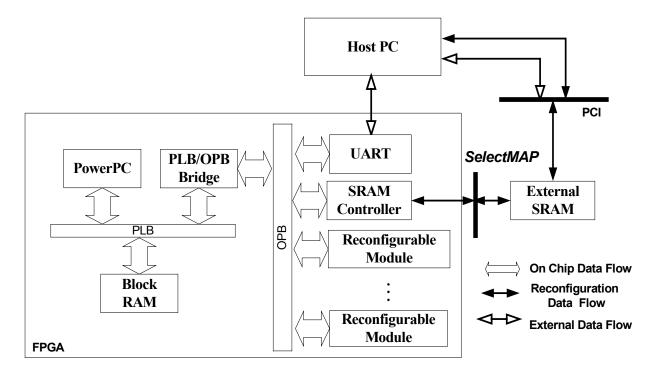

| 4.1 SelectMAP Based Methodology                         | 52 |

| 4.1.1 SelectMAP Interface                               | 52 |

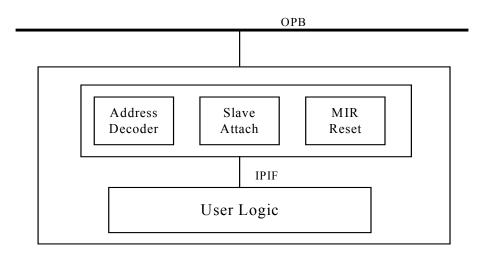

| 4.1.2 System Design                                     | 53 |

| 4.1.3 Testing Strategy and Communication Channel        | 56 |

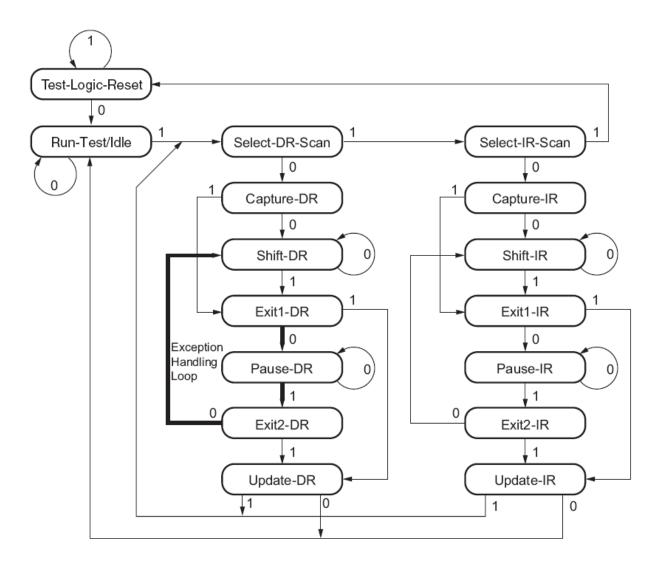

| 4.2 JTAG Based Methodology                              | 59 |

| 4.2.1 JTAG Interface                                    | 59 |

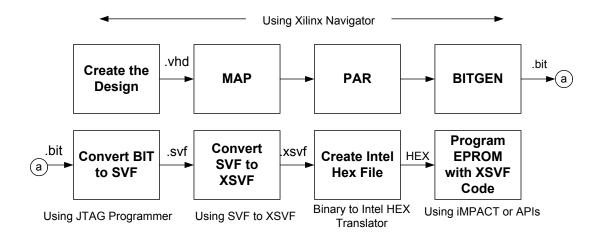

| 4.2.2 Reconfiguration Control                           | 62 |

| 4.2.3 Testing Strategy and System Design                | 64 |

| 4.3 ICAP Based Methodology                              | 70 |

| 4.3.1 ICAP Interface                                    | 70 |

| 4.3.2 System Design                                     | 72 |

| 4.3.3 Bit Manipulation and Reconfiguration Control      | 74 |

| 4.4 Chapter Summary                                     | 77 |

| CHAPTER 5: RESOURCE UTILIZATION AND TIMING ANALYSIS     | 79 |

| 5.1 Basic Application Case Study                        | 79 |

| 5.2 Resource Optimization Analysis                      | 83 |

| 5.3 Timing Analysis                                | 91  |

|----------------------------------------------------|-----|

| 5.3.1 Fundamental Timing Parameters                | 91  |

| 5.3.2 Translation Engine Evaluation                | 92  |

| 5.3.3 Timing Analysis                              | 96  |

| 5.4 Chapter Summary                                | 98  |

| CHAPTER 6: RECONFIGUARTION OPTIMIZATION TECHNIQUES | 101 |

| 6.1 Area and Bitstream Optimization                | 101 |

| 6.2 Application Analysis                           | 111 |

| 6.2.1 Data Structure Mapping                       | 111 |

| 6.2.2 Flexible Routing.                            | 113 |

| 6.3 GA Execution MRRA                              | 118 |

| 6.3.1 Performance Evaluation                       | 120 |

| 6.3.2 Results Analysis                             | 122 |

| 6.4 Chapter Summary                                | 124 |

| CHAPTER 7: CONCLUSION                              | 126 |

| 7.1 Summary                                        | 126 |

| 7.2 Future Work                                    | 130 |

| LIST OF REFERENCES                                 | 133 |

# LIST OF FIGURES

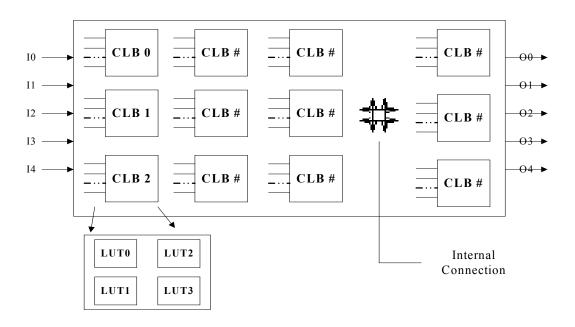

| Figure 1: FPGA architecture                                | 2  |

|------------------------------------------------------------|----|

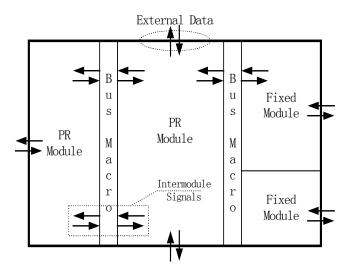

| Figure 2: Design Layout with Two Reconfigurable Modules    | 5  |

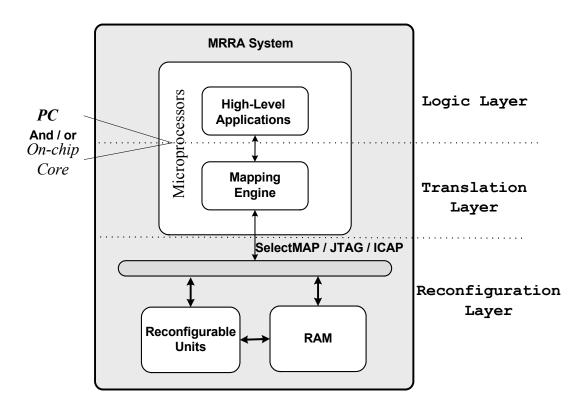

| Figure 3: Multi-layer Runtime Reconfiguration Architecture | 28 |

| Figure 4: LUT Representation at Logic Layer                | 29 |

| Figure 5: Translation Process Flow Diagram                 | 31 |

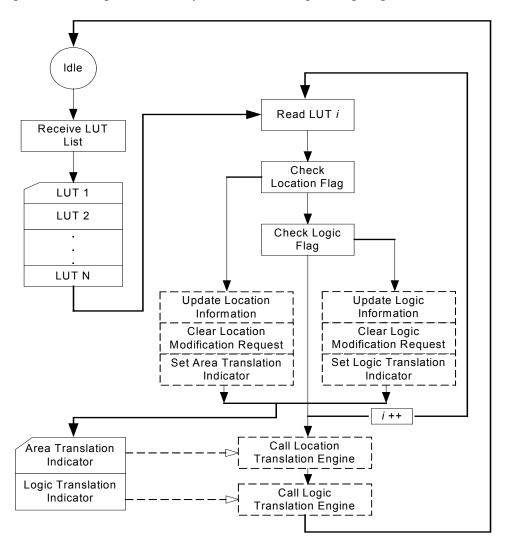

| Figure 6: Logic Control Flow                               | 34 |

| Figure 7: Module-Based Flow                                | 37 |

| Figure 8: A Simple Logic Modification Example              | 39 |

| Figure 9: Physical Area Management                         | 42 |

| Figure 10: SelectMAP based System                          | 54 |

| Figure 11: IPIF Template                                   | 55 |

| Figure 12: JTAG Control State Machine [80]                 | 61 |

| Figure 13: Programming Flow under JTAG Control.            | 62 |

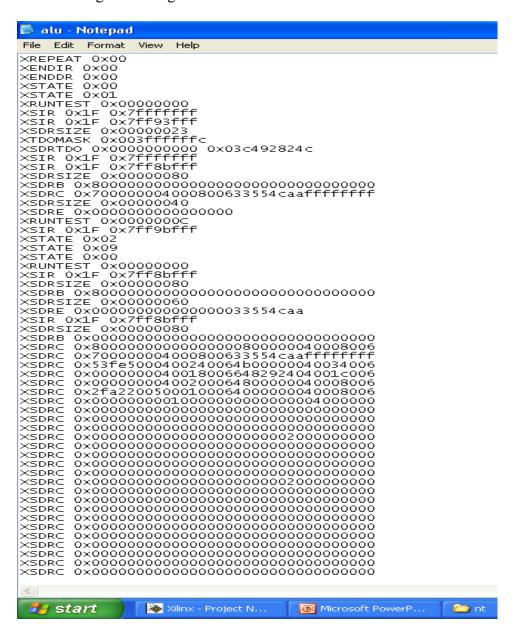

| Figure 14: An .SVF Example [20]                            | 63 |

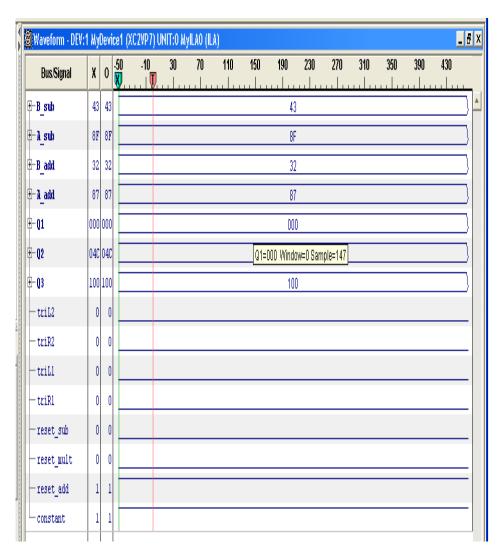

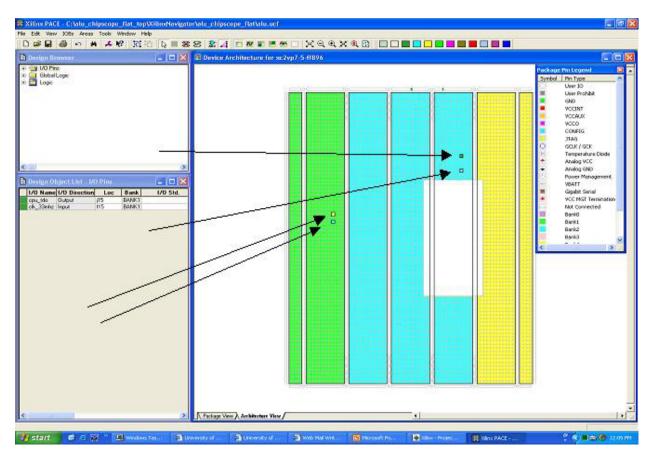

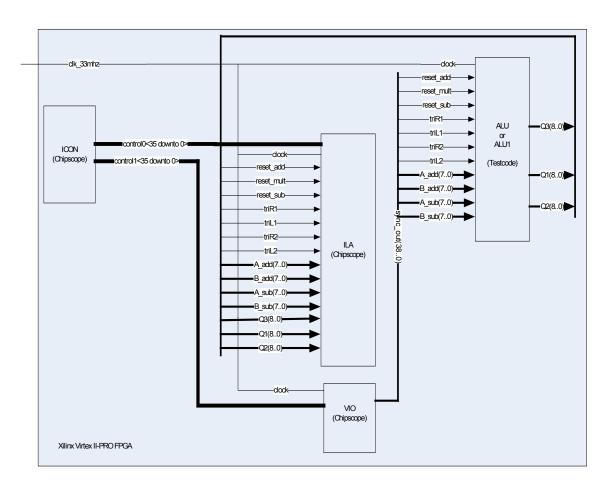

| Figure 15: ChipScope Logic Analyzer [20]                   | 64 |

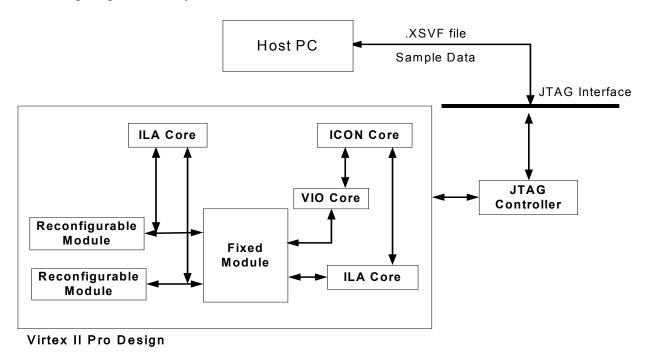

| Figure 16: Loosely Coupled System for JTAG [20]            | 66 |

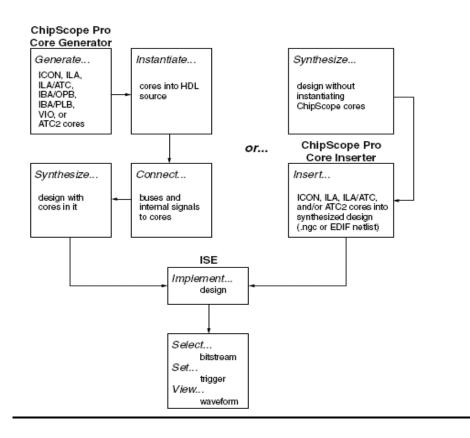

| Figure 17: ChipScope Core Insertion Procedure              | 67 |

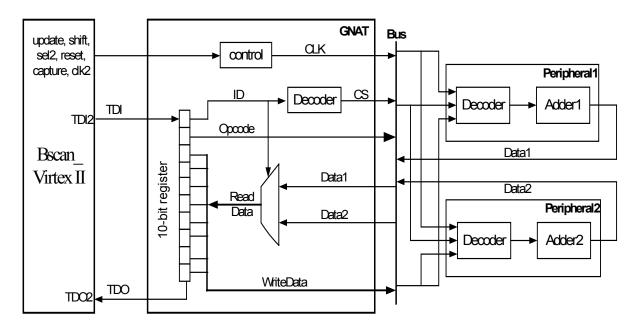

| Figure 18: GNAT Based System                               | 69 |

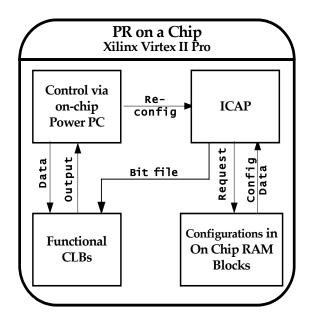

| Figure 19: System On Chip Example                          | 71 |

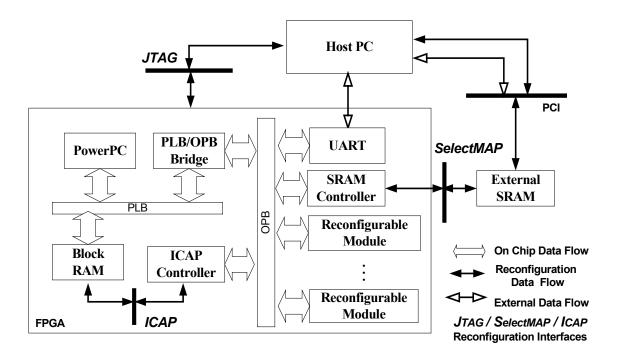

| Figure 20: ICAP Based Testing System                       | 73 |

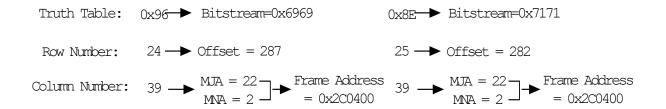

| Figure 21: Bitstream Mapping Process                       | 76 |

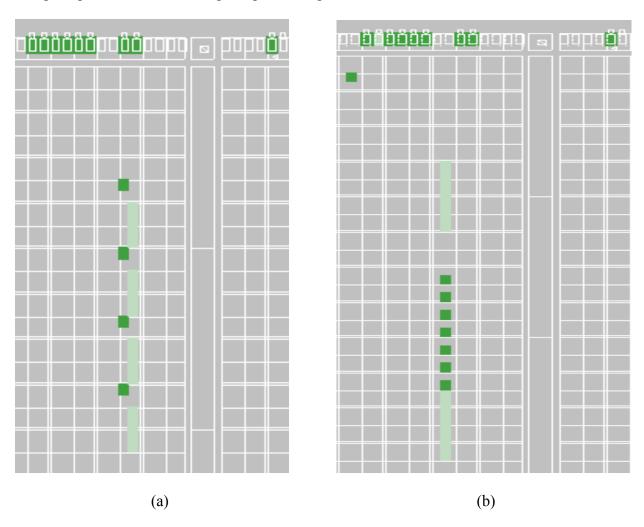

| Figure 22: Bus Macro Placement [20]                                                     | 84    |

|-----------------------------------------------------------------------------------------|-------|

| Figure 23: Partial Reconfiguration Module Routing                                       | 85    |

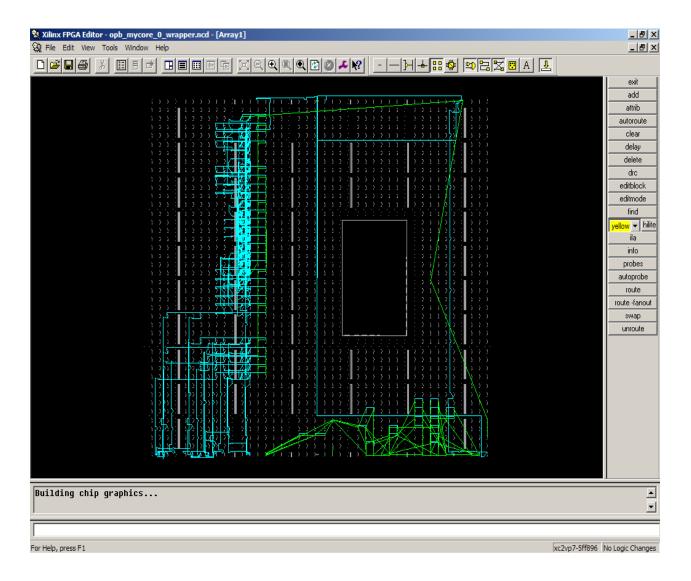

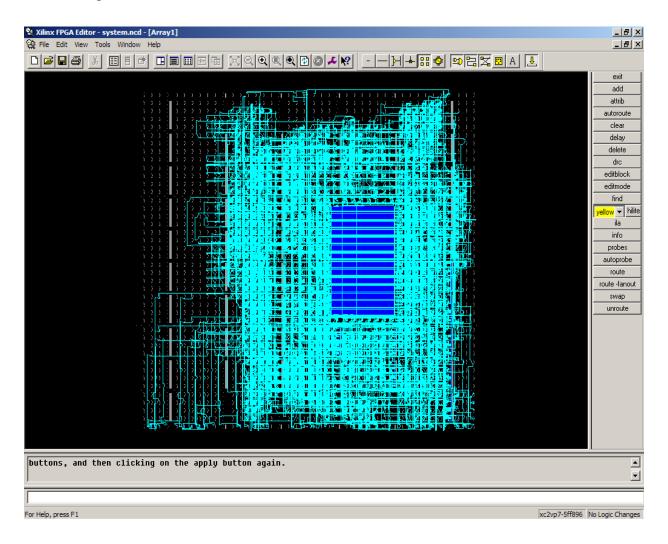

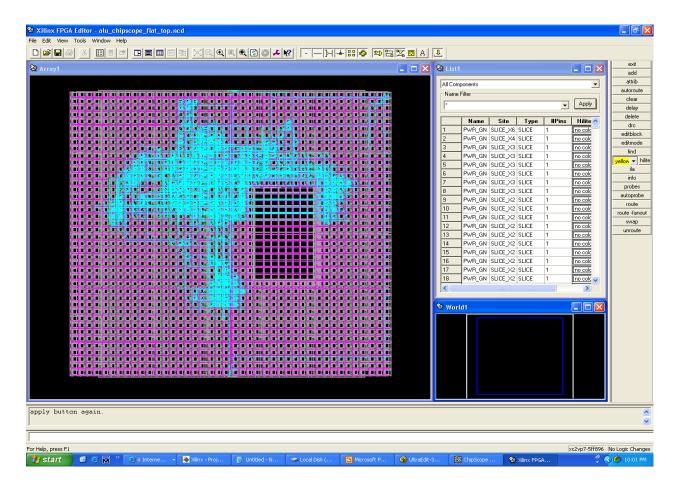

| Figure 24: MRRA with SelectMAP Interface Placement and Routing                          | 86    |

| Figure 25: Block Diagram of ChipScope Cores and Associated Interconnection              | 87    |

| Figure 26: Placement and Routing of ChipScope Cores and Associated Interconnection [20] | 88    |

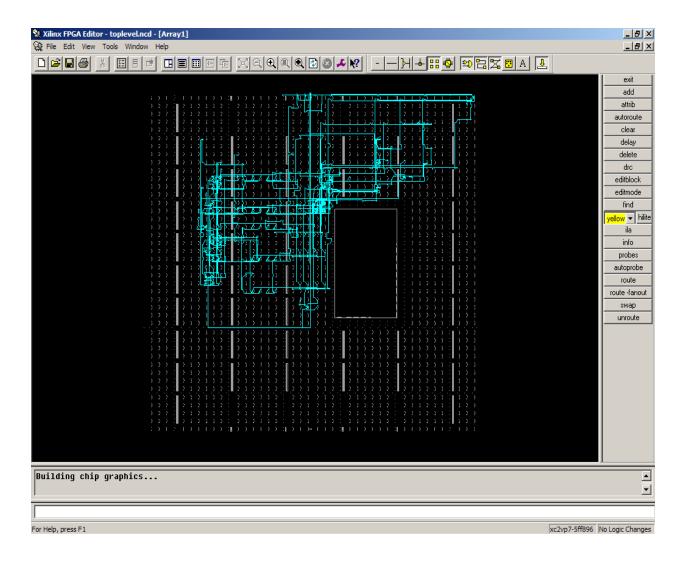

| Figure 27: GNAT Placement and Routing [52]                                              | 89    |

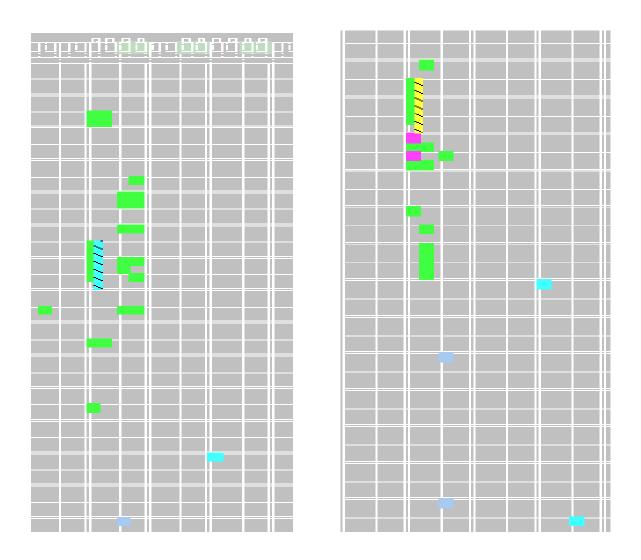

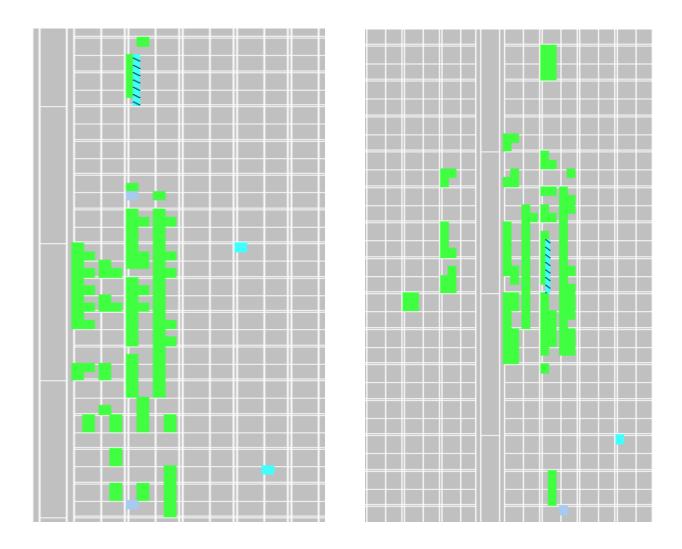

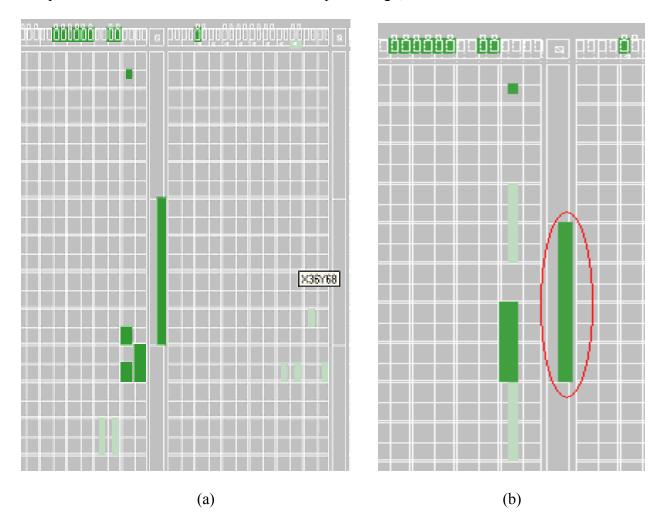

| Figure 28: B02 and C17 Mapping and Placement                                            | 93    |

| Figure 29: B03 and C1908 Mapping and Placement                                          | 94    |

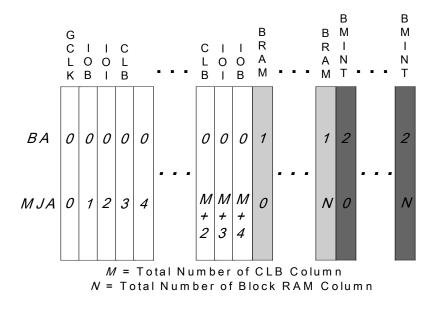

| Figure 30: Column Level Configuration Memory Map                                        | . 102 |

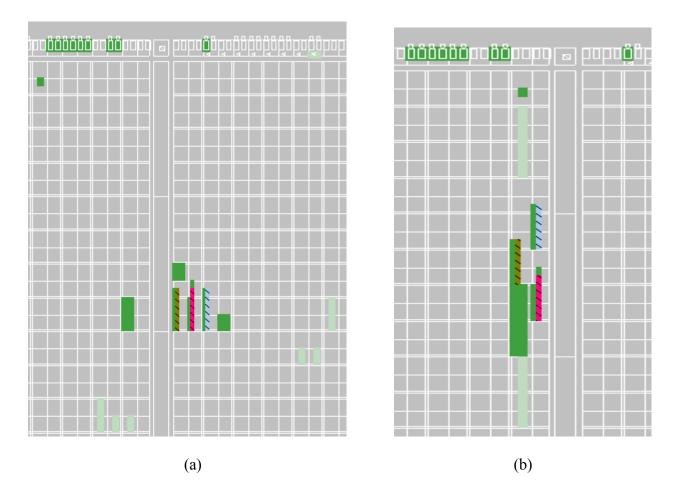

| Figure 31: Optimized Design Layout for Case 1 and 2                                     | . 106 |

| Figure 32: Case 3 Before and After Optimization                                         | . 108 |

| Figure 33: Case 4 Before and After Optimization                                         | . 109 |

| Figure 34: Flexible Routing Example                                                     | . 115 |

| Figure 35: Inter-connectivity Nets for Flexible Routing                                 | . 116 |

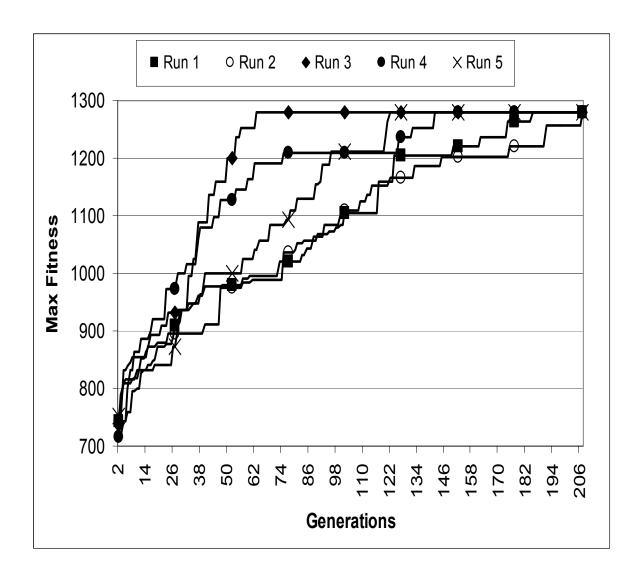

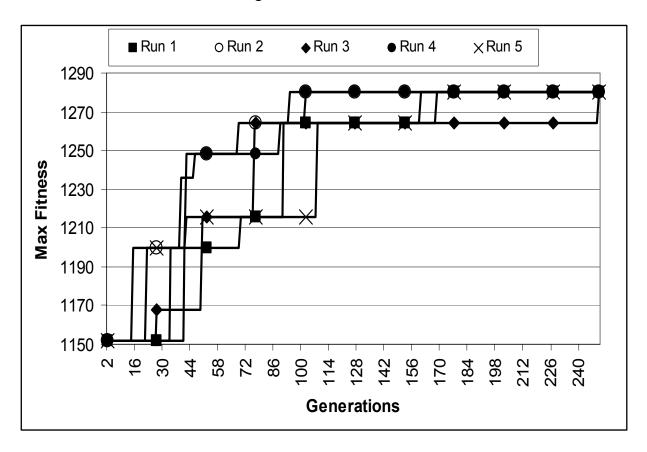

| Figure 36: Unseeded Design GA Runs [52]                                                 | . 122 |

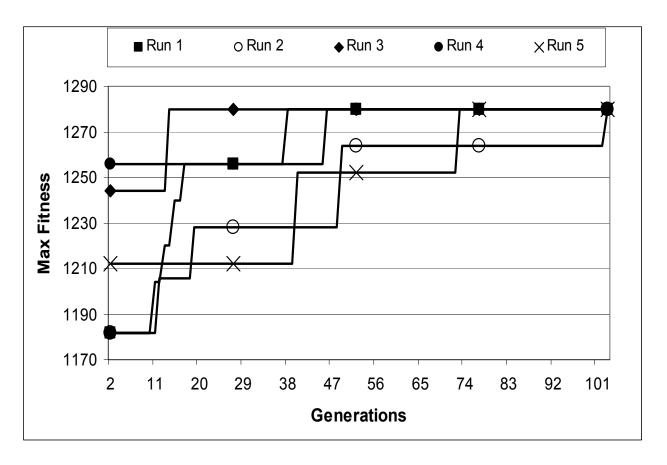

| Figure 37: Seeded Design GA Runs [52]                                                   | . 123 |

| Figure 38: Repair GA Runs [52]                                                          | . 124 |

# LIST OF TABLES

| Table 1: Recent Frameworks for Partial Reconfiguration           | 17  |  |

|------------------------------------------------------------------|-----|--|

| Table 2: High-Level Partial Reconfiguration Optimization         | 24  |  |

| Table 3: Communication APIs on PowerPC                           | 57  |  |

| Table 4: Communication APIs on Host PC                           | 58  |  |

| Table 5: Testing APIs for JTAG                                   | 70  |  |

| Table 6: Step Function Resource Utilization And Power Evaluation | 82  |  |

| Table 7: Resource Utilization                                    | 90  |  |

| Table 8: Basic Timing Evaluation                                 | 92  |  |

| Table 9: Translation Engine Evaluation                           | 96  |  |

| Table 10: Area and Bitstream Optimization                        | 110 |  |

| Table 11: Intermediate Translation APIs                          | 113 |  |

| Table 12: GA Parameters [52]                                     | 121 |  |

## **CHAPTER 1: INTRODUCTION**

#### 1.1 Overview

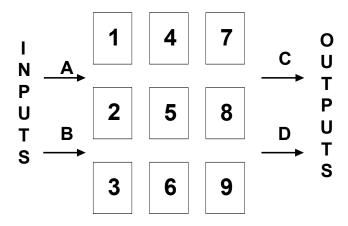

Field reconfigurable devices have been available for almost two decades [50]. The evolution of these systems has been considerably impacted by the development of Field-Programmable Gate Array (FPGA) technology. The basic architecture of a modern FPGA, as shown in Figure 1, consists of an array of Configurable Logic Block (CLB) that can be programmed to implement different design logics and a routing architecture that interconnects the CLB logic. Current commercial FPGA's CLBs can be based on one or more following technologies [32]: Transistor pairs, Basic simple gates such as two-inputs NANDs, Multiplexers, SRAM based Look-up tables, and Wide fan-in AND-OR structures. These CLBs can be implemented into both combinational and sequential logic functions.

The routing architecture of an FPGA is the physical network that makes connections between each individual CLB so that the basic logic functions can be formed into larger algorithms and applications. The routing architecture could be as simple as a nearest neighbor mesh or as complex as the perfect shuffle used in multiprocessor [32]. Most of the time, the FPGA incorporates various lengths of segments that can be interconnected for different needs, such short line, long line and global clock line. The number and the length of the wire segments directly affect the density and performance achieved by a FPGA. Along the path of the routing lines, there are programmable switches that can change the interconnections between different lines. There are three major types of technologies currently in use for the programmable switch implementation: SRAM, Antifuse, and EEPROM. Each has its own advantages and

disadvantages in the term of area and reprogramming ability issues. SRAM-based switches, working just as normal memory elements, can be readily reprogrammed and refreshed. However, they require more transistors to be implemented thus more area is occupied. On the other hand, the Antifuse based switches use the minimum area among the three. Yet they only allow to the device to be programmed once, and after that the interconnections are fixed. EEPROM-based switches stand in the middle among these three in both the area and reprogramming ability issues. Their required implementation area is larger than Antifuse based, but smaller than the SRAM based. They can be reprogrammed multiple times but may require higher voltage and the speed and flexibility is not as good as SRAM.

Figure 1: FPGA architecture

Modem FPGAs have evolved from simple Programmable Logic Devices (PLDs) to fully integrated System on Chip (SOC) architectures containing microprocessors, embedded memory, and optimized datapaths connected to a high capacity, dynamically reconfigurable fabric. As a

case in point, the high-end Virtex FPGAs family offered by Xilinx contains a multi-million gate-equivalent reconfigurable fabric in which several PowerPC processors, a number of RAM blocks, and multipliers are provided. Hence there is considerable interest in using these powerful customizable platforms for a wide range of high-performance scientific computation and embedded applications.

In particular, a unique aspect of flexibility provided by FPGAs is the capability for dynamic reconfiguration, which involves altering the programmed design within an SRAMbased FPGA at run-time [42]. With the capability of partial reconfiguration from device manufacturers [72] and availability of powerful on-chip CPU cores and block RAM, more and more research interests have been focused on this area and demonstrate applications benefiting from use of this reconfiguration paradigm, such as mobile systems [14], [15] operating system frameworks [22], [23] and artificial intelligence applications [4]. On the other hand, although FPGA architectures have advanced considerably, dynamic reconfiguration capabilities are only introduced in quite recent year and have not kept pace with architectural improvements. Currently, only limited FPGA hardware, provide and support partial and dynamic reconfigurable ability to some extent. As more and more applications involve runtime reconfiguration, autonomous dynamic reconfiguration, which automates the partial reconfiguration and/or testing/verification process by combining the capability of partial reconfiguration from the device manufacturers and the availability of powerful on-chip CPU cores, has become an important research topic.

## 1.2 Partial Reconfiguration Technology

Currently multiple vendors offer devices with various partial reconfiguration abilities including Altera, Atmel, Lattice, and Xilinx. The partial reconfiguration capability from Altera only includes certain components such as the divider of the Phase Locked Loop [65], instead of the general reconfigurable resources. The AT40K family from Atmel demonstrates some promising general partial reconfiguration performance with literature describing a 50K maximum gate-equivalent capacity [66], which comparatively restricts the framework and possible applications. On the other hand, Xilinx FPGAs, which provide multi-million gate-equivalent capacities, are the most widely used chips with partial reconfiguration capability. Therefore, most of the current research work focused on these hardware platforms. Work here has also chosen Xilinx as the major research platform. To support their FPGA architectures, Xilinx has proposed two standard reference flows for partial reconfiguration process: *Difference-based flow* and *Module-based flow* [72].

With a Difference-based flow, the designer must manually edit a design with only small changes. After the changes are completed, the partial bitstream, which contains information only regarding the differences between the two designs, is generated and stored in a file. Switching the configuration of a module from one implementation to another is very quick, as the bitstream differences can be significantly smaller than the entire device bitstream [72].

There are two main ways a design can be altered to be utilized with Difference-Based Partial Reconfiguration. The design can be changed either at the front-end in HDL or Schematic format or at the back-end in Native Circuit Description (NCD) file format. For front-end changes, the design must be re-synthesized and re-implemented to create a newly placed and

routed NCD file. For back-end changes to the NCD files, sections of a design can be modified using the FPGA Editor tool directly. Bit stream generation tool then can produce custom partial bitstreams that only modify small sections of the device.

Xilinx Modular Design methodology is another flow proposed by Xilinx, which allows a team of engineers to independently work on different pieces, or "modules," of a design and later merge these modules into one FPGA design [72]. For this flow, the full design is partitioned into modules, some of which can be fixed while others can be reconfigurable. The reconfigurable fabric of the FPGA is partitioned into column-based rectangular regions with the width ranging from a minimum of four slices to a maximum of the full-device width in four-slice increments, in which the fixed and reconfigurable modules will be arranged based on specified area constrains of the design.

Figure 2: Design Layout with Two Reconfigurable Modules

There should be no common I/O between fixed and reconfigurable modules except the clock. If signals are needed to cross over a partial reconfiguration area boundary, a *bus macro*, a fixed "bus" of inter-design communication, should be used to maintain correct connections

between the modules by spanning the boundaries of these rectangular regions. Each time when partial reconfiguration is performed, the bus macro is used to establish unchanging routing channels between modules, guaranteeing correct connections. Figure 2 shows the basic concept of this reconfiguration flow methodology. Such arrangement makes the Module-based flow much more flexible than the Difference-based flow and suitable for possible full automation, particularly when it is considered for integration with high-level user applications. Therefore, the Module-based flow has been chosen as the primary basic partial reconfiguration technique for the research.

## 1.3 Need for Autonomous Partial Reconfiguration

As mentioned earlier, since the introduction of the partial reconfiguration technique, more and more high-level applications and algorithms in different areas have been attempting to incorporate this concept into their design to boost their performance and decrease the human-related control requirements. NASA deep space mission is one of the typical examples of such scenarios, which requires high reliability involving mission safety or other critical tasks. Such applications rely increasingly on FPGAs to support their computing requirements. For example, NASA's Stardust probe carries on board over 100 FPGA devices [27]. As the number of FPGAs increases in the computing systems supporting these missions, fault detection and repair becomes critical to these missions. While a probe is traveling in deep space, permanent failures can degrade the functionality of Configurable Logic Blocks (CLBs) or programmable interconnects of the FPGAs. To quickly reconfigure many alternatives in an attempt to recover from these failures is necessary to keep the on-board computing system of the probe in normal operation.

However, under such circumstances, human intervention is very difficult or even impossible to carry out and will definitely slow down the performance of the original task significantly. Hence, an automatic mechanism is crucial to carry out such process. At the same time, such high throughput applications also require the reconfiguration operations to be processed as fast as possible to avoid long time system waiting and severe performance degeneration.

To meet such requirements, the partial reconfiguration management should be automatic, seamless, and completely transparent to the application. The management architecture needs to determine:

- (i) *Partitioning*: Which computational resources to initialize as component,

- (ii) *Placement*: How to determine the target location of the component on the reconfigurable fabric of the device,

- (iii) Routing: How to properly interface the component to its surrounding resources,

- (iv) Generation: How to generate the new bitstream of the component at the target location,

- (v) Configuration: When and how to write the generated bitstream to the appropriate portions of the underlying reconfigurable infrastructure of the reconfigurable fabric, and

- (vi) *Verification*: How to communicate with the hardware platform to test and validate the new downloaded bitstream.

However, current partial reconfiguration flow suggested by Xilinx mainly focused on the 4th step and thus only provides an incomplete solution to it. To use this basic flow, design tools with GUI are involved. Manual adjustments of design are unavoidable. Full automation control

process, as required by most of the current partial reconfiguration applications, is almost impractical.

Furthermore, using this basic solution, the reconfiguration generation delay alone is already on the order of tens to hundreds of milliseconds [54]. In some situations, configuration overhead can comprise over 98.5% of execution time [36]. Clearly, this extremely slow process already becomes one of the major barriers, especially for applications based on redundancy and spare availability when using partial reconfigurations such as [39], [57]. Some research work has been carried out at various levels to suggest solutions for separate steps. But so far there is no framework that has been proposed to accomplish all of the above steps and provides a general-purpose solution.

A more sophisticated partial reconfiguration framework would be useful to integrate and optimize existing reprogrammable technologies, as well as refine theories of operation in light of the feasibility of current and near-term hardware implementations. Ideally, this approach would provide a standardized set of APIs and abstracted data structures for a variety of high-level applications. It would facilitate algorithm mapping via uniform access to heterogeneous logic and communication resources. Such an approach would also improve flexibility and enhance portability across hardware reconfiguration interfaces requirements, and enable more sophisticated applications based on autonomous reconfiguration.

#### 1.4 Dissertation Outline

The remainder of the document is divided into the following Chapters. In Chapter 2, *PREVIOUS WORK*, a review of the State of the Art in partial reconfiguration tools, architectures and high-level control algorithms is given. The section *Partial Reconfiguration Tools and Framework* introduces the current toolsets for partial reconfiguration published by industry companies and some of most recent framework and toolsets for partial reconfiguration developed at academic area. The section *Hardware Optimization Technique* refers to the proposed optimization techniques that addressed the basic partial reconfiguration hardware components or the bitstream generation process. The chapter ends with the section *Software Control Optimization* that contrasts the investigated techniques at the software algorithm level for partial reconfiguration research.

In Chapter 3, MULTILAYER RUNTIME RECONFIGURATION ARCHITECTURE, the design considerations for the autonomous reconfiguration architecture are first analyzed. The detailed architecture design is then discussed, including the 3 layers of the Hierarchical Architecture and the Dynamic Control Flow, which provide the Adopted Module Based Flow at design phase, the Frame Based Flow at runtime phase and the Physical Area Management control. Finally the basic Genetic Algorithm Operators for FPGA high-level fault tolerance application based on the MRRA structure and control flow are illustrated.

In Chapter 4, *RECONFIGURATION AND VERIFICATION METHODOLOGY*, the system design considerations for the reconfiguration and verification methodology are discussed. Three different types of reconfiguration interface, including SelectMAP, Joint Test Action Group (JTAG) and Internal Configuration Access Port (ICAP) are introduced. Difference

reconfiguration and verification methodologies and system design based on the characteristics of these three interfaces are explored. Details of bit manipulation and function mapping equations are also studied and discussed in details.

In Chapter 5, RESOURCE UTILIZATION AND TIMING ANALYSIS, three groups of experiments are described. First group of tests analyzed the resource utilization and power consumption by using two Hashing algorithms as top-level application case study. The data are compared and contrast through the criteria of slice occupancy, dynamic power consumption, and core power consumption. The utilization data are analyzed in three groupings of the design, including the traditional baseline design, module-based design, and frame-based design. The second group of experiments demonstrates the detailed FPGA resource utilization for each MRRA platform with a different reconfiguration interface and testing methodology. Six different MRRA prototype platforms are tested. In addition to the slice utilizations, the routing flexibility, I/O arrangement, resource placement and communication overhead are also used as metrics to quantify these platforms' performance. The last group of experiments evaluates the timing performance of the MRRA system, including the basic reconfiguration and testing time and the Translation Engine overhead. A brief timing analysis is also presented based on the collected data to determine the bottleneck of the system speed and possible optimization methodology through pipelining.

In Chapter 6, *HIGH-LEVEL RECONFIGURATION OPTIMIZATION TECHNIQUES*, the proposed bitstream optimization strategy is tested and its behavior is analyzed by applying it to five different types of experimental circuits. Comparisons against the tool automation approach are given. The design technique of linking the high-level data structure with the physical circuit design is then demonstrated. The flexible routing strategy by using LUT-based switch box is also

presented. The resource expense of this strategy is analyzed as well. The final part of this chapter shows the experimental details of GA applications running on MRRA using these advanced techniques.

In Chapter 7, *CONCLUSION*, the results of the experiments are summarized and general conclusions about MRRA architecture design, the reconfiguration and verification methodology employed, and high-level application design using the MRRA platform are drawn. Future work is identified for the continuation of the project. Several areas are proposed for further research, related to new hardware architecture, better area management algorithms, and the application of these techniques at general data structure level, especially for GAs.

#### 1.5 Contribution of Dissertation

A summary of the major contributions made by this dissertation includes:

- 1) An original thorough solution providing a clear framework with standard interfaces between partial reconfiguration physical implementations and logic designs, which allows the general high-level algorithms to execute at an abstract level without the knowledge of the low-level hardware details. Other COTS tools may be easily integrated into this framework and customized for their own applications. This enables a real hardware-related Genetic Algorithm to execute directly on a FPGA in real-time.

- 2) Layering model that shields the reconfiguration logic and higher-level application logic from the hardware details. So when later a different FPGA is selected for use, the bottom reconfiguration layer can change accordingly. The algorithm layer

- can remain untouched. The only modification needed is carried out on the hardware-dependent part of the APIs at the translation layer.

- 3) This is the first system design that explores multiple mainstream reconfiguration interfaces and provides correspondent reconfiguration and verification methodologies. Their performance is also contrasted and compared between each other. Advantages and disadvantages are analyzed in details under a variety of scenarios.

- 4) The traditional spatial and temporal algorithms for fast configuration are also advanced. A practical strategy is formed based on current hardware technology. The strategy now is implemented distributively in multiple layers as independent hardware or software modules. Therefore these algorithms can be used respectively or combined depending on user's high-level application. Special modifications can also be easily carried out on these traditional algorithms for specific user requirements without affecting the normal major working flow.

The benefits of this MRRA approach include increased design productivity, portability and resources utilization. On the other hand, these advantages require new tradeoffs for extra hardware complexity, software capability, and resource overhead, as quantified in the analysis herein.

#### **CHAPTER 2: PREVIOUS WORK**

Many different industry efforts and research works aimed at different aspects of partial reconfiguration have been studied in the literature, including partial reconfiguration generation tools, layered partial reconfiguration frameworks, hardware size and performance optimizations and software control optimizations, etc. Some of the most recent and relevant works from each category are reviewed in this Chapter.

## 2.1 Commercial Partial Reconfiguration Tools

Currently, the most widely used FPGA chips with partial reconfiguration capability are from Xilinx in the Virtex, Virtex II, and Virtex Pro families [69]. Yet only very few preliminary toolsets commercially have been reported supporting the partial reconfiguration paradigm. JBits [53], an earlier research toolset presented by Xilinx, provides dynamic reconfiguration capabilities, allowing an application to instantiate a component, generate its corresponding bitstream, and download it to a reconfigurable device. The JBits Application Programming Interface (API) is implemented in the Java programming language and permits programmatic access to all of the configurable elements in Xilinx Virtex-II FPGAs. It supports partial configuration and modification of the bitstream. It is a low level tool that not only changes the logic content of LUTs, but also dynamically modifies specific logic interconnections. JBits communicates with the hardware through a generic hardware interface called Xilinx Hardware Interface or XHWIF. It can be very useful for designers who want to design run-time reconfigurable logic on FPGAs, which will help in the future revolution of online upgradeable hardware. Since the tool is Java based, the execution speed can be comparatively slow. This

toolset has been made only available for the Virtex family primarily as a research tool for Virtex II series, instead of the bigger Virtex family such as Virtex II Pro and Virtex 4. Xilinx had dropped all the technical support and further development several years ago, even though the toolsets still have significant academic interest.

The Xilinx Partial Reconfiguration Toolkit (XPART) [5] is another tool that has been proposed by Xilinx engineers in 2003. XPART is derived from the JBits API efforts. It provides a lightweight, minimal set of JBits API features implemented in the C language instead of Java. Similar to the JBits API, it abstracts the bitstream details providing seemingly random access to select FPGA resources. The XPART API enables fine grain reconfiguration control over select FPGA resources. This allows actions such as tuning off Multi-Gigabit Transceiver (MGT), or constant folding achieved by modifying LUTs. XPART also provides some basic functionality for supporting relocatable modules. A locatable module is a partial bitstream that can be relocated to multiple places on the FPGA. XPART provides two methods for dealing with relocatable modules. The two methods are setCLBModule and copyCLBModule. The setCLBModule method works on regular partial bitstreams that contains information about all of the rows in the included frames. The copyCLBModule function copies any sized rectangular region of configuration memory and writes it to another location. The copied region contains just a subset of the rows in a frame. This allows the designer to define dynamic regions that have static regions above or below it. The copyModule function employees a read/modify/write strategy like the re-source modification functions. This technique enables changing select bits in a frame and leaving the others bits to their current configured state. This self-reconfiguring platform enables embedded applications to take advantage of dynamic partial reconfiguration without requiring external circuitry. However this toolset has never been officially released.

The most recent released platform for partial reconfiguration paradigm by Xilinx is called PlanAhead [68]. This software is based on the Module Based flow paradigm introduced in Chapter 1. PlanAhead streamlines the design step between synthesis and place and route and attempts to reduce in both the number and the length of design iterations. This methodology allows designers to divide a larger design up into smaller, more manageable blocks and focus efforts toward optimization of each module, improving performance and quality of the entire design. PlanAhead software is the first graphical environment for partial reconfiguration. Using PlanAhead design tools as a platform for partial reconfiguration applications can simplify the complexities of the constraints of the dynamic operating environment of applications, allowing a single device to operate in applications that previously required multiple FPGAs. It provides a single environment to manage the Module Based flow guidelines. Using PlanAhead design tools to implement a partial reconfiguration design, users can carry out the netlist import, floor planning for partial reconfiguration, design rule checks, netlist export, and implementation flow management. The methodology offered by PlanAhead software can potentially increase productivity and decrease time-to-solution for designers using partial reconfiguration. However this tool is a graphical environment for design time use only instead of runtime control. Moreover, it supports the Module Based flow considerations. Currently, the partial reconfiguration function part of this tool is also not open for public use yet and requires a special request to Xilinx for access.

## 2.2 Partial Reconfiguration Tools and Framework

Since the commercial works have placed emphasis on components and methods for the step of partial reconfiguration file generation, significant challenges have remain with creating an autonomous environment for dynamic reconfiguration. Significant recent work in academia and industry has been focused on this area.

Some representative research approaches are listed in Table 1. Early work by Moraes et al had developed a set of tools for remote and partial reconfiguration for Virtex XCV300 [11]. With this toolset remote reconfiguration is enabled to update and/or fix hardware cores in the field. By using this toolset, parameter reconfiguration can be used to customize a circuit, avoiding extra devices as external microcontrollers and ROMs, and saving internal control logic in the FPGA. However, some steps of the approach have to be carried out with manual user intervention and the described technique does not intrinsically support core relocation.

Raghavan and Sutton's tool called JPG was developed for Xilinx Virtex devices [1]. This JPG tool is based on the Xilinx Java-based JBits API. Jbits allows an application to instantiate a component, generate its corresponding bitstream, and download it to a reconfigurable device such as the Virtex FPGA. Therefore JPG is able to generate partial bitstreams for Xilinx Virtex devices based on data extracted from the standard Xilinx CAD tool flow. Yet due to the use of JBits and its Java interpretation overheads, the tool has some speed and scalability limitations. Since Xilinx had already dropped the support for JBits, further upgrading and expansion of this framework may be uncertain.

Table 1: Recent Frameworks for Partial Reconfiguration

| Approach             | DEVICE<br>SUPPORTED | ON-CHIP<br>SYSTEM | Bitstream<br>Reuse | POTENTIAL<br>CHALLENGES            |

|----------------------|---------------------|-------------------|--------------------|------------------------------------|

| Mesquita et al.      | Virtex XCV300       | N                 | N                  | Area<br>Relocation                 |

| Raghavan,<br>Sutton  | Virtex              | N                 | N                  | Supporting CAD flow                |

| Blodget,<br>McMillan | Virtex II           | Partial           | Y                  | Direct bitstream reuse             |

| Williams et al.      | Virtex II           | Y                 | Y                  | Large User application             |

| Kalte et al.         | Virtex E            | N                 | Y                  | Dynamic Routing                    |

| Bobda et al.         | Virtex              | N                 | N                  | Communication and Control Overhead |

To avoid some of these limitations and more fully encapsulate the higher layers from low-level device specifics, a two-layer framework for Virtex II devices had been separately suggested by Blodget et al [6] and also Fong et al [51]. These systems enable self-reconfiguration under software control within a single FPGA. The system enables self-reconfiguration through the reconfiguration hardware interface *Internal Configuration Access Port (ICAP)* inside the Xilinx FPGA. The reconfiguration subsystem has a two-layer hardware and software architecture that permits a variety of different interfaces. The system enables self-reconfiguration under software control within a single FPGA, minimizes the need for external hardware and provides a highly integrated, lightweight approach to dynamic reconfiguration for embedded systems. However, because of the operations of ICAP, the bitstream has to be processed directly instead of high-level netlists.

Experimental Generic Reconfigurable Embedded Target (EGRET) [33] [45] is another similar framework proposed by Williams et al. This framework is also focusing on full system-on-chip (SOC) solution by using ICAP and an embedded Linux system on a Xilinx Virtex II

chip. More emphasis has been drawn to the software control side using embedded Linux. But on the other hand, currently available CPU core speed and RAM size can impact the complexity of the high-level applications that can be implemented into such solution.

Bobda et al also presented a framework named Erlangen Slot Machine (ESM) [9]. In this platform, each module can access its periphery independent from its location through a programmable crossbar, which gives the potential of unrestricted one-dimensional relocation of modules on the device. Different inter-module communication channels, including a bus macro, shared memory, reconfigurable multiple bus and crossbar have also been proposed. As a variety of communication channels are available, multiple external control hardware and boards can be involved. Communication and control overheads using such approaches may vary.

The most recent framework developed by Kalte et al [16] is called *REPLICA (Relocation per online Configuration Alteration)*, which mainly focused on the step of downloading and relocating the modules. The REPLICA parses the bitstream during the normal download process and replaces the column addresses within the bitstream according to the desired location of the module. Next, it uses the SelectMAP interface to perform bitstream manipulation to carry out the relocation process on Xilinx Virtex Series to achieve the maximum possible throughput. Other similar proposed frameworks and tools for partial reconfiguration process also include [12], [26], [33], [51], and others.

# 2.3 Hardware Optimization Technique

One of the other common research interest areas is at the downloading step, by using different hardware optimization techniques to achieve possible timing and performance

improvement. In previous early stages of research, bit file compression [25] [56] is one of the direct approaches used to accelerate the reconfiguration process. In such an approach, customized decompression hardware is required. Different general-purpose compression algorithms for reconfiguration may be carried out. It had been reported that using this approach might bring an overall reduction of up to a factor of four in total bandwidth required for reconfiguration under Hank's approach [56].

With the appearance of the partial reconfiguration technology in recent years, it has observed that the configuration overhead can be improved by just over a factor of 7 over the serially programmed FPGA [36]. This led to an extra series methods addressing from different hardware aspects to improve its efficiency and thus increase the reconfiguration speed even more. Compton, Li, Knol and Hauck [36] developed an algorithm for configuration relocation and defragmentation. A new custom designed architecture FPGA as well as software algorithms for controlling this hardware is presented, which has different features from the normal commercial FPGA chips. With an extra hardware area specially designed for controlling the relocation and defragmentation, which is comparatively negligible, it is reported that as much as 35% improvement in reconfiguration times in these devices for realistic run-time algorithms may be gained, compared with basic partial reconfiguration architecture and multi-context device [36]. However this architecture modification is specifically based on the Xilinx 6200 series, which is not available any longer in the market.

For more recent practical solutions, Raghuraman, Wang, Tragoudas [37] on the other hand studied the configuration data size at the logic level. In this approach, the LUTs' inputs are fixed to appropriate order based on a heuristic algorithm in polynomial time. With such LUT input orders, memory locations that need to be changed during partial reconfiguration process are

relocated into common frames as many as possible. By relating the number of frames that need to be downloaded into FPGAs to the number of minterms of a specially constructed logic function, the required number of configuration frames can be reduced. Since the number of the configuration frames is directly related to the size of the partial reconfiguration bitstream, the final hardware bit file size should be able to be reduced. It is reported that the size of the reconfiguration data could be reduced by around 15% by this approach.

Regarding to other aspects of the partial reconfiguration hardware bitstream generation, Upegui and Sanchez [3] recently discussed possible methodologies to generate the partial reconfiguration bitstreams. Besides the standard module-based and difference-based approaches suggested by Xilinx, the technique for low-level direct bitstream modification is suggested. By calculating the physical location of specific LUT, the logic of this LUT can be directly located in the bitstream. Thus, the logic content of LUTs can be modified directly inside the old bitstream with much faster speed instead of generating a new one based on the cumbersome standard CAD flow. However, this paper only discussed the full bitstream format without exploring the partial reconfiguration bitstream pattern, which is quite different from the format of a complete device file. This limits the usage of such approach. Moreover, this direct bitstream modification can only apply to the logic contents, instead of the routing part of the bitstream, which is far too complicate to be manipulated at the bitstream level.

Sedcole et al [48] also presented a new partial reconfiguration flow to generate the hardware bitstream, called the *merge partial reconfiguration method*. The merge method prepares modules to be allocated arbitrary areas in FPGA with a customized tool required to be involved in the place and route step of the process. In this method, by using an XOR function to combine the new partial bitstream and the current configuration read back from the device,

existing configuration information is preserved, and the module can be removed by repeating the XOR operation. Only the difference then needs to be downloaded to the device. Modules can be allocated in any rectangle region in device and static routes can pass though reconfiguration area. To avoid conflicts, some of the routing resources are reserved for the static routes. It is reported that speed measurements have revealed an increase in configuration times of between 2.4-fold to 4.0-fold, with a baseline overhead of at least 1.58-fold.

Hardware routing-related issues with partial reconfiguration are also addressed. Two types of special designed communication bus for partial reconfiguration modules research independently by Krasteva et al [62] and group of Bobda et al [8] to take the place the bus macro suggested by Xilinx. By using LUT-based or slot-based communication bus macro structure, physical partial reconfiguration resource region size may be modified based on the logic modules size. Large regions may be spilt. Adjacent small ones may be combined together. Thus, it provides possibility of module relocation and area re-partition. This can bring potential for optimization of the hardware performance.

# 2.4 Software Control Optimization

Besides the low-level hardware related research, a lot of approaches had also been proposed from theoretical control algorithm angles, including both design phase and runtime phase of the partial reconfiguration flow. In Shirazi, Luk and Cheung's approach, two successive circuit configurations are matched to locate the components common to them, so that reconfiguration time can be minimized [46]. Two stages had to be carried out for this approach. In the first stage, possible components for reconfiguration are identified, and a sequence of

conditions for activating an appropriate component at a particular time is found. This step has to be carried out manually. In the second stage, successive configurations will be optimized to achieve the desired trade-offs in reconfiguration time, operation speed and design size. Components and connections common to two or more successive configurations will be identified automatically and will not be reconfigured.

Another approach suggested by Diessel, Middendorf and Schmeck is dynamic scheduling when there are multiple independent tasks to be reconfigured [47]. Rearranging a subset of executing tasks takes two steps. The first step identifies a rearrangement of the tasks executing on the FPGA that frees sufficient space for the waiting task, and the second schedules the movements of chosen tasks so as to minimize the delay to their execution. Three methods for have been tested, including *local repacking* (deterministic heuristics), *ordered compaction* and GA. However the result varies depending on the reconfiguration delay  $T_{DRT}(i)$  and the processing time of tasks  $T_{TAT}(i)$ . The GA is advantageous when  $T_{DRT}(i) \ll T_{TAT}(i)$ . While for the large reconfiguration delays  $T_{DRT}(i)$  and smaller task processing times  $T_{TAT}(i)$ , faster methods carrying out less rearrangement perform better. When  $T_{DRT}(i) \gg T_{TAT}(i)$ , the simple first-fit method without rearrangement tends to perform well.

For large reconfiguration tasks, Mak and Young introduced a temporal logic replication method named hierarchical bipartitioning [60]. In this method, an application has to be partitioned into multiple stages. The configuration will be switched continuously to implement each stage one by one in order to perform the function of the original circuit. They applied this to effectively exploit the slack capacity of a stage to reduce the communication cost. For the case when there is a tight area bound that limits the amount of replication, they also presented a flow-

based replication heuristic. In addition, they showed a correct network flow model for partitioning sequential circuits temporarily and proposed a new hierarchical flow-based performance-driven partitioner for computing initial partitions without replication [60].

Pipelining is another temporal partitioning approach discussed by Ganesan and Vemuri [55]. By using the processors partial reconfiguration capability, overlapping execution of one temporal partition with the reconfiguration of another, reconfiguration overhead  $L_{tot}$  was reduced from  $\sum_{i=1}^{n} (T_{DRT}(i) + T_{E}(i))$  to  $T_{DRT}(1) + \sum_{i=1}^{n-1} \max(T_{DRT}(i+1) + T_{E}(i)) + T_{E}(n)$ , where  $T_{DRT}(i)$  and  $T_{E}(i)$  are the reconfiguration time and execution time respectively. They also incorporated block processing in the partitioning framework for reducing overhead of partitioned with the ability to handle loops and conditional constructs in the input specification.

Herbert, Christoph and Macro presented placement methods that rely on efficient algorithms for the partitioning of the reconfigurable resource in the temporal level and a hash matrix data structure to maintain the free space in the spatial level at the same time [22]. Given n as currently placed tasks, previously known placers find a feasible location in O(n) time. Additionally, simulations show that the methods improve the placement quality by up to 70% compared to Bazargan's Partitioner [35].

However, these proposed methods are only focused on the logic algorithm level with simplified FPGA architecture and partial reconfiguration operation assumptions, which current hardware may not be able to provide. Most of them remain untested on real hardware platforms or even sophisticated commercial simulation tools. Therefore each may have its own implementation limits. Some may appear to be even impractical to implement based on current partial reconfiguration technology. The brief comparison of these methods is listed in Table 2.

Table 2: High-Level Partial Reconfiguration Optimization

| Approach                                       | Метнор                                                             | PARTIAL<br>RECONFIGU-<br>-RATION | SPATIAL<br>REALLOCA-<br>-TION | TEMPORAL<br>PARALLELISM | Area<br>Shape | RUN-TIME | POTENTIAL<br>LIMITATIONS              |

|------------------------------------------------|--------------------------------------------------------------------|----------------------------------|-------------------------------|-------------------------|---------------|----------|---------------------------------------|

| Hauck, Li,<br>Schwabe                          | Bit file compression                                               | No                               | N/A                           | N/A                     | N/A           | No       | Full reconfiguration required         |

| Shirazi, Luk,<br>Cheung                        | Identifying common components                                      | Yes                              | N/A                           | N/A                     | N/A           | No       | Design time work required             |

| Compton, Li,<br>Knol, Hauck                    | Relocation and<br>Defragmentation<br>with new FPGA<br>architecture | Yes                              | Yes                           | No                      | Row-<br>based | Yes      | Special FPGA architecture required    |

| Diessel,<br>Middendorf,<br>Schmeck,<br>Schmidt | Task Remapped and Relocated                                        | Yes                              | Yes                           | No                      | Rectangle     | Yes      | Overhead for remapping calculations   |

| Mak, Young                                     | Dynamic<br>Partitioning                                            | Yes                              | No                            | Yes                     | N/A           | Yes      | Only desirable to large design        |

| Ganesan,<br>Vemuri                             | Pipeline                                                           | Yes                              | No                            | Yes                     | N/A           | Yes      | Limited pipeline depth                |

| Herbert,<br>Christoph,<br>Macro                | Partitioning and 2D Hashing                                        | Yes                              | Yes                           | Yes                     | Rectangle     | Yes      | Rigid task<br>modeling<br>assumptions |

Now with the appearance of partial reconfiguration technique from Xilinx and more powerful FPGA chip equipped with on-chip CPU core, a more sophisticated and thorough approach may be applied to the reconfiguration process. In this dissertation, a 3-layer architecture, named Multilayer Runtime Reconfiguration Architecture (MRRA) is proposed to establish a general-purpose framework for a wide variety of practical applications and algorithms that require reconfiguration during operation. This framework seeks to integrate and optimize existing technologies and theories as well as fill in all the missing pieces to thoroughly fulfill the tasks listed in Section 3 of Chapter 1. All the concepts and architectures proposed in this

dissertation have been validated with on a real hardware platform along with detailed performance analysis.

# 2.5 Chapter Summary

This chapter has explored the recent previous works related to partial reconfiguration from multiple areas. In Chapter 2.1, the available commercial partial reconfiguration tools are introduced. Chapter 2.2 presents and compares the previous work at the partial reconfiguration framework area with their advantages and disadvantages. In Chapter 2.3, the past research work at hardware optimization field is discussed. Different techniques are explained. Chapter 2.4 introduced the previous research at the high-level software control area of the partial reconfiguration process. A quick summary of different algorithms is also listed in the Table provide.

## CHAPTER 3: MULTI-LAYER RUNTIME RECONFIGURATION ARCHITECTURE

# 3.1 Architecture Design Definition

Currently, the most widely used FPGA chips with partial reconfiguration capability are from Xilinx in the Virtex, Virtex II, and Virtex Pro families. Yet, there are no sophisticated toolsets commercially available supporting many aspects of the partial reconfiguration paradigm. In order to accommodate a variety of reconfiguration processes required by different applications, a tiered framework, called the *Multilayer Runtime Reconfiguration Architecture* (MRRA) based on the available Xilinx FPGA hardware is designed. This architecture includes two aspects. The first aspect is a Tiered Framework. There are four major design considerations that should be able to conceptually address in this framework:

**Autonomous Operation**: Provide stand-alone reconfiguration capability on the FPGA device as well as a bi-directional communication channel with the embedded host PC to carry out the partial reconfiguration process and routing without manual intervention.

**Task-level Modularity**: Provide support at levels down to, and including, task-level granularity. A task is defined as an arbitrary function synthesized to a module that can be dynamically downloaded into the reconfigurable device.

**Runtime Scenario Support**: Provide the ability to generate and reconfigure task bitstreams at runtime as well as design-time. Runtime scenarios envisioned at design-time may not necessarily know in advance which tasks will arrive nor when they will arrive, and in selected cases, what some of their specific properties will be.

In addition to the framework, the second element of the MRRA paradigm is a Logic Control Flow aimed at increasing capability towards the following attributes:

**Flow Coverage:** Both the design phase and the runtime phase are automated, so that the partitioning, placement, routing, bitstream generation, and configuration steps can be accommodated.

**Encapsulation:** Control logic of each layer is self-contained thus exposing only a fixed interface to other layers, so that modification made at one layer has minimal influence on other layers. If new control algorithms are added or the device platform is changed, the system can be ported more readily.

**Standardization:** A standardized set of APIs is provided for uniform access to heterogeneous logic and communication resources.

Effective provision of these capabilities in MRRA design can accelerate reconfiguration speed, reduce resource inefficiencies, and realize sophisticated range of applications. The benefits of this MRRA approach include increased design productivity, portability and resources utilization. On the other hand, the coming along extra hardware and software resources overhead may need to estimate and compensate.

In this dissertation, some of the existing reprogrammable technologies and theories of operation are investigated and enhanced. Missing components of the steps are explored. A full general-purpose framework MRRA is proposed. A high-level data structure along with a standardized logic control flow is developed in the MRRA framework to enable flexible implementation of user applications and maximize the overall performance. Standardized set of Application Programming Interfaces (APIs) and corresponding hardware platform are demonstrated for uniform access to heterogeneous logic and communication resources. Speed

and area optimization method for reconfiguration is also presented. On the other hand, estimation and compensation techniques are also explored to deal with the additional hardware and software resource demands required to provide such advantages.

## 3.2 Hierarchical Architecture Design

Figure 3: Multi-layer Runtime Reconfiguration Architecture

Figure 3 shows the layered architecture used to encapsulate partial reconfiguration capabilities. The top tier is called the *Logic Layer*. This Layer is the upper tier that supports general user-level applications, carrying out hardware-independent logic control on the tasks running on the FPGA platform. In this layer, task routines are available for invocation by user

applications. Reconfiguration requests can be initiated from this level, based on the requirements of the hardware-independent user logic. These reconfiguration requests, including possible new logic function modification and/or physical resources re-arrangements, are all described in a general logic format at this layer. These are subsequently provided to the translation layer to generate the device-dependent reconfiguration data file.

```

Typedef struct tagLUTinfo

/* LUT status information */

unsigned short source[3];

/* The 4 input of the LUT */

/* Current output truth table */

unsigned char iTruthTable[2];

unsigned short cRow;

/* Current row position */

unsigned short cColumn;

/* Current column postion */

unsigned short destination[255]; /* The output of the LUT */

GorFLUT;

/* 0=G LUT; 1=F LUT */

char

/* Modification request */

unsigned short cFutureRow;

/* Future Row */

unsigned short cFutureColumn;

/* Future Column */

char

SwitchLUTFlag;

/*0= no change, 1= move position

between G and F LUT */

unsigned char iFutureTable[2]; /* Future Truth Table */

PositionFlag;

/* 0=no change; 1=update */

char

/* 0=no change; 1=update */

char

TableFlag;

} LUTInfo;

```

Figure 4: LUT Representation at Logic Layer

Figure 4 shows the detailed representation of this logic format. The representation describes the hardware circuit at the Look Up Table (LUT) level. For each LUT, the representation has two parts, the LUT Status Information and the Modification Request. In the LUT Status Information, the LUT inputs and output are labeled. The physical row and column position of the LUT in the FPGA and the logic function inside the LUT are also recorded. The

modification request can be a physical relocation request or a logic function adjustment or both. Besides the details of request information, two modification request flags are also used in this section to advise the translation layer to interpret the request more efficiently. All of the high level applications will only use and modify this device-independent data structure to determine their current state and generate new reconfigurations requests. The reconfiguration requests containing all the LUT information generated at the Logic Layer will generate the device-dependent reconfiguration data file at the Translation Layer. Depending on the complexity of these high-level applications, these can run either in standalone mode on the on-chip CPU core inside the FPGA, or on an external host PC with the on-chip CPU core running simultaneously using a loosely-coupled structure.

The middle tier is referred to as the Translation Layer. In this layer, the general logic descriptions for a palette of tasks are translated into specific physical details as a reconfiguration data file by a hardware-dependent mapping engine. After the partial reconfiguration tasks generation request is made by the user logic from the Logic Layer at runtime, the general information contained in these requests must be translated into a hardware-dependent configuration data file. The original list of partial reconfiguration tasks may include the origin design netlist, physical area allocation, re-allocation and/or direct logic modification. This translation enables the Reconfiguration Layer to execute the reconfiguration requests on the FPGA device. The Translation Layer contains a mapping engine to interpret all of the general representations passed from the upper layer into an actual reconfiguration data file.

Figure 5 shows the details of the translation process. The Translation Layer always stays in the idle state until a new request is sent from the Logic Layer. A new request is always accompanied by an LUT list. Based on the modification request specified in the contents of each

element of the LUT data structure, the status of each LUT is updated. The modification request is then cleared and the corresponding translation engine indicator will be set if necessary. Based on the two translation engine indicators, the corresponding area and logic translation engine will be called to map the general information into device related data. The actions in the dashed boxes in Figure 5 will be processed only when the corresponding flags or indicators are set.

Figure 5: Translation Process Flow Diagram

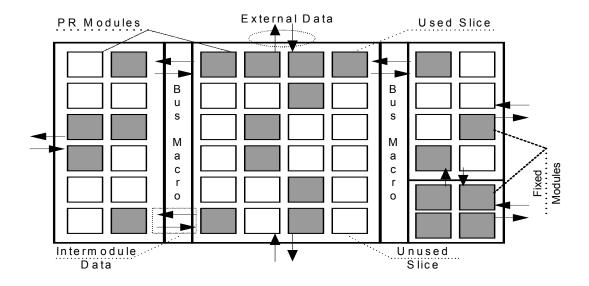

Currently, in the prototype Translation Layer, both the one-dimensional (1D) and twodimensional (2D) area management mapping processes still rely on the Xilinx toolset. The physical resource area management constraints are generated and modified directly by the upper layer logic, and then translated into standard text based constraint inputs by the translation engine in this layer. After the new constraint file is generated, the Xilinx tools are invoked by the translation engine via a shell script. This will automatically run the task in the background to perform the placement and routing for the module without manual input. The Figure 5 shows the details of the translation process. Currently, in the Translation Layer, both the 1D and 2D area management mapping process still rely on the Xilinx toolsets. These physical resource area management constraints are created and modified directly by upper layer logic then translated into standard text based constraint input by the translation engine in this layer. After the new constraint file is generated, the Xilinx toolsets will be called as the other part of translation engine by a shell script. This will run the task at background automatically to perform the placement and routing for the module without manual input.

On the other hand, logic modifications can be translated on either an available partial reconfiguration file or on the currently active configuration data in the device directly without involvement of the Xilinx tools. When the partial reconfiguration file is processed, the Translation Layer will map the top-level logic request directly into the file and then send it to the Reconfiguration Layer interface to be downloaded to the device.

This decouples the bottom layer's hardware-specific considerations from the application's user logic. It also incorporates the online run-time spatial management information into the corresponding partial reconfiguration data file so that when multiple modules need to be reconfigured, the physical area can be reorganized and optimized. With the existence of such a layer, adjustments for changes to the hardware devices or components can be accomplished by

modifications of the mapping engine in the Translation Layer without influencing the top-level Logic Layer.

The bottom tier comprises the *Reconfiguration Layer*. This layer of an autonomous architecture includes the hardware platform and the low-level communication APIs. The hardware platform includes *system resources* and *operational resources*. The system resources include all the external peripherals such as the SRAM, which is a shared memory and can be accessed by both Host PC and FPGA, and the communication interface, such as RS232. The system resources can also contain an on-chip CPU core as the embedded control element and the on-chip Block RAMs, based on design specifications. The operational resources are the actual reconfigurable LUTs inside the FPGA. It can be further conceptually partitioned into two subset region, a *fixed resource subset* that held constant during the entire process and are used to control the on-chip data communications and on-board peripherals, and a *reconfigurable resource subset* that is used for the user-defined partial reconfiguration applications.

The configuration bitstream is downloaded to the targeted FPGA reconfigurable units from the hardware interfaces at this layer when either the initial configuration or the run-time partial reconfigurations are carried out. Input and output data of the FPGA is also passed between the logic control and the bottom FPGA reconfigurable units areas through this path for the functional throughput of the task routines during operation. Block or External RAMs may be used to buffer configuration data in this layer to accelerate the transfer process through pipelining and buffering. The details of the system design and verifications will be discussed in Chapter 4.

### 3.3 Dynamic Control Flow

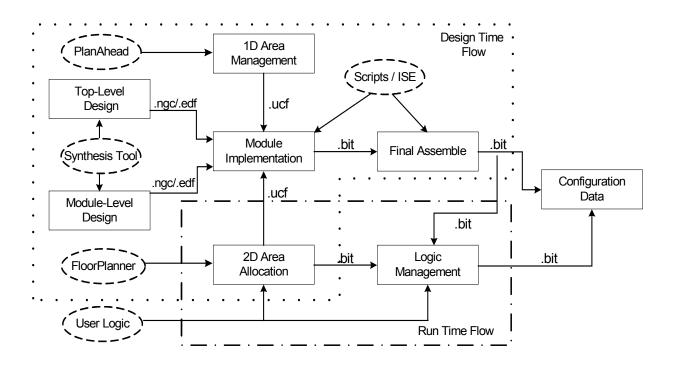

Figure 6: Logic Control Flow

A logic control flow has also been designed for the MRRA as shown in Figure 6. This control flow has integrated a *Module-based Flow* adopted from the standard Xilinx [72] flow with area management ability and the direct bit management process, which we named as a *Frame-based Flow*. This flow allows different pieces, or "modules," of a design to be independently developed and later merge these modules into one FPGA design and reconfigure and modify them individually later at run-time and it provides the potential full autonomous flexibility by using the translation engine from the lower layer without necessary manual input through GUI interface.

As shown in the Figure 6, a full design needs to carry out first at design time. The full hardware system is partitioned into modules and designed from the top view to the bottom.

Meanwhile, *One-Dimensional Area Management* is performed on the full physical FPGA device by partitioning it into multiple 1D column-based rectangles, in which the fixed and reconfigurable modules will be arranged based on the size of each module and the specified area constraints. Then all these top views and modules are implemented and verified individually. The size of each module will be optimized by additional *Two-Dimensional Area Allocation* placements inside each module. The Optimized partial reconfiguration bitstream for the specific modules are also generated. Finally, all the individual modules are created by *Final Assembly* based on the top-level view and are ready to be downloaded to the FPGA device as Configuration Data bitstreams.

After the initial bitstream is downloaded, based on the user logic control, the precompiled partial bitstream can be monitored by the algorithms in the Logic Layer and updated directly to the device for dynamic reconfiguration when necessary. On the other hand, new modification requests can be generated by the user logic in the form of hardware independent general representation at run-time. Although the boundary of each module is fixed, the physical logic resources inside each module can be re-allocated at runtime. Logic function modification request for each Look UP Table (LUT) inside modules can be generated based on the user requirement as well. Both requests from the Logic Layer will eventually wait for the translation engine from lower layer to interpret to the corresponding configuration date file and reconfigured by the Reconfiguration Layer.

#### 3.3.1 Adopted Module Based Partial Reconfiguration Flow

As delineated by the dashed area in Figure 6, Module-based Partial Reconfiguration Flow is a basic flow primarily used at design time. This flow is adapted from the flow proposed by Xilinx. This flow allows different elements referred to as modules of a design to be independently developed and later merged into one FPGA design. This allows the individual reconfiguration and modification of the modules at run-time. Additionally, it provides the potential for full autonomy and flexibility using the translation engine from the lower layer without the need for GUI-based manual input. For this flow, the reconfigurable fabric of the FPGA is partitioned into column-based rectangular regions in which the fixed and reconfigurable modules will be arranged based on specified area constrains. The reconfigurable modules have the following properties:

- The reconfigurable module height is always the full height of the device. The width ranges from a minimum of four slices to a maximum of the full-device width, in fourslice increments.

- 2) To help minimize problems related to design complexity, the number of reconfigurable modules should be minimized, which means the number of slice columns divided by four is the only real limit to the number of defined reconfigurable module regions.

- 3) A reconfigurable module's boundary cannot be changed. The position and region occupied by any single reconfigurable module is always fixed.

- 4) Reconfigurable modules communicate with other modules, both fixed and reconfigurable, by using a special bus macro.

- 5) The implementation must be designed so that the static portions of the design do not rely on the state of the module under reconfiguration while reconfiguration is taking place.

The implementation should ensure proper operation of the design during the reconfiguration process. Explicit handshaking logic may be required.

- 6) The states of the storage elements inside the reconfigurable module are preserved during and after the reconfiguration process. On the other hand. If set/reset initialization is required for the reconfigurable module, user-defined set/reset signals should be defined in the source HDL.

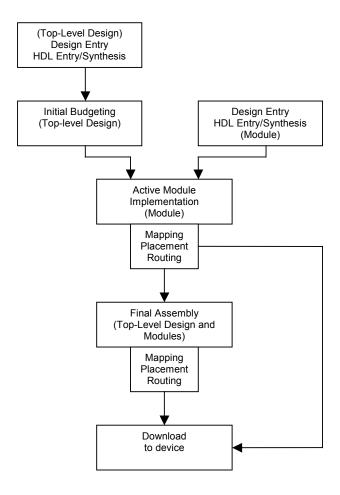

Figure 7: Module-Based Flow

A detailed description of this design flow is shown in Figure 7. A full design is first carried out, implemented and verified from top level to bottom modules, some of which are fixed while others are designated as reconfigurable. This generates the *Top-level Design* and *Module-level Design*. After the device is downloaded with initial power-up configuration, reprogram reconfigurable modules as needed with individual (or partial) bitstreams then can be updated to the device.

The communication between a reconfigurable module and a fixed module, or between the reconfigurable ones must go through dedicated wires, i.e. in order to maintain correct connections between the modules, must use the same physical wires. This is why the *bus macro* is used. By positioning the bus macro exactly straddling the dividing line between two adjacent modules, the inter-module connection is established. However, the standard bus macro provided by Xilinx can only establish communication between two modules next to each other. When a communication channel is required for two separate modules, i.e. one or more modules physically placed between them, a signal needs to pass through the reconfigurable modules connecting the two modules with standard bus macros used on both sides to make that connection. This effectively requires creation of an intermediate signal that is defined in the reconfigurable module. This signal cannot be actively used during the time the intermediate reconfigurable module is being configured.

To avoid this dilemma, a custom-made bus macro is designed. By extending the dedicated wires, the new bus macro provides communication between modules across multiple module boundaries. The dedicated routing that used by the bus macro going through the modules will be also reconfigured with the intermediate reconfigured module. But since it will be placed

in exactly the same way before, during, and after the reconfiguration, and since this is done glitch free, the bus will stay intact. Therefore, the communication will not broken during reconfiguration process since the wires going through the modules being reconfigured never change.

### 3.3.2 Frame Based Partial Reconfiguration Flow

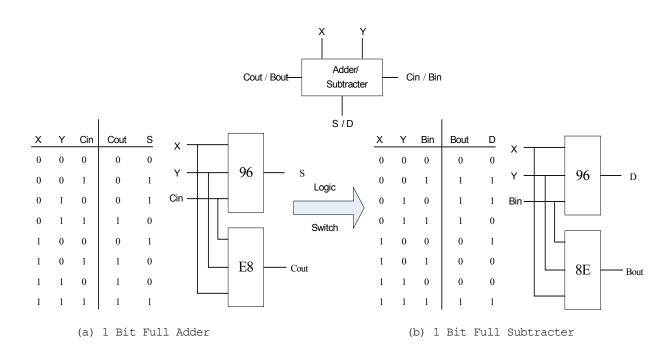

Figure 8: A Simple Logic Modification Example

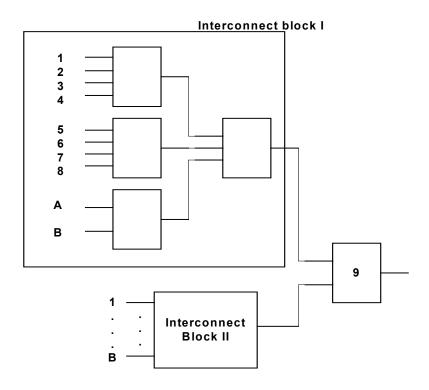

In the basic Module-based flow, all the tasks that need to be reconfigured at runtime are required to be precompiled at design time and reside originally in non-volatile storage. However, in some instances, hardware tasks may have very similar or even identical logic function structures as well as input and output signals. Such scenarios typically can occur in hash, encryption, and encoding/decoding applications, such as [44], [58], [59], [63], etc. Figure 8 illustrates this concept with a straightforward example. Both a one-bit full adder and a one-bit