## AUTONOMOUS RECOVERY OF RECONFIGURABLE LOGIC DEVICES USING PRIORITY ESCALATION OF SLACK

by

## NAVEED IMRAN M.S. Electrical Engg. University of Central Florida, Orlando, 2010

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering in the College of Electrical Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2013

Major Professor: Ronald F. DeMara

© 2013 Naveed Imran

## ABSTRACT

Field Programmable Gate Array (FPGA) devices offer a suitable platform for survivable hardware architectures in mission-critical systems. In this dissertation, active dynamic redundancy-based fault-handling techniques are proposed which exploit the dynamic partial reconfiguration capability of SRAM-based FPGAs. Self-adaptation is realized by employing reconfiguration in detection, diagnosis, and recovery phases.

To extend these concepts to semiconductor aging and process variation in the deep submicron era, resilient adaptable processing systems are sought to maintain quality and throughput requirements despite the vulnerabilities of the underlying computational devices. A new approach to autonomous fault-handling which addresses these goals is developed using only a uniplex hardware arrangement. It operates by observing a health metric to achieve *Fault Demotion using Reconfigurable Slack (FaDReS)*. Here an autonomous fault isolation scheme is employed which neither requires test vectors nor suspends the computational throughput, but instead observes the value of a health metric based on runtime input. The deterministic flow of the fault isolation scheme guarantees success in a bounded number of reconfigurations of the FPGA fabric.

FaDReS is then extended to the *Priority Using Resource Escalation (PURE)* online redundancy scheme which considers fault-isolation latency and throughput trade-offs under a dynamic spare arrangement. While deep-submicron designs introduce new challenges, use of adaptive techniques are seen to provide several promising avenues for improving resilience. The scheme developed is demonstrated by hardware design of various signal processing circuits and their implementation on a Xilinx Virtex-4 FPGA device. These include a Discrete Cosine Transform (DCT) core, Motion Estimation (ME) engine, Finite Impulse Response (FIR) Filter, Support Vector Machine (SVM), and Advanced Encryption Standard (AES) blocks in addition to MCNC benchmark circuits. A

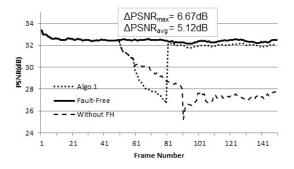

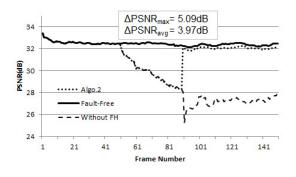

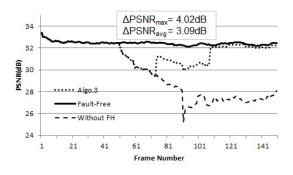

significant reduction in power consumption is achieved ranging from 83% for low motion-activity scenes to 12.5% for high motion activity video scenes in a novel ME engine configuration. For a typical benchmark video sequence, PURE is shown to maintain a PSNR baseline near 32dB. The diagnosability, reconfiguration latency, and resource overhead of each approach is analyzed. Compared to previous alternatives, PURE maintains a PSNR within a difference of 4.02dB to 6.67dB from the fault-free baseline by escalating healthy resources to higher-priority signal processing functions. The results indicate the benefits of priority-aware resiliency over conventional redundancy approaches in terms of fault-recovery, power consumption, and resource-area requirements. Together, these provide a broad range of strategies to achieve autonomous recovery of reconfigurable logic devices under a variety of constraints, operating conditions, and optimization criteria.

To all those whose innovations and efforts make the world a better place to live

## ACKNOWLEDGMENTS

I am deeply grateful to my advisor Dr. Ronald F. DeMara whose continuous guidance, encouragement, and support made this dissertation possible. I really appreciate his exceptional advice, valuable time and very generous attitude throughput my doctorial studies.

I would like to thank Drs. Wasfy B. Mikhael, Mingjie Lin, Jiann-Shiun Yuan, and Christopher D. Geiger for their great suggestions and for their time to evaluate this dissertation as my advisory committee members.

I would also like to thank Dr. Jooheung Lee at Hongik University, Seoul, South Korea, for his valuable input during my collaborative work with him. I thank my friends for my unforgettable happy memories during my stay in Orlando.

Finally, I would like to thank my parents and sisters for their endless love, support and passionate encouragement throughout my life. I am greatly thankful to my wife and sons for their unremitting love, patience and support throughout this journey.

# TABLE OF CONTENTS

| LIST OF FIGURES                              |

|----------------------------------------------|

| LIST OF TABLES                               |

| LIST OF ACRONYMS                             |

| LIST OF NOTATIONS                            |

| CHAPTER 1: INTRODUCTION                      |

| Need for Reliability and Survivability 1     |

| Characteristics of Fault-Tolerant Systems 4  |

| Soft Resilience of Signal Processing Systems |

| Quality-Oriented Architectural Adaptations   |

| Contributions of the Dissertation            |

| CHAPTER 2: RELATED WORK                      |

| Static Redundancy                            |

| Resource Testing by BIST                     |

| System-Level Diagnosis                       |

| Evolvable Hardware Techniques                                  | 19 |

|----------------------------------------------------------------|----|

| Reconfiguration Techniques                                     | 21 |

| Comparison of Techniques                                       | 22 |

| CHAPTER 3: ADAPTIVE AREA MANAGEMENT FOR LOCAL PERMANENT DAM-   |    |

| AGE                                                            | 25 |

| A Self-Configuring TMR Scheme utilizing Discrepancy Resolution | 25 |

| The SCDR Approach                                              | 26 |

| Encoding Representation of the TMR Pathways                    | 28 |

| Fitness Function                                               | 28 |

| Fitness Evaluation                                             | 29 |

| Fitness Selection                                              | 30 |

| Genetic Operators                                              | 30 |

| Experiment Design                                              | 31 |

| Simulation Results                                             | 32 |

| Intrinsic Hardware Evaluation using SCDR                       | 32 |

| Faults-Aware Simulation Paradigm                               | 34 |

| Performance Bound Comparison to Exhaustive Search              | 36 |

| Heterogeneous Concurrent Error Detection ( <i>h</i> CED) Based on Output Anticipation | 36 |

|---------------------------------------------------------------------------------------|----|

| Alternate CED Arrangements                                                            | 38 |

| The Baseline Setup                                                                    | 41 |

| Spatial Heterogeneous CED                                                             | 43 |

| Temporal Heterogeneous CED                                                            | 45 |

| Amorphous Slack (AS) Fault-Handling Methodology                                       | 47 |

| Simulation Results                                                                    | 49 |

| Case Study-1: Video Encoder                                                           | 50 |

| Case Study-2: Edge Detector                                                           | 52 |

| Distance-Ranked Fault Identification (DRFI)                                           | 53 |

| Fault Detection                                                                       | 53 |

| System-Level Diagnosis of Hardware Configurations                                     | 54 |

| Exhaustive Evaluation                                                                 | 57 |

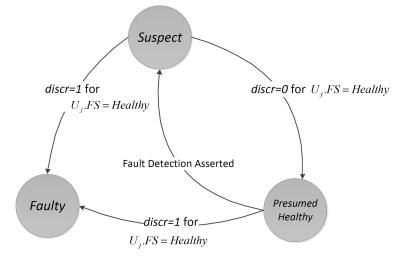

| The SFH Fitness States Transitions Diagram Method                                     | 59 |

| The DRFI Approach                                                                     | 64 |

| Fault Recovery Results                                                                | 68 |

| Experiment-1: MCNC benchmark circuits                                                 | 69 |

| Experiment-2: DCT core                                                         | 74 |

|--------------------------------------------------------------------------------|----|

| Experiment-3: Partial Recovery                                                 | 75 |

| CHAPTER 4: SOFT-RESILIENCE USING AN ONLINE MULTI-OBJECTIVE GA 7                | 77 |

| Self-Aware Signal Processing Architectures                                     | 78 |

| Previous Techniques of Soft Resilience                                         | 31 |

| Problem Formulation and Methodology                                            | 34 |

| Multi-Objective function                                                       | 38 |

| Throughput Degradation                                                         | 39 |

| Power Consumption                                                              | 90 |

| Guidance Function                                                              | 90 |

| Execution Results                                                              | 93 |

| Synthetic Nodes Simulation                                                     | 93 |

| A Computer Vision Case-Study: Support Vector Machine (SVM)                     | 96 |

| An Image/Video Processing Case-Study: Discrete Cosine Transform 10             | 03 |

| Comparison of Proposed Approach with Conventional Fault-Handling Techniques 10 | )7 |

| Modular Redundancy                                                             | )7 |

| BIST-based Evaluation                                                          | 07 |

| CHAPTER 5: POWER AND QUALITY-ORIENTED SOFT-RESILIENCE          |

|----------------------------------------------------------------|

| Motion Estimation                                              |

| Previous Techniques of Low Power ME                            |

| Activity Based Resource Allocation Framework                   |

| Computational Demand Anticipation                              |

| Faults Mitigation Strategy                                     |

| Detection of Hardware Faults                                   |

| Fault Diagnosis using Dynamic Redundancy                       |

| Fault Recovery                                                 |

| Case-Study : FPGA-based Implementation of Full Search FHME     |

| Evaluation Results of FHME                                     |

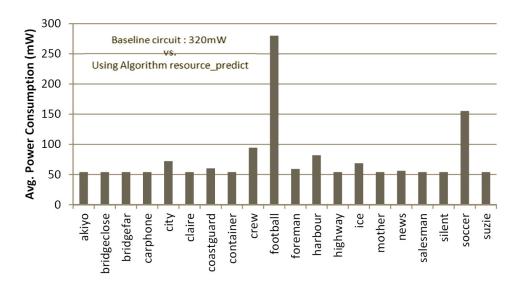

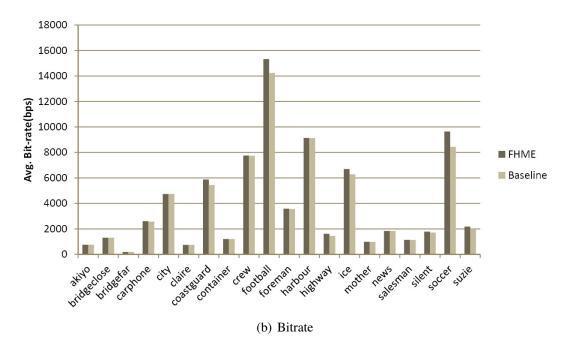

| Energy Saving in Reconfigurable Design                         |

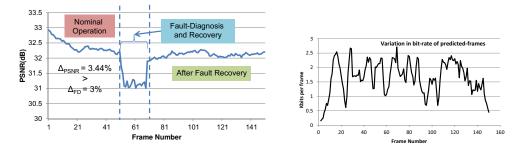

| Online Recovery Results of FHME core                           |

| CHAPTER 6: HEALTH METRIC BASED DYNAMIC RESOURCE ALLOCATION 136 |

| Fault-Handling Method                                          |

| Functional diagnosis to record discrepancy history             |

| Reconfiguration Algorithm 1: Divide-and-Conquer Method         |

| Reconfiguration Algorithm 2: FaDReS                              |

|------------------------------------------------------------------|

| Hardware Organization in FaDReS Technique                        |

| Hardware Components                                              |

| Fault Detection, Isolation and Recovery                          |

| Experimental Results                                             |

| Performance Improvement                                          |

| Power Analysis                                                   |

| Diagnosis by voting                                              |

| Diagnosis by Comparison                                          |

| Reconfiguration Algorithm 3: PURE                                |

| Diagnostic Flow                                                  |

| Fault Detection Criteria                                         |

| PSNR as a Health Metric                                          |

| Output Discrepancy as a Health Metric                            |

| PURE Functional Testing as Compared to Physical Resource Testing |

| Experimental Results                                             |

| Case Study-1: Prioritized elements of the DCT core               |

| Case Study-2: Fault Resilience of a Multi-PE Design | 183   |

|-----------------------------------------------------|-------|

| Energy Duty Cycle                                   | 185   |

| CHAPTER 7: CONCLUSION                               | . 187 |

| Technical Summary                                   | 187   |

| Scope and Limitations                               | 192   |

| Future Directions                                   | 195   |

| The Road Ahead                                      | 196   |

| LIST OF REFERENCES                                  | . 198 |

# **LIST OF FIGURES**

| 1.1  | Characteristics of an ideal autonomous recovery technique                      | 6  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | System block diagram illustrating the scope of reconfiguration techniques      | 9  |

| 1.3  | A roadmap diagram illustrating the techniques evaluated herein                 | 12 |

| 3.1  | Circuit realization to employ the SCDR recovery mechanism                      | 27 |

| 3.2  | Mapping between an individual and configuration                                | 28 |

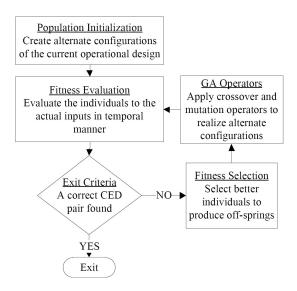

| 3.3  | The evolutionary recovery process in the context of a standard GA [1] $\ldots$ | 31 |

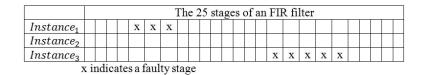

| 3.4  | A faulty TMR configuration                                                     | 32 |

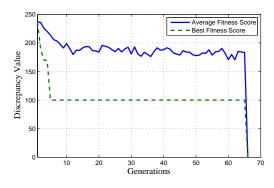

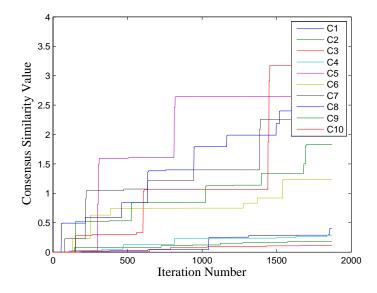

| 3.5  | The consensus fitness history of the population                                | 33 |

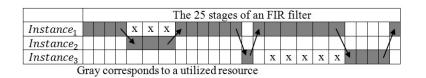

| 3.6  | A repaired instance in the new configuration                                   | 33 |

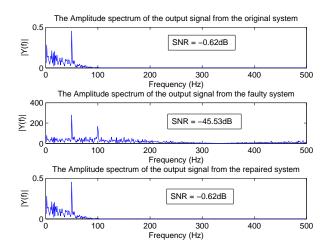

| 3.7  | The amplitude spectrum of the output signal                                    | 35 |

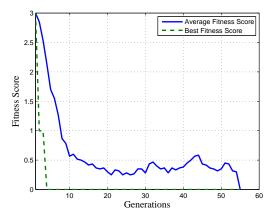

| 3.8  | The absolute fitness history of the population                                 | 35 |

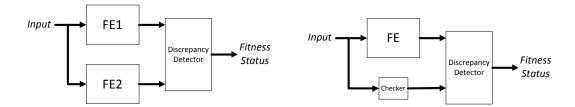

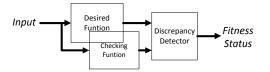

| 3.9  | Various CED configurations                                                     | 37 |

| 3.10 | The DCT matrix                                                                 | 39 |

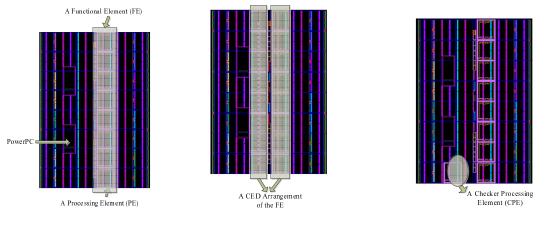

| 3.11 | Floorplan of various FE configurations realizing a DCT module                  | 42 |

| 3.12 | Spatial heterogeneous CED arrangement realizing a DCT module                   | 43 |

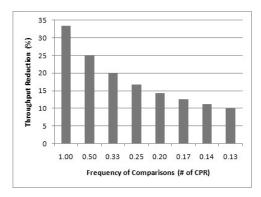

| 3.13 | Temporal heterogeneous CED arrangement of the DCT module                         | 46 |

|------|----------------------------------------------------------------------------------|----|

| 3.14 | Throughput reduction of temporal Heterogeneous CED arrangement                   | 47 |

| 3.15 | Fault isolation using AS technique                                               | 50 |

| 3.16 | An operational example in a faulty scenario of video encoder                     | 51 |

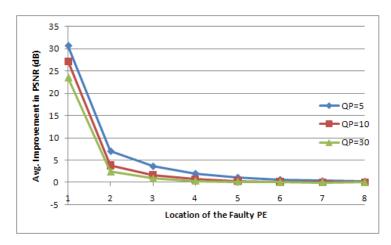

| 3.17 | Improvement in average PSNR after fault recovery                                 | 52 |

| 3.18 | Gaussian kernel and qualitative results                                          | 53 |

| 3.19 | A CED arrangement of a functional element                                        | 54 |

| 3.20 | Online fault-diagnosis strategies evaluated herein                               | 55 |

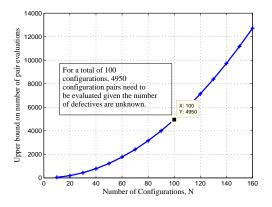

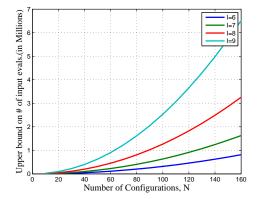

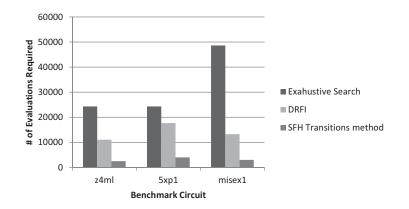

| 3.21 | Fault-diagnosis cost of exhaustive evaluation method                             | 58 |

| 3.22 | Fitness states of a design configuration during a circuit's life time            | 59 |

| 3.23 | Identifying healthy configurations in a suspect pool                             | 61 |

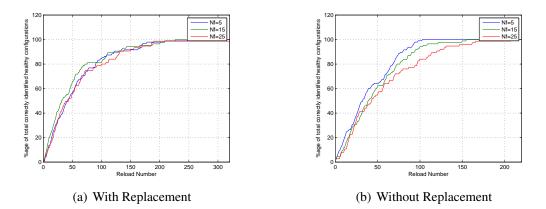

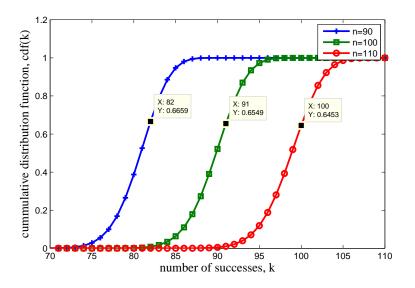

| 3.24 | Probability of success for various trials with replacement                       | 63 |

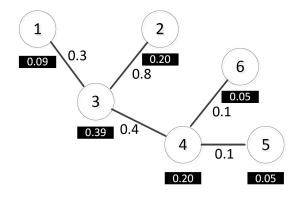

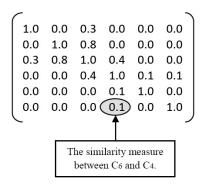

| 3.25 | An example of configurations ranking                                             | 67 |

| 3.26 | An example of fault-injection into the simulation model of the circuit           | 68 |

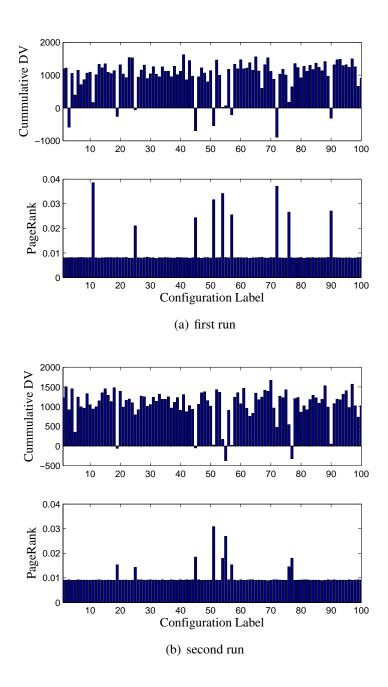

| 3.27 | CDV, and PR of various configurations for different simulation runs (a), and (b) | 71 |

| 3.28 | The discrepancy history of various configurations of the circuit                 | 72 |

| 3.29 | A comparison of fault-diagnosis methods for various MCNC benchmarks              | 73 |

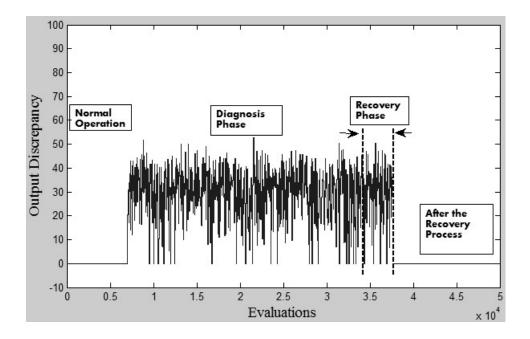

| 3.30 | An operational example of a circuit on a $x10^4$ evaluations scale              |

|------|---------------------------------------------------------------------------------|

| 3.31 | An image in the frame memory of video encoder                                   |

| 3.32 | Partial recovery results of the scheme                                          |

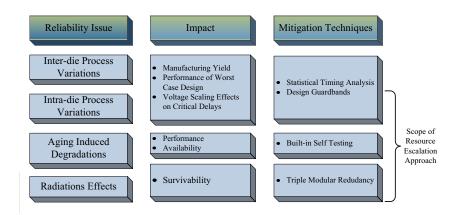

| 4.1  | Reliability issues of digital systems built with deep submicron devices 78      |

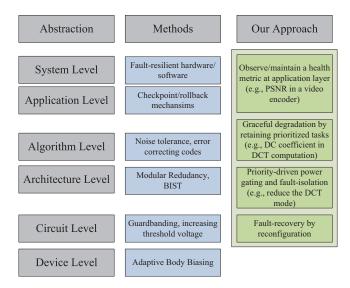

| 4.2  | Hierarchy of fault-mitigation techniques at various abstraction levels 82       |

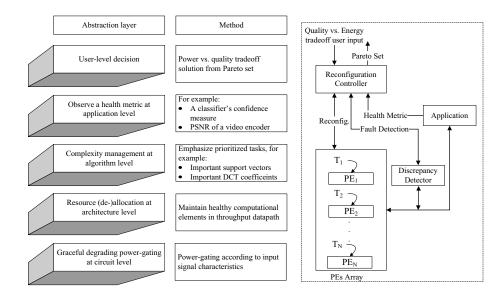

| 4.3  | Cross-layer fault-handling architecture with hierarchical support               |

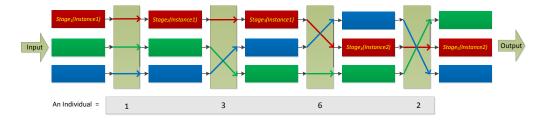

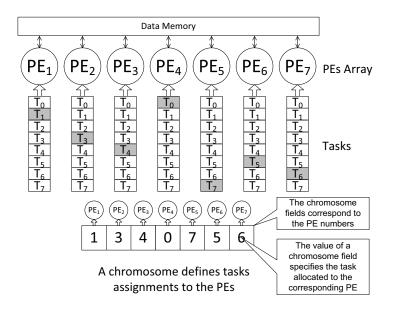

| 4.4  | An array of 7 configurable PEs and its genetic representation                   |

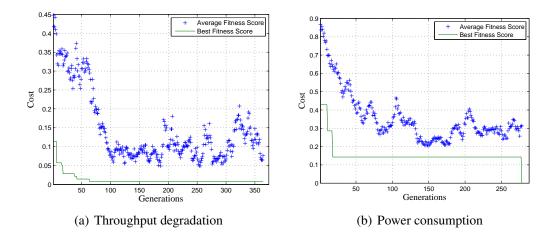

| 4.5  | Cost functions                                                                  |

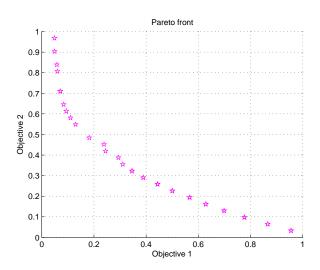

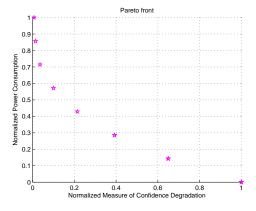

| 4.6  | Pareto set of solutions for the synthetic graph MOOE problem                    |

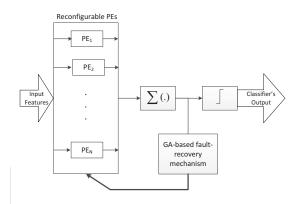

| 4.7  | Functional block arrangement in a Self-Healing SVM case study 97                |

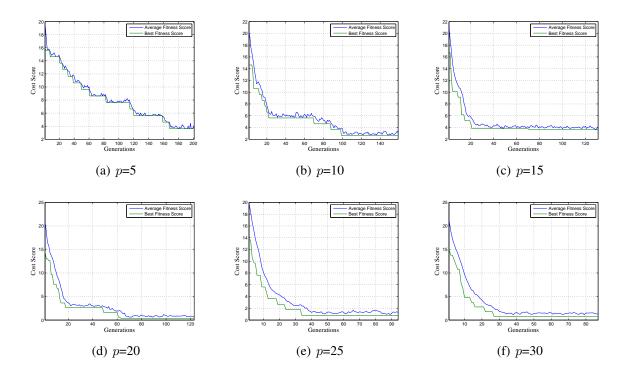

| 4.8  | Effect of population size on recovery results                                   |

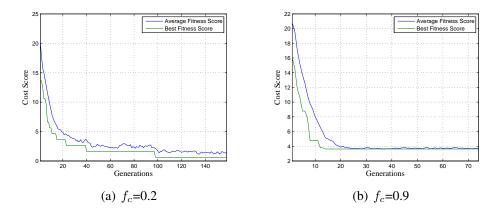

| 4.9  | Effect of crossover fraction on convergence property of the GA, $p=25$ 100      |

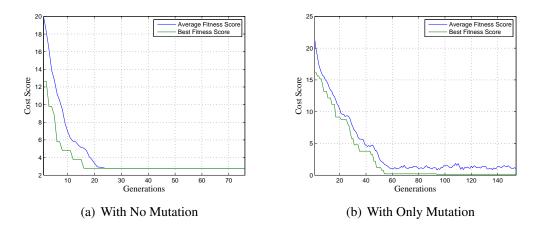

| 4.10 | Effect of mutation on convergence property of the GA                            |

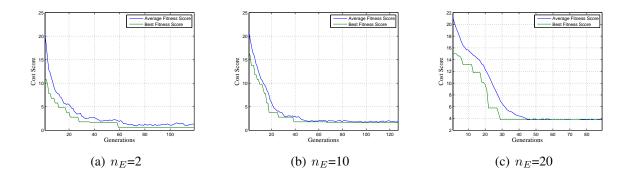

| 4.11 | Effect of elite count on convergence property of the GA, $p=25$ , $f_c=0.5$ 102 |

| 4.12 | Pareto set of solutions for the SVM MOOE problem                                |

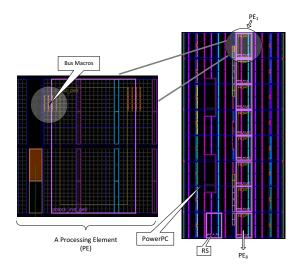

| 4.13 | Floorplan of DCT module for Virtex-4 device                                     |

| 4.14 | Fault recovery results for various 4cif test video sequences [2]                |

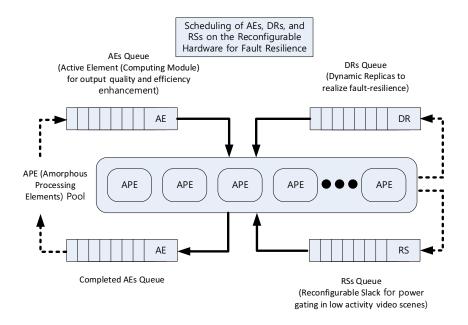

| 5.1  | Flexible configuration of Amorphous Processing Elements (APEs) 111                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2  | Computation of a motion vector                                                                                                                     |

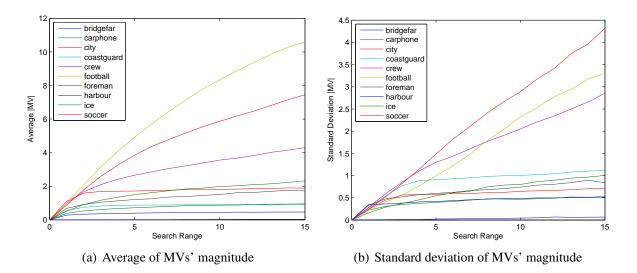

| 5.3  | Effect of search range on motion vector's values for various video sequences . 116                                                                 |

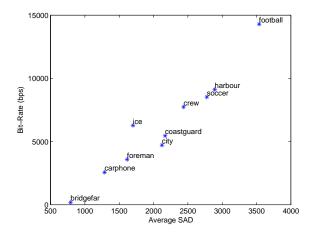

| 5.4  | Effect of ME's SAD error on encoder's bitrate, $QP = 10$                                                                                           |

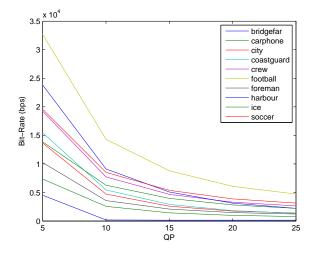

| 5.5  | The effect of QP on bitrate, $S = 15 \dots $ |

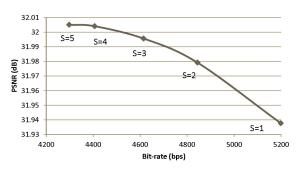

| 5.6  | RD curve showing the effect of increasing search range                                                                                             |

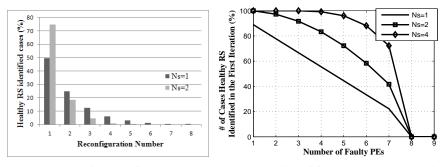

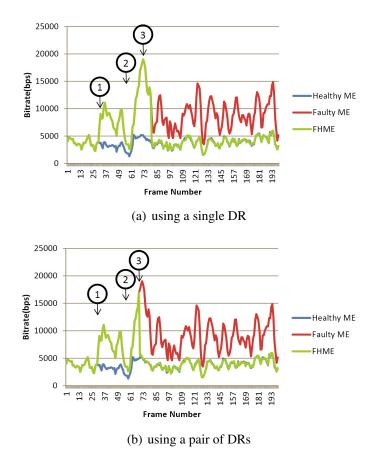

| 5.7  | Fault injection results for container video sequence                                                                                               |

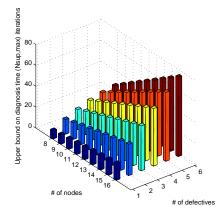

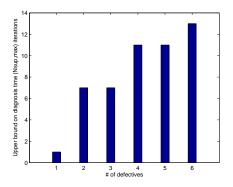

| 5.8  | The effect of $N_f$ on iterations required for the fault-diagnosis algorithm $\ldots$ 124                                                          |

| 5.9  | Hardware architecture of FHME                                                                                                                      |

| 5.10 | Evaluation Setup: FPGA based FHME's interface with on-chip processor 128                                                                           |

| 5.11 | Power saving at the cost of increased bitrate for Soccer video sequence 130                                                                        |

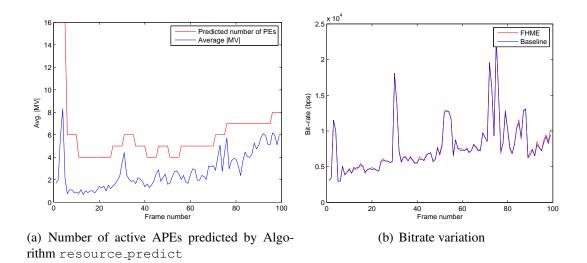

| 5.12 | Dynamic computational resource prediction for crew video sequence 131                                                                              |

| 5.13 | Energy saving results of FHME with low overhead of bitrate                                                                                         |

| 5.14 | Power and quality tradeoff results for city.4cif video sequence 133                                                                                |

| 5.15 | An example of online fault-handling                                                                                                                |

| 6.1  | Self-adapting resource escalation of the FPGA device                                                                                               |

| 6.2  | Overview of recovery algorithms evaluated herein and the evaluation approach 140                                                                   |

| 6.3  | Divide-and-conquer method for fault diagnosis                                 |

|------|-------------------------------------------------------------------------------|

| 6.4  | Various reconfiguration instants in the divide-and-conquer approach 146       |

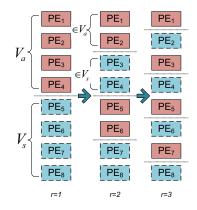

| 6.5  | CPDC demonstrating diagnosis benefit of additional slacks                     |

| 6.6  | The FaDReS approach applied to an H.263 architecture                          |

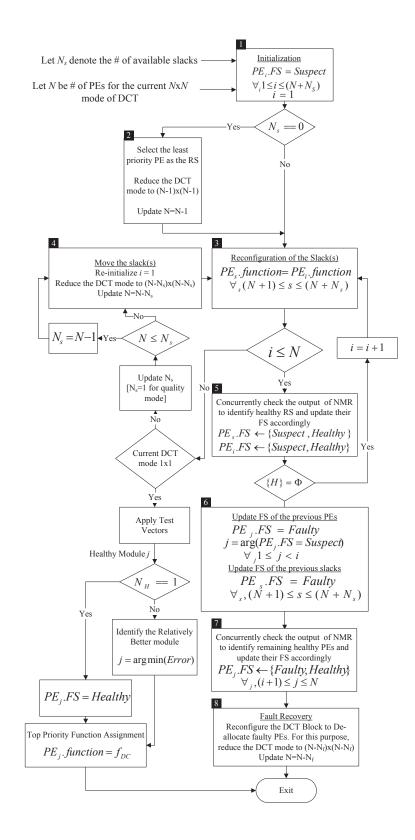

| 6.7  | The fault isolation and recovery process flow chart                           |

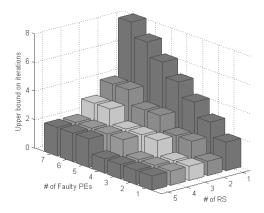

| 6.8  | Upper Bound on number of iterations for fault isolation                       |

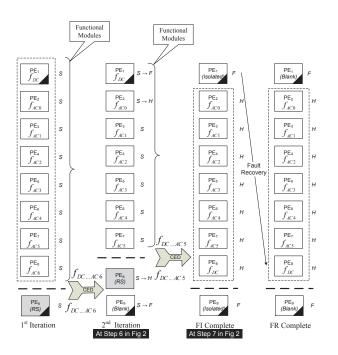

| 6.9  | An example of the fault isolation and recovery scheme                         |

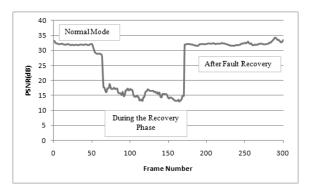

| 6.10 | An operational example of the video encoder                                   |

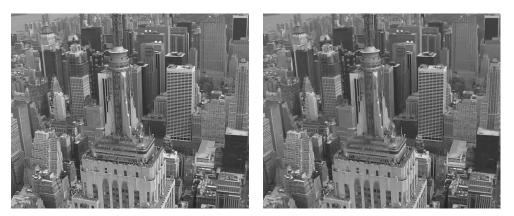

| 6.11 | Qualitative results on sequence from ASU video library [3]                    |

| 6.12 | Fault-diagnosis in the FaDReS approach                                        |

| 6.13 | The diagnosability of a topology with various reconfiguration iterations 166  |

| 6.14 | An example of fault diagnosis in PURE approach                                |

| 6.15 | The worst case scenario for the diagnostic phase with two defective nodes 167 |

| 6.16 | The impact of faults on PSNR and image quality                                |

| 6.17 | Diagnosis latency of the PURE approach for $N_s = 1$                          |

| 6.18 | Diagnosis latency of the PURE approach for $N_s = 2, N = 8$                   |

| 6.19 | PSNR and bit-rate of the encoder employing PURE                               |

| 6.20 | Operational examples of the three algorithms                |

|------|-------------------------------------------------------------|

| 6.21 | Floorplan of the AES core for Virtex-4 chip                 |

| 7.1  | The techniques developed herein to meet evaluation criteria |

# LIST OF TABLES

| 2.1 | Comparison of fault-tolerance techniques for SRAM-based FPGAs 22                      |

|-----|---------------------------------------------------------------------------------------|

| 3.1 | Resource utilization for spatial hCED arrangement                                     |

| 3.2 | Resource utilization summary of the DCT core                                          |

| 4.1 | Example of priority values, $\mathbf{P}$ , and healthiness of resources, $\mathbf{H}$ |

| 4.2 | GA paramters                                                                          |

| 4.3 | Fault impact on the classifier output                                                 |

| 4.4 | Fault recovery for <i>Covertype</i> [4] dataset                                       |

| 5.1 | Hardware utilization summary for Virtex-4 FPGA                                        |

| 5.2 | Number of vacated APEs while bitrate within 3% tolerance                              |

| 5.3 | Bitrate of encoded bitstream for foreman video sequence                               |

| 6.1 | Dynamic power consumption of the static design                                        |

| 6.2 | Dynamic power consumption of the reconfigurable design                                |

| 6.3 | Dynamic energy consumption of the PR design during FI phase                           |

| 6.4 | Latency vs. throughput comparisons                                                    |

| 6.5  | Effect of $\Delta_{FD} = 3\%$ tolerance using Failure-Free Resources for city.qcif 172 |

|------|----------------------------------------------------------------------------------------|

| 6.6  | Effect of $\Delta_{FD} = 3\%$ tolerance using PEs with 5% degraded output 172          |

| 6.7  | Fault detection performance ( $\Delta_{FD} = 3\%$ )                                    |

| 6.8  | Quality-oriented fault-diagnosis                                                       |

| 6.9  | Configuration bitstream sizes in DCT core                                              |

| 6.10 | Fault impact in 128 AES Computational FE                                               |

| 6.11 | Utilization summary of the AES design                                                  |

| 7.1  | A summary of the dissertation and lessons learned                                      |

| /.1  |                                                                                        |

## LIST OF ACRONYMS

- ACE Advanced Configuration Environment

- AE Active Element

- **AEs** Active Elements

- **AES** Advanced Encryption Standard

- **APE** Amorphous Processing Element

- APEs Amorphous Processing Elements

- BIST Built-in Self Test

- **CDM** Comparison Diagnosis Model

- **CED** Concurrent Error Detection

- **CLBs** Configuration Logic Blocks

- **CRR** Competitive Runtime Reconfiguration

- CUT Circuit Under Test

- **DCT** Discrete Cosine Transform

- **DMR** Dual Modular Redundancy

- DRFI Distance-Ranked Fault Identification

- **DR** Dynamic Replica

| DRs | Dynamic | Replicas |

|-----|---------|----------|

|-----|---------|----------|

- **DSP** Digital Signal Processing

- ECC Error Correcting Code

- **EM** Electromigration

FaDReS Fault Demotion using Reconfigurable Slack

FIAT Fault Injection and Analysis Toolkit

FPGAs Field Programmable Gate Arrays

FD Fault Detection

FE Functional Element

FI Fault Isolation

FR Fault Recovery

FT Fault Tolerance

FH Fault Handling

FHME Fault-Handling Motion Estimation

GA Genetic Algorithm

GAs Genetic Algorithms

hCED Heterogeneous CED

HDL Hardware Description Language

**ISE** Integrated Software Environment

## ICAP Internal Configuration Access Port

ME Motion Estimation

- MV Motion Vector

- **NUT** Node Under Test

NMR N-Modular Redundancy

**PE** Processing Element

**PEs** Processing Elements

**PSNR** Peak Signal-to-Noise Ratio

**PLB** Programmable Logic Block

**PR** Partial Reconfiguration

**PRR** Partial Reconfiguration Region

PRRs Partial Reconfiguration Regions

PURE Priority Using Resource Escalation

QoS Quality of Service

**QP** Quantization Parameter

**RN** Reconfigurable Node

**RS** Reconfigurable Slack

**SEU** Single Event Upset

**SET** Single Event Transient

SA Stuck At

SCDR Self-Configuring Discrepancy Resolution

**SNR** Signal-to-Noise Ratio

SEUs Single-Event Upsets

SCDR Self-Configuring Discrepancy Resolution

STARs Self-Testing AReas

TDDB Time-Dependent Dielectric Breakdown

**TMR** Triple Modular Redundancy

# LIST OF NOTATIONS

| $\mathbf{G}(V,E)$ | An undirected graph, where V is the set of all nodes, E is the set of edges                 |

|-------------------|---------------------------------------------------------------------------------------------|

| $\mathbf{C}$      | Connectivity matrix                                                                         |

| C(t)              | Connectivity $\mathbf{C}$ at time instant $t$                                               |

| $\Psi$            | Syndrome Matrix                                                                             |

| $\hat{\Phi}$      | Estimated Fitness State Vector                                                              |

| Р                 | Priority Vector                                                                             |

| t(G)              | Diagnosability of G                                                                         |

| d(G)              | Average degree of a node in G                                                               |

| $V_a$             | Set of active nodes                                                                         |

| $V_s$             | Set of Reconfigurable Slack (RS) to diagnose the active nodes by comparison-based diagnosis |

| $V_h$             | Set of healthy nodes                                                                        |

| $V_{NMR}$         | Set for N-Modular Redundancy checking                                                       |

| M                 | Number of PRRs                                                                              |

| $N_a$             | Number of nodes in the datapath (i.e., $ V_a $ )                                            |

| $N_s$             | Number of Reconfigurable Slacks (i.e., $ V_s $ )                                            |

| $N_d$             | Number of defectives                                                                        |

| r                 | Testing arrangement instance (may involve multiple reconfigurations)                        |

| s                 | Slack update instance (a slack is reconfigured with some function)                          |

| t                 | Time instant                                                                                |

| $T_{recon}$       | Reconfiguration Time                                                                        |

| $T_{eval}$        | Evaluation window period                                                                    |

|                   |                                                                                             |

| F                        | Functions assignments vector                                           |

|--------------------------|------------------------------------------------------------------------|

| $F^*$                    | Solution vector $F$ after recovery                                     |

| $T_d$                    | Latency of fault detection                                             |

| $T_{diag}$               | Latency of fault diagnosis                                             |

| $T_{rec}$                | Recovery time                                                          |

| $N_r$                    | Number of testing arrangement instances before the diagnosis completes |

| $N_{sup}$                | Number of slack updates                                                |

| $N_{AE}, N_{DR}, N_{RS}$ | Number of AEs, DRs, and RSs, respectively                              |

| N                        | Total number of APEs defined in the reconfigurable device              |

| Ν                        | Macroblock's size (N $\times$ N)                                       |

| $\Phi$                   | Predicted fitness status (0:healthy, 1:faulty, or x:suspect)           |

| $V_T$                    | APEs in the pool under test                                            |

| S                        | Search Range                                                           |

| n                        | Number of SAD's computed by an APE per clock cycle                     |

| TCAE                     | Current Testing Candidate APE in the active datapath (i.e., AE)        |

| $T_r$                    | Time to reconfigure an APE                                             |

| $\hat{S}$                | Search range anticipated                                               |

| $\mu$                    | Average magnitude of motion vectors over a video frame                 |

| $	au_{SAD}$              | Threshold to increased search range                                    |

| $\Delta_{SAD}$           | Difference in SAD values                                               |

## **CHAPTER 1: INTRODUCTION**

Survivability, reliability, and availability are indispensable characteristics of mission critical digital systems. To achieve these characteristics in electronics systems used in space, satellite, or other difficult to access environments where the manual intervention may not be feasible, autonomous repair capability becomes a desirable property. This chapter highlights the significance of the problem, and provides an overview of the techniques widely used in fault-tolerant designs on reconfigurable platforms. Afterwards, innovations of the proposed resilience approaches are identified and listed in the Contribution of Dissertation section.

### Need for Reliability and Survivability

With the continued reducing feature size of semiconductor technology, device reliability and system survivability for mission-critical systems poses increasingly significant challenges [5][6][7] [8]. Error-resiliency and self-adaptability of future electronic systems are subjects of growing interest [5][9]. In some situations, even survivability in the form of graceful degradation is desired if a full recovery cannot be achieved. Transient, so called *soft*, errors as well as permanent, *hard*, errors in electronic devices caused by aging or radiation in space environment require autonomous mitigation as manual intervention may not be feasible [10]. The reliability problem of highly complex VLSI systems in sub-90 nanometer process, caused by soft and hard errors, is increasing. Therefore, the importance of addressing reliability issues is growing to sustain a high level of integration, performance, and transistor density on chip.

The self reconfiguration capability of Field Programmable Gate Arrays (FPGAs) is appealing for building fault-tolerant circuits. Various configurations of a design can be studied for throughput,

power, and reliability analysis. Fault recovery of FPGA-based designs can be realized by employing fault-free logic resources at runtime. Given some faulty resources in a particular region in an FPGA chip, the circuit can be repaired by assigning its functionality to a pristine area in the chip. Equivalently, if a circuit realized by a particular configuration-bitstream manifests faults, an alternate configuration-bitstream utilizing only the fault-free resources can be downloaded into a chip.

Another reason for research interest in fault-tolerance of FPGA based design is due to their popularity in mission critical systems [11]. The regular structure of an FPGA-fabric is amenable to reconfiguration-based recovery. A high regularity of FPGA logic resources allows movement of a function implemented over a defective region to a fault-free region [12] [13] [14] [15]. FPGAs are popular among space exploration community for its reconfigurability [10] [16]. On the other hand, FPGAs are also susceptible to transient as well as permanent faults, for example Single Event Upset (SEU) in the configuration memory, and Stuck At (SA) faults in the logic resource [17]. These errors can occur while operating in deep space environments when FPGAs are subjected to cosmic rays and high energy radiations. For fault detection capability, a duplex of the design can be instantiated on the chip and a discrepancy in the output can be monitored via a discrepancy detector [18].

At the *circuit level*, scaling the supply voltage  $V_{dd}$  and threshold voltage  $V_t$  have been effective methods to drastically reduce power consumption in digital circuits [19]. However, a mere scaling of operating voltage can lead to output degradation as it can result in increased delays of critical paths. For example, a low voltage operation of Discrete Cosine Transform (DCT) in a video encoder impacts Peak Signal-to-Noise Ratio (PSNR) quality metric due to erroneous output [20]. Without controlling the supply voltage adaptively, the power gains are diminished due to increased sensitivity of the circuits to manufacturing variations and longer critical path delays. Otherwise, choosing a ( $V_{dd}$ , $V_t$ ) combination becomes necessary for error-free computation and power gains become limited accordingly [21].

In addition to voltage scaling-induced errors and manufacturing *Process Variations (PV)*, other types of hardware faults include aging-induced degradations [22] and radiation-created permanent faults. Systems in which some manual intervention remains no longer a feasible option after deployment, the absence of provision of an autonomous fault-handling capability may lead to a catastrophic system failure [23]. Thus, the provision of capability to adapt the hardware is an essential characteristic for self-organizing hardware systems and reconfigurable hardware paradigm [24][25][26] is favorable in such a scenario. A unified scheme of mitigating hardware errors irrespective of their underlying causes is desirable to achieve output at sufficient quality levels. Nevertheless, hardware faults necessitate mitigation to sustain computational correctness.

While low power Digital Signal Processing (DSP) designs focus on reducing redundancy in computations, conventional error mitigation techniques rely on introducing some form of redundancy in computations. Therefore, for low power designs intended for modern or future nano-scale hardware platforms, the design poses a dilemma. Achieving power efficiency as a design objective seeks those algorithms which can be efficiently mapped to fewer computational units. However, such a reduction makes every computational unit more critical and hence more susceptible to errors. This becomes a significant concern when the intended algorithm is mapped to unreliable hardware fabrics. At the other end of the spectrum, to achieve robustness as a design objective, architectures are sought which exploit or even introduce redundancy in the design. As this type of approach brings in new alternatives to distribute the reliance to multiple hardware units, overall fault-tolerance is enhanced. However, it can realize power hungry designs as the redundancy to mask errors becomes a significant overhead. To combat these challenges in a unified manner, we propose a design framework which introduces the concept of dynamic modular redundancy utilizing computational priorities. We utilize a reconfigurable approach to avoid redundancy during normal operation of the Circuit Under Test (CUT) and dynamically introduce it at run-time to mitigate fault scenarios.

### Characteristics of Fault-Tolerant Systems

Fault tolerant systems are characterized by the reliability and dependability they provide in mission critical systems. The fault detection capability, or *detectability*, is an important attribute of the fault tolerant systems by which faults or a system failure can be detected [27]. An indication is required in situation of faults when the output of the system deviates from its desired operation. While the detectability can be implemented by observing the behavior of a system through certain variables, another way is to replicate the system to realize a duplex configuration. A disagreement in output of the two instances indicates the faulty nature of operation as an error in at least one of the two instances.

A survivable system is defined as one that, when enabled by likely regeneration strategy, can operate without substantial depreciation throughout its expected lifetime even when subjected to multiple internal or external fault-invoking conditions. Specifically within the domain of DSP, a device is said to be survivable if it is capable of handling imminent failures throughout its lifetime by taking the actions necessary to maintaining desired signal processing performance above some minimum threshold. The threat of diminished component reliability becomes more unpredictable due to escalating thermal profiles, process-level variability, and harsh DSP environments such as deep-space and high-altitude flight. Furthermore, increasing density and complexity renders preventing or eliminating all possible design faults to be increasingly infeasible. All these factors pose renewed challenges to designing signal processing circuits resistant to unpredictable damage or malfunction.

Two conventional approaches to handle permanent faults in FPGAs are through Triple Modular

Redundancy (TMR) via tools such as Xilinx XTMR, or progressive resolution via distinct *detection, diagnosis, isolation,* and *recovery* processes. Typically, recovery relies upon reconfiguring the impaired functional block in a different fault-free portion of the fabric. Partial Reconfiguration (PR) capability is beneficial in achieving runtime adaptability with reduced time and space overhead. Compared to resource-oriented Built-in Self Test (BIST) based schemes [28], *functional testing* techniques offer model-free fault-diagnosis [18]. Moreover, autonomous survivability is desired to continue operation without halting service. Ideally, an online fault handling scheme would not interrupt the continuous throughput of the system while only temporarily degrading the spatial/temporal resolution, or PSNR quality. Nonetheless, minimal impact on PSNR is desirable and rapid fault recovery becomes an important design objective.

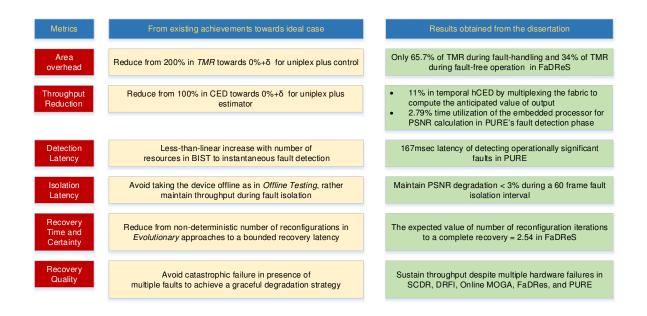

Dynamic redundancy techniques have been widely used to increase reliability of critical systems in which reconfiguration is employed at runtime to utilize spare units in response to failures [29] [30] [31]. While some techniques rely on pre-allocation of dedicated spare units, a dynamic spare pool sharing approach can be favorable in terms of extending fault-capacity [8]. Redundancy enables fault-tolerance, however, how wisely redundancy is employed at runtime determines the sustainability of the system exposed to cumulative failures. Fig. 1.1 illustrates these characteristics of an ideal autonomous recovery technique and the techniques developed in this dissertation in the context of exiting approaches towards achieving these goals. A favorable faulttolerance technique minimally impacts the throughput datapath. In addition, the area-overhead of a fault-handling controller,  $\delta$  should be very low as compared to the baseline area where  $\delta$  is fixed, independent of the datapath complexity, and a fraction of the size of the datapath.

Biological systems have inherent self-repairing capabilities which have inspired signal processing research to mimic these natural adaptive processes in silicon-based systems. Thus, research interest has been increasing toward electronic systems which can sustain considerable damage, yet still remain operational or at least partially operational. Consequently, self-repair and self-healing

mechanisms have been proposed for digital hardware by various researchers [32][33][34]. These mechanisms rely on identifying or employing some form of redundancy, reconfiguration, or both. To realize these properties in a signal processing system, it is useful to identify how a layered model emphasizing the impact of signal processing tasks on output correctness and the runtime reconfiguration of FPGA resources based on Evolvable Hardware can be leveraged.

| Metrics                           | From existing achievements towards ideal case                                                                            |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Area<br>overhead                  | Reduce from 200% in <i>TMR</i> towards 0%+δ for uniplex plus control                                                     |

| Detection<br>Latency              | Reduce from less-than-linear increase with number of resources via BIST, toward instantaneous fault detection            |

| Isolation<br>Latency              | Avoid taking the device offline as in <i>Offline Testing</i> , rather maintain throughput during fault isolation         |

| Recovery<br>Time and<br>Certainty | Reduce from non-deterministic number of reconfigurations in <i>Evolutionary</i> approaches to a bounded recovery latency |

| Recovery<br>Quality               | Avoid catastrophic failure in presence of multiple faults to achieve a graceful degradation strategy                     |

Figure 1.1: Characteristics of an ideal autonomous recovery technique

Evolvable Hardware has been proposed in literature as a reconfiguration-based approach to achieve fault tolerance in electronic designs. These methods extend static fault tolerance techniques at design-time which attempt to make designs which are more robust to faults [35][36]. In particular, runtime evolvable hardware techniques reconfigure hardware resources at runtime to refurbish the circuit [18]. Previous works establish the successful use of Evolutionary Algorithms for adaptive self-recovery of hardware systems based on reconfigurable logic platforms, especially in FPGA-

based systems [18][37][38]. A survey of techniques ranging from passive to dynamic in classification are presented in [39] to tackle hard faults in SRAM-based FPGAs for small circuit case studies. For example, modular redundancy is exploited in [40] for achieving fault recovery of a 4-bit x 4-bit multiplier. Moreover, novel techniques are sought which are scalable to large modular signal processing systems.

Researchers have devised runtime evolutionary techniques to realize fault-resilient electronics through iterative selection [41][42][43]. The fault-detection technique in [43] employs redundant cells in the reconfigurable fabric to check the operating resources by detection discrepancies among replicated outputs. Although, previous attempts have been made to combine architecture and algorithm level knowledge [44][45], there remains a need to develop frameworks utilizing cross-layer information in a way that leverages the soft-resilience present in signal processing applications.

#### Soft Resilience of Signal Processing Systems

In the domain of DSP, a system is said to be *resilient* if it is capable of handling failures throughout its lifetime to maintain the desired signal processing performance within some tolerance. The threat of diminished component reliability becomes more critical to maintaining these tolerances due to process-level variability, as well as escalating thermal profiles which can accelerate aging effects [46] [47]. Additionally, harsh DSP environments such as deep-space and high-altitude flight can further exacerbate lifetime reliability concerns. Meanwhile, increasing device density and system complexity can make the use of design margins and timing guard-banding techniques more difficult [48]. All these factors pose renewed challenges to designing signal processing systems resistant to process variation and aging-induced malfunction.

Dynamic redundancy techniques based on reconfiguration have been widely used to increase re-

liability [30][31]. While traditional fault-handling techniques rely on pre-allocation of dedicated spare units, more recent approaches based on dynamic spare pool sharing can be favorable in terms of reducing area overhead[46] [49]. Resiliency is achieved when a regeneration strategy allows a system to operate without substantial depreciation throughout its lifetime, even when subjected to multiple internal or external fault-invoking conditions. Redundancy enables fault-tolerance, how-ever, how wisely redundancy is employed at runtime determines the sustainability of the system after exposure to cumulative failures. Adaptive reconfiguration can reduce the size of a sustainable spare pool, and it also enables the novel resiliency strategies developed herein.

FPGAs offer two important features towards resilient signal processing architectures. First, FP-GAs have been used to achieve significant acceleration of DSP applications over conventional computing platforms [50][51]. Second, FPGAs provide hardware support for adaptive reconfiguration. From a reliability perspective, the regular structure of an FPGA-fabric is amenable to reconfiguration-based recovery. A high regularity of FPGA logic resources allows movement of a computational function implemented over a defective region to a fault-free region [15][52]. This characteristic has already made FPGAs popular for application in the space exploration community[10][16][53]. On the other hand, SRAM-based FPGAs are also susceptible to soft (transient) errors as well as hard (permanent) faults [54] that can be addressed using the techniques developed in this work.

Aggressive scaling of semiconductor technology to cope with today's intensive processing demands leads to seeking new autonomous reliability approaches for logic devices. In particular, the reliability concern of VLSI signal processing systems implemented in a sub-32 nanometer process, caused by soft and hard errors, is increasing. Therefore, the importance of providing resiliency is increasing in order to achieve a high level of integration, throughput performance and quality, and the classical trends of transistor density per chip.

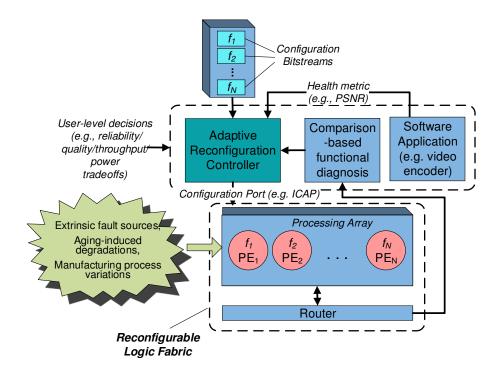

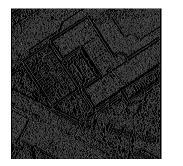

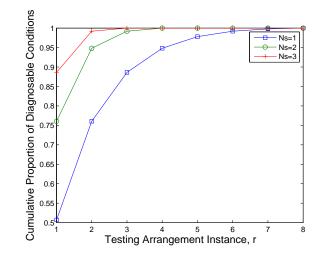

Figure 1.2: System block diagram illustrating the scope of reconfiguration techniques

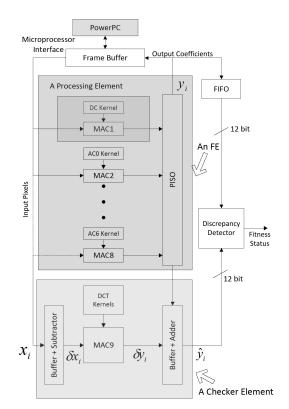

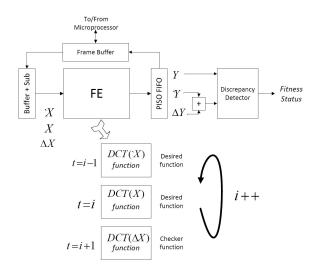

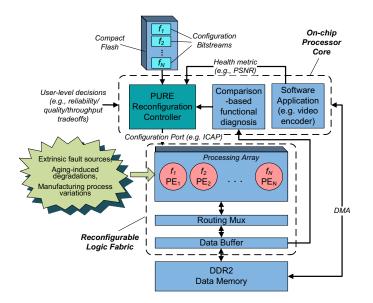

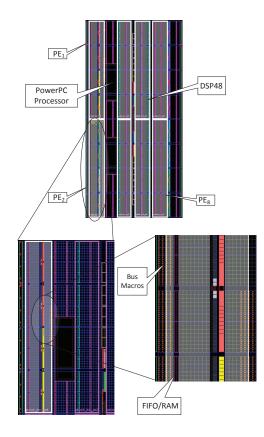

In this dissertation, a strategy is presented for autonomously mitigating permanent faults in order to improve system availability and mission lifetime. The scheme is advantageous in terms of continuous operation, power consumption, and area-overhead while improving reliability. We consider a Functional Element (FE) which has been decomposed into various Processing Elements (PEs) for throughput enhancement. Such a distributed implementation is also beneficial in terms of fault-tolerance. Some of the PEs can be used at runtime to perform diagnosis while others can be configured as operational resources to compensate for failures and maintain performance requirements. Without loss of generality, we term each of these PEs as Reconfigurable Slack (RS). Each RS region denotes a contiguous 2-dimensional reconfigurable region of FPGA logic resources used to diagnose the active PEs. An RS has size and shape which is identical to an active PE in throughput datapath, yet is not currently configured to contribute to the throughput. Multiple RS's are not required for the techniques herein, but are shown to decrease the fault diagnosis latency. A system level block diagram to illustrate the framework used in this work for evaluating the techniques developed herein is given in Fig. 1.2. The reconfiguration management of logic resources for fault-handling purposes is performed by reconfiguration controller. The configuration bitstreams are stored in an external memory module. Results from comparison-based diagnosis are monitored at software level. These reconfiguration bitstreams represent alternate configurations to recover from faults. They are loaded from the storage memory as needed dynamically, under control of autonomous algorithms executing on the reconfiguration controller. Thus, from a high-level viewpoint, the objective of this dissertation is to develop algorithms for the reconfiguration controller that best address the fault-handling characteristics identified in Figure 1.1

# **Quality-Oriented Architectural Adaptations**

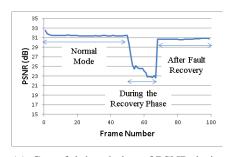

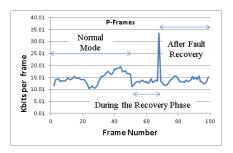

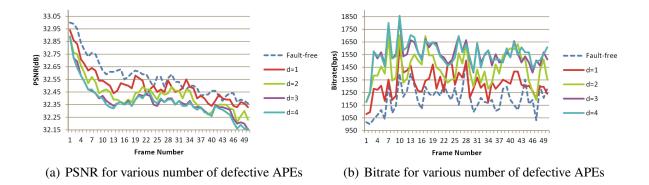

To deal with susceptibility to aging and process variation in the deep submicron era, signal processing systems are sought to maintain quality and throughput requirements despite the vulnerabilities of the underlying computational devices. The Priority Using Resource Escalation (PURE) online resiliency approach is developed herein to maintain throughput quality based on the output PSNR or other health metric. PURE is evaluated using an H.263 video encoder and shown to maintain signal processing throughput despite hardware faults. Its performance is compared to two alternative reconfiguration algorithms which prioritize the optimization of the number of reconfiguration occurrences and the fault detection latency, respectively. For a typical benchmark video sequence, PURE is shown to maintain a PSNR baseline near 32dB. Compared to the alternatives, PURE maintains a PSNR within a difference of 4.02dB to 6.67dB from the fault-free baseline by escalating healthy resources to higher-priority signal processing functions. The diagnosability, reconfiguration latency, and resource overhead of each approach is analyzed. The results indicate the benefits of priority-aware resiliency over conventional redundancy in terms of fault-recovery, power consumption, and resource-area requirements.

Voltage scaling has been an effective approach to reduce the power consumption in DSP systems due to the quadratic dependence of power on operating voltage. However, variations in the fabrication process can manifest soft errors in devices built with deep submicron technology [47][55]. The reliability issues of modern signal processing architectures due to voltage scaling are being addressed in recent research [56][57]. Many of these works take various approaches to leverage the role of priority in the signal processing computation to improve resiliency, along with its area and energy costs. For example, the general concept of asymmetric reliability is developed in [46] to prioritize the protection of higher order bits in error resilient architectures supporting probabilistic applications. Algorithmic level properties are utilized to realize area efficient replicas of motion estimation blocks to achieve reliable operation under energy efficiency constraint in [58]. Likewise, to minimize the power overhead of error resilience while maintaining signal quality, the scheme proposed in [47] exposes only less crucial blocks to process variation and channel noise.

In this dissertation, the developed techniques exploit health metric based feedback to perform reconfiguration in order to meet resiliency, availability, energy efficiency, and survivability objectives. Various applications are considered as case studies. These health metrics include PSNR of video encoder, bitrate of the compressed bitstream, and measure of confidence from DCT, Motion Estimation (ME), and SVM modules, respectively. In other case studies where a readily available health metric is not feasible, the discrepancy information is used to assess the erroneous behavior of the hardware fabric. Fault-diagnosis algorithms developed herein engage the priority of processing blocks in order to sustain partial throughput during the recovery period. The recovery strategy also considers functional priorities when mitigating hard faults. Furthermore, the tradeoffs of quality and energy efficiency are explored by a multi-objective formulation of the reconfiguration problem.

#### Contributions of the Dissertation

The primary focus of this work is to develop novel and effective techniques for autonomous faulthandling in digital systems. To this end, reconfiguration based diagnosis and recovery techniques are proposed to effectively utilize redundancy needed for fault-tolerance.

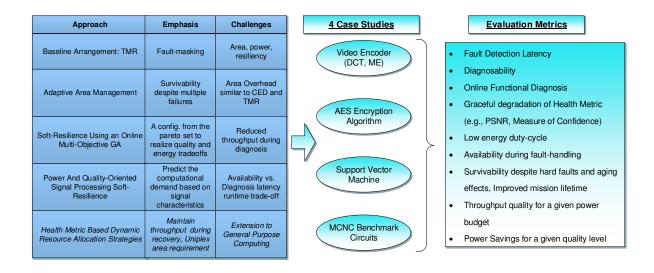

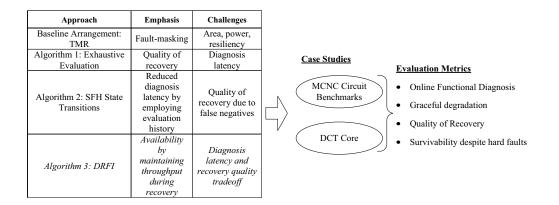

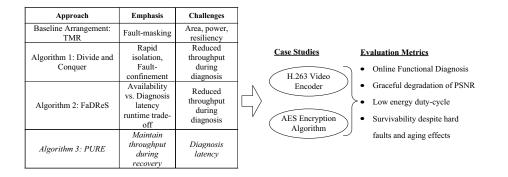

Figure 1.3: A roadmap diagram illustrating the techniques evaluated herein

Fig. 1.3 illustrates the emphasis of various techniques presented in this dissertation and evaluation metrics in the context of some signal processing case-studies. Here, the five novel approaches for autonomous fault-handling developed in this dissertation are listed. The last approach listed is the capstone work in the dissertation using an observable health metric. In the next column, each approach has a technical focus or objective related to the desirable characteristics for autonomous fault handling mentioned earlier ranging from simple fault-masking to sophisticated maintenance of throughput during recovery while incurring negligible area overhead. To achieve these objective, each approach faces technical challenges ranging from reduced throughput during diagnosis to recovery latency. Next, four case studies were selected to evaluate each approach. These case

studies were chosen due to their popularity in signal processing, communication systems, machine learning, and computer architecture. Each case study was then evaluated using one or more metrics as listed on the right side of Figure 1.3. While progress was made on improving many of these, a focus on fault-handling latency and recovery quality proved especially effective as will be shown in Chapter 6. The main contributions of the dissertation are listed in the following, while the chapters following a chapter on the related work describe these techniques in detail.

- Developed area management techniques for the fault handling problem in reconfigurable logic devices with δ area-overhead, less than 5% throughput degradation, and ability to sustain multiple failures in the hardware resources. These are A Self-Configuring TMR Scheme Utilizing Discrepancy Resolution (SCDR), Heterogeneous Concurrent Error Detection (hCED), Amorphous Slack (AS) Fault-Handling Methodology, and Distance-Ranked Fault Identification (DRFI) presented in Chapter 3.

- Formulated the objective of maintaining the quality-of-service and power consumption into a generalizable runtime mapping problem based on the underlying resource performance and operating workload. A multi-objective GA approach is developed for this mapping optimization problem in which a population of solutions is guided by a novel adaptive guidance function as presented in Chapter 4.

- Demonstrated use of PSNR as a health metric to achieve autonomous monitoring of operation for graceful degradation, low-power operation, and survivability in presence of multiple failures. These techniques are *Fault-Handling Motion Estimation (FHME) Engine*, *Fault Demotion Using Reconfigurable Slack (FaDReS)*, and *Priority Using Resource Escalation* (*PURE) Escalation* presented in Chapters 5 and 6, respectively

# **CHAPTER 2: RELATED WORK**

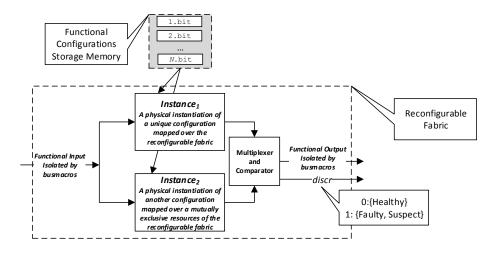

Fault Handling (FH) systems typically employ a sequence of resolution phases including Fault Detection (FD), *Fault-Diagnosis*, and Fault Recovery (FR). A system can be considered to be fault-tolerant if it continues operation in the presence of failures, perhaps in a degraded mode with partially restored functionality [59]. Reliability and availability are desirable qualities of a system, which are measured in terms of service continuity and operational availability in presence of adverse events, respectively [60]. In this work, reliability is attained by employing the reconfigurable modules in the fault-handling flow, whereas availability is maintained by minimum interruption of the main throughput datapath.

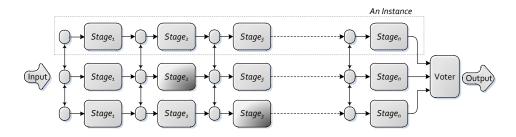

The redundancy based FD methods are popular among fault-tolerant systems community, with costs of area and power overhead. In the *Comparison Diagnosis Model* [61][62], a pair of units is evaluated subjected to the same inputs and a discrepancy indicates failure. For example, a Concurrent Error Detection (CED) arrangement utilizes either two concurrent replicas of a design [18], or a diverse duplex design to reduce common mode faults [30]. Its advantage is a very low fault detection latency. A TMR system [63][64] utilizes three instances of a datapath module. The outputs of these three instances become inputs to a majority voter, which in turn, provides the main output of the system. In this way, besides fault detection capability, the system is able to mask its faults in the output if distinguishable faults occur within one of three modules. However, this incurs an increased area and power requirement to accommodate three replicated datapaths. It will be shown that these overheads can be significantly reduced by either considering the instantaneous PSNR measure obtained within video encoder as a precipitating indication of faults or periodic checking of the logic resources.

The Fault Diagnosis phase consists of distinguishing properly-functioning components from some

larger set of suspect components. Traditionally, in many fault tolerant digital circuits, the components are diagnosed by evaluating their behavior under a set of test inputs. This *test vector strategy* can isolate faults while requiring only a small area overhead, yet incurs the cost of evaluating an extensive number of test vectors to diagnose the functional blocks as they increase exponentially according to the number of inputs. The proposed active dynamic redundancy approach combines the benefits of redundancy with a negligible computational overhead. *Static redundancy* techniques reserve dedicated spare resources for fault-handling. In contrast, in the presented approach, the redundant modules are continually utilized in the datapath during the normal mission operation.

While reconfiguration and redundancy are fundamental components of a FR process, both the choice of reconfiguration scheduling policy and the granularity of recovery affect the *availability* during *recovery phase* and *quality of recovery* after fault-handling. Here, it is possible to exploit the algorithm's properties so that the reconfiguration strategy is constructed taking into account varying priority-levels associated with required functions.

Various methods of achieving fault-tolerance in FPGAs include device level, passive redundancy, resource-oriented testing, functional testing, GA, configuration level, multiple configurations, and scrubbing techniques. The relevant work is described in detail in the following.

#### Static Redundancy

A passive *redundancy* based scheme, TMR is popular in FPGA-based reliable designs for protection against permanent as well as transient faults. As a matter of fact, a vendor's tool *XTMR* is available to triplicate the user logic [63]. The errors can be masked in the output to some extent. A Dual Modular Redundancy (DMR) arrangement is also commonly used for fault detection in situations in which area and power overhead of a TMR is unaffordable. A research of different forms of the CED setup was presented by Mitra et. al [30]. The CED schemes rely on some form of redundancy for fault detection purpose. Sometimes, the functional modules are implemented in the form of a diverse duplex system which involves two alternative implementations of the same design. This helps error detection in case of common mode failures. Besides duplex systems, CED schemes also realize parity based systems [30]. For example, an even/odd parity can be used to ensure the correctness of an output sequence of a digital system.

Temporal redundancy techniques have been explored in fault-tolerant microprocessor systems. A typical error detection scheme involves running a duplicate thread for the comparison purpose on a chip multiprocessor (CMP). Hyman et. al [5] proposed an extension to the scheme by exploiting various redundancies in instructions in multi-core processors framework. Thus, if an instruction is affected by transient errors in the execution path, the duplicate execution would provide a fault detection capability. However, if the faults are of permanent nature, the re-execution of an instruction would have the same result and the error detection becomes impossible. This is because a given input data will exercise the logic resource in the same way no matter how many times an instruction is executed. In the proposed Heterogeneous CED (hCED) approach, we apply the desired function to the input data at one instant, and the redundant computation is performed on the difference data in the second instant. Thus, the logic resource is exercised with different input data in each case. In this way, the approach is able to detect errors in case of permanent faults also, in addition to transient errors.

In the context of previous work, the followings are the key-points of the *h*CED approach: FD in spatial *h*CED mode with resource saving, FD in temporal *h*CED mode with uniplex chip area requirement at the cost of reduced throughput, and the coverage of transients as well as permanent faults in FD using temporal *h*CED.

The Algorithmic Noise Tolerance (ANT) technique [58] offers area efficiency which consolidates

16

an application oriented approach to achieve fault-resilience. In the ANT scheme, a reduced precision replica of CUT is employed which is less energy hungry; then CED is performed to check the CUT for output discrepancy. Alternatively, in [45], fault-handling is demonstrated in uniplex mode of operation using the runtime reconfiguration property of FPGAs. Fault-detection was performed by observing the behavior of the PSNR metric while diagnosis was performed by re-mapping the APEs contained in the DCT core itself with significantly less area overhead as compared to ANT. Varying priorities of DCT coefficients were exploited to recover from faults scenarios.

#### Resource Testing by BIST

*Resource-based Testing* techniques rely on testing the logic resources using some test vectors. The output response of the logic resources is analyzed to identify their health. Online BIST and Roving Self-Testing AReas (STARs) are based on the principle that part of a chip is subjected to test inputs, and the test area is moved around while keeping the system online. The techniques proposed by Emmert et al. [6], Dutt et al. [65], and Gericota et al. [66], are some examples of resource oriented techniques. The heterogeneous nature of FPGA resources (e.g., LUTs, FFs, BRAMS, DSP Blocks) makes it intractable to come up with a generic testing methodology. Moreover, the scalability of resource testing techniques with huge growth of on-chip resources is also a concern. Therefore, functional testing is an appealing alternative to resource testing.

Resource testing techniques for fault isolation of FPGA resources have been proposed in literature in the form of either offline testing or online testing [67]. In an offline BIST method, all the active resources are released from their active functionality and a testing sequence is conducted to verify the correctness of these resources. However, this method is less practical for real-time systems having specific timing deadlines, or mission critical systems in which device outage may be problematic to the mission. On the other hand, *Online Testing* schemes may employ the dynamic reconfiguration capability of FPGA and tests can be performed during runtime. Online BIST techniques [6] check a small area of the chip in concurrence while keeping the remaining non-tested regions in operation. Resource testing typically involves pseudo-exhaustive input-space testing of the physical resources to identify faults, while functional testing methods check the fitness of the datapath functions [65]. In Gericota et. al's approach [66], the active logic resources are concurrently replicated to support a runtime testing procedure. Their active replication technique concurrently creates replicas of Configuration Logic Blocks (CLBs) to improve the reliability. Dutt et. al [65] extended the BIST method to offline as well as online testing modes. In their approach, the output of a Programmable Logic Block (PLB) is compared to that of an identically configured PLB. A discrepancy in the output flags the PLB as faulty. The exhaustive evaluation of all the resources through test vectors may be a long process. Our scheme can be conceptualized as resource testing through actual inputs of the circuit.

BIST techniques are characterized by the fact that fault detection latency may be long depending upon the chip area. Moreover, transient errors are not detectable in these schemes. In our approach, by introducing some redundancy for error checking purpose, the transient errors are also detectable with a negligible fault detection latency. Gao et. al [68] proposed a resource testing scheme using time multiplexing of different components through the reconfiguration capability of FPGA. As the reconfiguration time is a considerable entity in current FPGA technology, the Self-Configuring Discrepancy Resolution (SCDR) technique multiplex the inputs to a fixed hardware fabric instead of reconfiguring the resources with alternating functions.

# System-Level Diagnosis

There is a body of research dealing with the problem of identifying faulty components by employing system diagnosis theory. A pioneer work in diagnosis theory is by Preparata et al. [62] in which the problem of identifying faulty nodes in a digital system is formulated as a connection assignment procedure. Various components of a digital system are represented by nodes in a graph described by a *connection matrix*. A given edge in the graph connects two nodes, one being the node *under test* and the other being *testing* node. The diagnosibility of digital systems containing faulty modules has been studied by various researchers [69][70]. In the proposed scheme, reconfigurable hardware's bitstreams can be conceptualized as nodes of a graph representing a digital system.

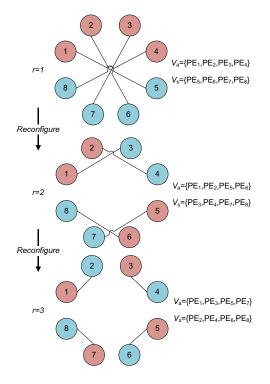

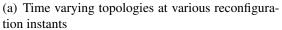

In general, the process of identifying faulty nodes in a system G is called *Fault Diagnosis*. The maximum number of faulty nodes which a scheme guarantees to identify is known as *diagnos-ability* of the system. *System-Level Diagnosis* is a widely used technique for fault resilience in multiprocessor systems. In Comparison Diagnosis Model (CDM) [61] [71], [72], [73], a pair of units is evaluated subjected to the same inputs and a discrepancy indicates some failure. The impact of a topology on diagnosability of a network is thoroughly discussed in [74] [75]. In the proposed adaptive reconfiguration schemes, we will consider a fully connected topology so that the diagnosis can be performed between any pair of nodes. Then, after identifying a faulty node, it can be replaced by any of the available healthy nodes. It will be shown that fault-handling can be performed online by time varying topology of the PEs.

#### **Evolvable Hardware Techniques**

*Evolvable hardware* techniques focus on adapting hardware to achieve fault tolerance. These methods rely on finding a configuration which meets fitness criteria under a given fault scenario. A Competitive Runtime Reconfiguration (CRR) [18] scheme uses evolution to repair the faulty resources of a CED arrangement. We can divide these evolutionary schemes into two types 1) Design-time fault tolerance 2) Runtime fault tolerance. The focus in design time fault tolerance

is to build circuits which are robust to faults in different components, yet the disadvantage is that fault recovery is limited to only anticipated faults. On the other hand, the focus in runtime fault tolerance schemes is to recover during runtime operation. Using the dynamic partial reconfiguration capability and the presented recovery sequence, PURE approach is able to achieve a high degree of runtime fault tolerance.

Keymeulen et al. [36] proposed an *evolutionary* approach to circumvent the faults in reconfigurable digital circuits. They proposed genetic algorithms to evolve the population of fault tolerant circuits by applying genetic operators like mutation and crossover over the circuit representation. Another technique [76] is based upon bitstream manipulation by evolutionary algorithms to recover from faults.

Heng and DeMara [77] developed a *Multilayer Runtime Reconfiguration Architecture* for autonomous fault handling in FPGA. They split the task into logic, translation and reconfiguration layers and manipulate the hardware configurations using on-chip resources for autonomous repair. Lach et al. [78] split the design into tiles and calculate the reliability of each tile instantiated into the design implemented in FPGA. On identifying the tile that uses faulty resources, they assign the allocated spare resources to that element. *Multiple configurations* are generated by [18] for fault handling purpose whereas the configurations are repaired using evolutionary algorithms.

Sharma et al. [79][80] used *group testing* techniques to isolate fault locations in FPGA. Once the resources are isolated, the recovery is made by utilizing alternative logic resources. The method presented in this dissertation does not require explicit fault isolation phase, while the configurations are only generated at design time thereby not necessitating the vendor's synthesis and implementation tool at runtime. Fault handling is accomplished by promoting the hardware configurations which utilize fault-free resources [12]. The proposed Distance-Ranked Fault Identification (DRFI) approach is a system-level fault-diagnosis technique by which healthy configurations are identified

in a configuration pool, while the instantiation of two healthy configurations in a duplex manner completes the fault-recovery process.

#### **Reconfiguration Techniques**

Hardware autonomy is desirable in space systems because manual intervention may be an infeasible option. Steiner et. al [81] proposed an autonomous system in which hardware computational resources are managed at runtime. Their demonstrated system can dynamically parse and synthesize digital circuit netlists, place-and-route on FPGA at a very fine granularity. It relies on a customized implementation tool. Our method operates at a coarse granularity of block-level in the circuit corresponding to pipelined stages of hardware core. The autonomous operation can be realized using dynamic reconfiguration capability, an on-chip microprocessor and the internal access port for reconfiguration. An autonomous operation of hardware is also desirable for other applications involving certain objectives such as power optimization.

FPGAs are widely used in signal processing, image processing and video applications [82] due to their parallel nature. In addition, the reconfiguration capability [83] provides flexibility in exploring different hardware architectures. The dynamic reconfiguration of FPGA resources can be performed in a fault handling scheme to avoid the faulty resources.

Dynamic partial reconfiguration capability of FPGAs has been explored for useful tasks by various researchers [84], [85], [86]. Fault recovery methods of FPGA-based designs usually exploit the reconfigurable nature of the device. After completion of the fault isolation phase, the faulty resources are avoided by reconfiguring the chip so that the design is relocated to a fault-free area. On the other hand, evolutionary techniques such as Genetic Algorithms (GAs) have been employed to generate circuits at design-time which are robust to faults [36]. In the current work, the circuit

is evolved at runtime to reach the desired level of functionality. The GAs being soft computing stochastic search process, the bounds on search time are not achievable; however, related work using GAs demonstrated very acceptable recovery time for circuits with various number of LUTs.

# Comparison of Techniques

| Approach                                          | Area<br>requirement | Basis for<br>Recovery                           | Detection<br>Latency                           | Number of<br>Reconfigs                                                   | Additional<br>Components<br>Required                          | Granularity                     | Guarantee of improvement                     |

|---------------------------------------------------|---------------------|-------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------|----------------------------------------------|

| TMR                                               | 3 fold              | Requires 2<br>datapaths are<br>operational      | Negligible                                     | Not Applica-<br>ble                                                      | 2 of 3 Major-<br>ity Voter                                    | Function or Re-<br>source level | 100% for sin-<br>gle fault, 0%<br>thereafter |

| Evolutionary Hard-<br>ware                        | Not Applica-<br>ble | Redundancy<br>and Com-<br>petitive<br>Selection | Not Ap-<br>plicable                            | Only when<br>fault is<br>present;<br>Non-<br>deterministic               | GA Engine                                                     | Logic Blocks                    | No                                           |

| CRR                                               | Duplex              | Recovery<br>complexity                          | Negligible                                     | Only when<br>fault is<br>present;<br>Varies                              | CRR con-<br>troller                                           | Function level                  | No                                           |

| Online Recovery<br>(Roving STARs,<br>Online BIST) | Roving Area         | Available<br>Spares                             | Significant:<br>linear in<br>number of<br>PLBs | Continuous<br>reconfigura-<br>tion                                       | Test vector<br>genera-<br>tor, Output<br>response<br>analyzer | Logic Blocks                    | Yes                                          |

| PURE (the approach proposed herein)               | Uniplex             | Priority of<br>functionality                    | Negligible                                     | Only when<br>fault is<br>present;<br>Linear in<br>number of<br>functions | Reconfig.<br>Controller                                       | Computational<br>Functions      | Yes                                          |

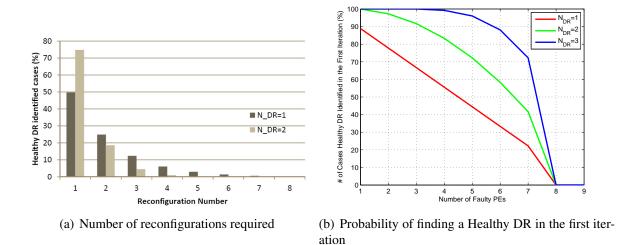

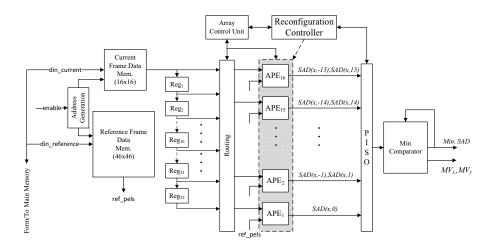

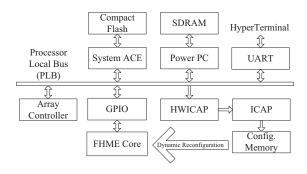

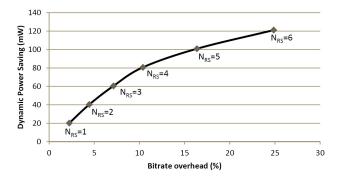

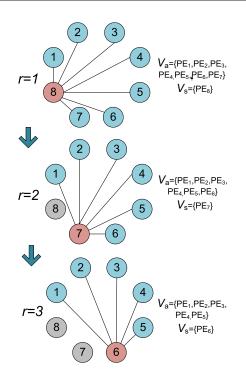

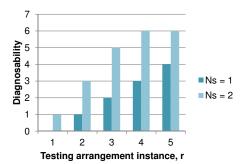

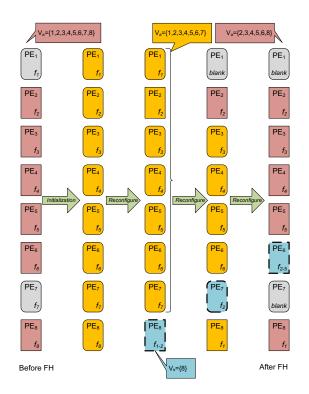

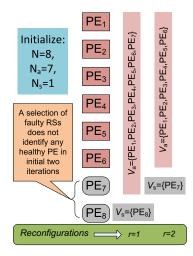

Table 2.1: Comparison of fault-tolerance techniques for SRAM-based FPGAs