# OPTIMIZING DYNAMIC LOGIC REALIZATIONS FOR PARTIAL RECONFIGURATION OF FIELD PROGRAMMABLE GATE ARRAYS

by

MATTHEW G. PARRIS B.S. University of Louisville, 2005

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2009

©2008 Matthew G. Parris

#### **ABSTRACT**

Many digital logic applications can take advantage of the reconfiguration capability of Field Programmable Gate Arrays (FPGAs) to dynamically patch design flaws, recover from faults, or time-multiplex between functions. Partial reconfiguration is the process by which a user modifies one or more modules residing on the FPGA device independently of the others. Partial Reconfiguration reduces the granularity of reconfiguration to be a set of columns or rectangular region of the device. Decreasing the granularity of reconfiguration results in reduced configuration filesizes and, thus, reduced configuration times. When compared to one bitstream of a non-partial reconfiguration implementation, smaller modules resulting in smaller bitstream filesizes allow an FPGA to implement many more hardware configurations with greater speed under similar storage requirements.

To realize the benefits of partial reconfiguration in a wider range of applications, this thesis begins with a survey of FPGA fault-handling methods, which are compared using performance-based metrics. Performance analysis of the Genetic Algorithm (GA) Offline Recovery method is investigated and candidate solutions provided by the GA are partitioned by age to improve its efficiency. Parameters of this aging technique are optimized to increase the occurrence rate of complete repairs. Continuing the discussion of partial reconfiguration, the thesis develops a case-study application that implements one partial reconfiguration module to demonstrate the functionality and benefits of time multiplexing and reveal the improved efficiencies of the latest large-capacity FPGA architectures. The number of active partial reconfiguration modules implemented on a single FPGA device is increased from one to eight to implement a dynamic video-processing architecture for Discrete Cosine Transform and Motion Estimation functions to demonstrate a 55-fold reduction in bit-stream storage requirements thus improving partial reconfiguration capability.

To my wife, Kathryn

#### ACKNOWLEDGMENTS

The author thanks the following for their significant contribution to this work:

Kathryn Parris for her enduring love and patience.

Beckie Lewis, Patrick Breen, Arnold Postell, Pat Simpkins, and Bill Parsons of NASA Kennedy Space Center for supporting this endeavor through the Kennedy Graduate Fellowship Program.

Carthik Sharma, Kening Zhang, Rashad Oreifej, Rawad Al-Haddad, Raul Dookhoo, and Heng Tan for their camaraderie and expertise.

Dr. Lee and Dr. Wu for their encouragement as professors and dedication as Committee Members.

Dr. DeMara for his impressive ability as a mentor in truly caring for his students and inspiring them to greatness.

God for bestowing the gift of intelligence to know Him and benefit humanity.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                          | VIII |

|--------------------------------------------------------------------------|------|

| LIST OF TABLES                                                           | IX   |

| LIST OF ACRONYMS/ABBREVIATIONS                                           | X    |

| CHAPTER 1 INTRODUCTION                                                   | 1    |

| 1.1 Field Programmable Gate Arrays                                       |      |

| 1.2 Space Applications: Radiation-Induced Faults and Handling Techniques | 3    |

| 1.3 Partial Reconfiguration Overview                                     |      |

| 1.4 Benefits of Partial Reconfiguration                                  |      |

| 1.5 Thesis Outline                                                       |      |

| 1.6 Contribution of Thesis                                               | 11   |

| CHAPTER 2 PREVIOUS WORK                                                  | 14   |

| 2.1 Classification of Fault-Handling Techniques                          | 14   |

| 2.2 A-priori Allocation                                                  |      |

| 2.2.1 Spare Configurations                                               |      |

| 2.2.2 Spare Resources                                                    |      |

| 2.3 Dynamic Processes                                                    | 26   |

| 2.3.1 Offline Recovery Methods                                           | 26   |

| 2.3.2 Online Recovery Methods                                            | 30   |

| 2.4 Comparison of Methods                                                | 39   |

| 2.4.1 Overhead-related Metrics                                           |      |

| 2.4.2 Sustainability Metrics                                             | 42   |

| 2.5 Chapter Summary                                                      | 44   |

| CHAPTER 3 EVOLVABLE HARDWARE OPTIMIZATION STRATEGIES                     | 46   |

| 3.1 Genetic Algorithms                                                   | 46   |

| 3.2 Age-Layered Population Structure Overview                            | 47   |

| 3.3 ALPS Implementation                                                  | 49   |

| 3.3.1 Chromosome Representation                                          | 50   |

| 3.3.2 Initialize Population                                              | 51   |

| 3.3.3 Evaluate Fitness                                                   | 52   |

| 3.3.4 Selection                                                          | 53   |

| 3.3.5 Genetic Operators                                                  | 54   |

| 3.3.6 Replacement                                                        | 55   |

| 3.3.7 GA Parameter Summary                                               |      |

| 3.4 Experimental Setup                                                   | 58   |

| 3.5 Experimental Results                                                 |      |

| 3.5.1 ALPS Overview                                                      |      |

| 3.5.2 Standard GA and ALPS Comparison                                    | 62   |

| 3.5.3 Age-Level Management Optimization                                  | 66   |

| 3.6 Chapter Summary                                                      |      |

| CHAPTER 4 PARTIAL RECONFIGURATION AND FPGA ARCHITECTURE ANALY            |      |

| 4.1 Introduction                                                         |      |

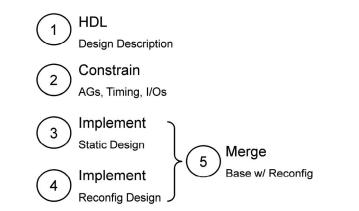

| 4.2 Early Access Partial Reconfiguration Design Flow                     |      |

| Step 1: Hardware Description Language (HDL) Design and Synthesis         | 73   |

| Step 2: Set Design Constraints                          | 74  |

|---------------------------------------------------------|-----|

| Step 3: Static Module Implementation                    |     |

| Step 4: Reconfigurable Module Implementation            | 76  |

| Step 5: Merge Implementations                           | 76  |

| 4.3 Application Using Partial Reconfiguration           |     |

| 4.3.1 Case-study Application                            |     |

| 4.3.2 Overview of Design using Partial Reconfiguration  |     |

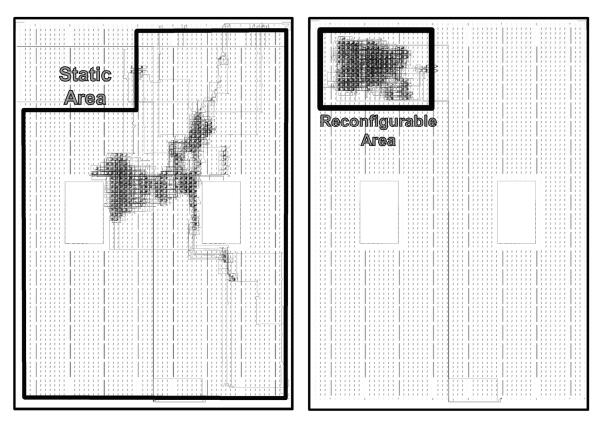

| 4.3.3 FPGA Implementation                               | 81  |

| 4.4 Virtex Family Comparison                            |     |

| Bitstream Size Comparison                               |     |

| 4.5 Chapter Summary                                     |     |

| CHAPTER 5 DYNAMIC PROCESSOR ALLOCATION STRATEGIES       |     |

| 5.1 Video Compression Overview                          | 86  |

| 5.2 Scalable Architecture for DCT and Motion Estimation |     |

| 5.3 Scalable Architecture Implementation                | 89  |

| 5.4 Scalable Architecture Hardware Arrangements         |     |

| 5.5 Chapter Summary                                     |     |

| CHAPTER 6 CONCLUSION                                    |     |

| APPENDIX: FIGURE 1-1—PERMISSION TO REPRINT              | 102 |

| LIST OF REFERENCES                                      | 104 |

# LIST OF FIGURES

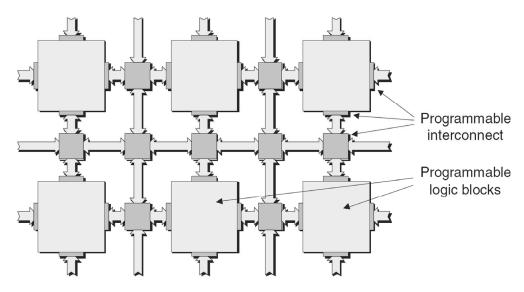

| Figure 1-1: Top-down View of a Simple, Generic FPGA Architecture [Maxfield 2004]      | 2  |

|---------------------------------------------------------------------------------------|----|

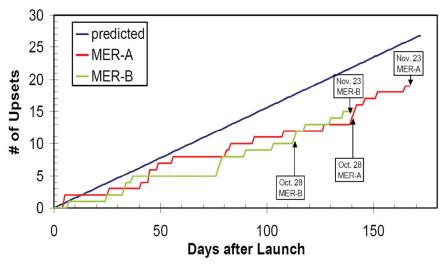

| Figure 1-2: SEU Occurrences in Xilinx XQR4062XL FPGAs in the MER LPSIF [Swift 2006]   |    |

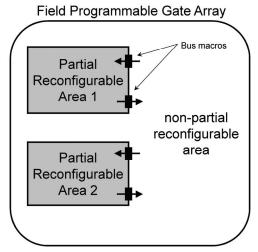

| Figure 1-3: Module-based Design Layout with Two Reconfigurable Modules                | 7  |

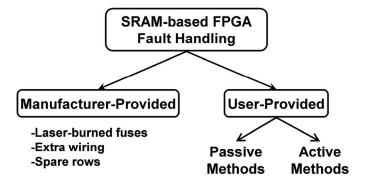

| Figure 2-1: Classification of FPGA Fault-Handling Methods                             | 14 |

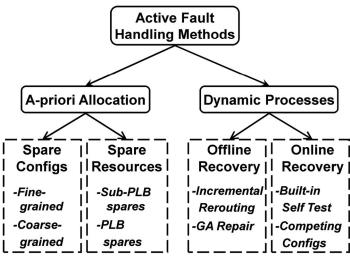

| Figure 2-2: Classification of Active Fault-Handling Methods                           | 16 |

| Figure 2-3: Alternate Fine-grained Configurations for a Faulty 3x3 Partition          | 18 |

| Figure 2-4: Triple Modular Redundancy with Standby Configurations [Zhang et al. 2006] | 19 |

| Figure 2-5: Coarse-grained Partitioning Schemes for an FPGA                           | 21 |

| Figure 2-6: PLB Repair Strategies using Sub-PLB spares                                |    |

| Figure 2-7: Fault scenarios with spare PLBs [Hanchek and Dutt 1998]                   | 25 |

| Figure 2-8: One Possible Minimax Fault-Handling Strategy for a 5x5 array              |    |

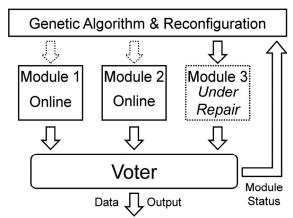

| Figure 2-9: Single-Module Repair in TMR Arrangement                                   | 31 |

| Figure 2-10: Roving STARs within an FPGA                                              |    |

| Figure 2-11: 4x2 Array Configured for a PLB BIST                                      |    |

| Figure 2-12: States of an Individual during its Lifetime [DeMara and Zhang 2005]      | 37 |

| Figure 2-13: Procedural Flow for Competing Configurations [DeMara and Zhang 2005]     | 37 |

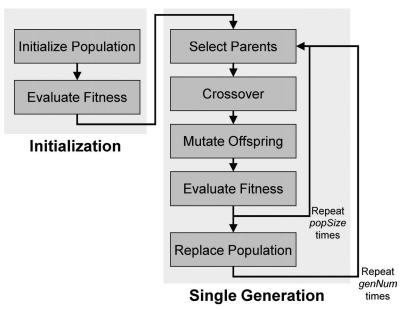

| Figure 3-1: Standard Genetic Algorithm and ALPS Process Flow                          |    |

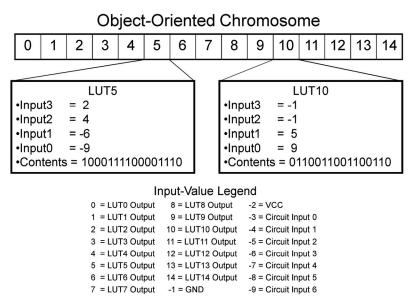

| Figure 3-2: Detailed View of the GA Chromosome                                        |    |

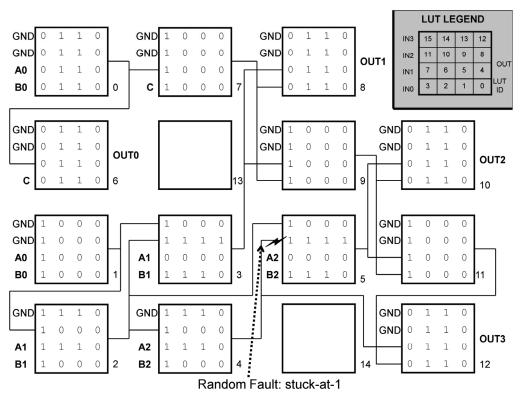

| Figure 3-3: 3-bit Full Adder Implementation (+ wire junctions are not connected)      |    |

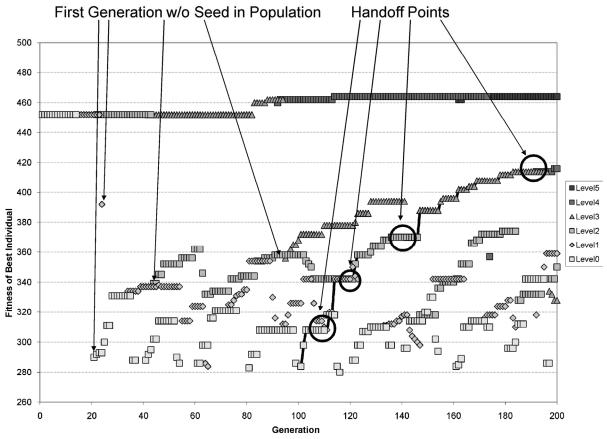

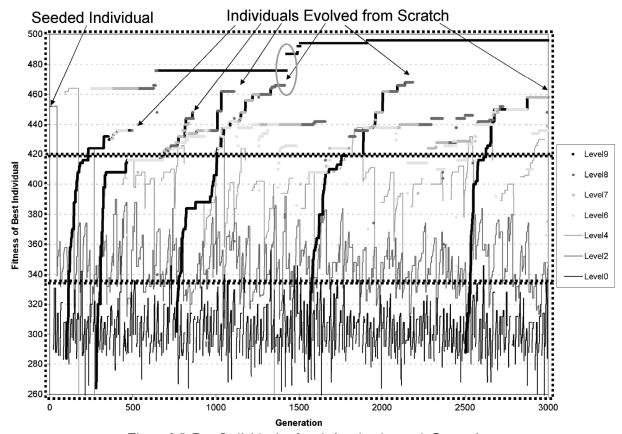

| Figure 3-4: Best Individuals of each Age-level during the Initial Generations         |    |

| Figure 3-5: Best Individuals of each Age-level at each Generation                     | 62 |

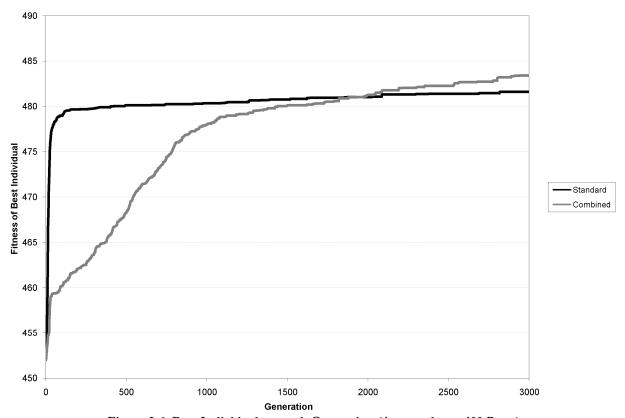

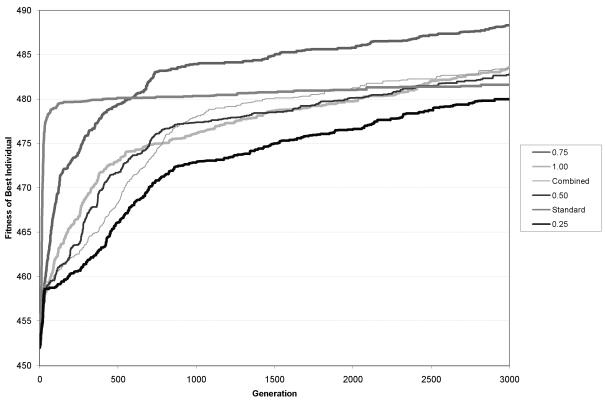

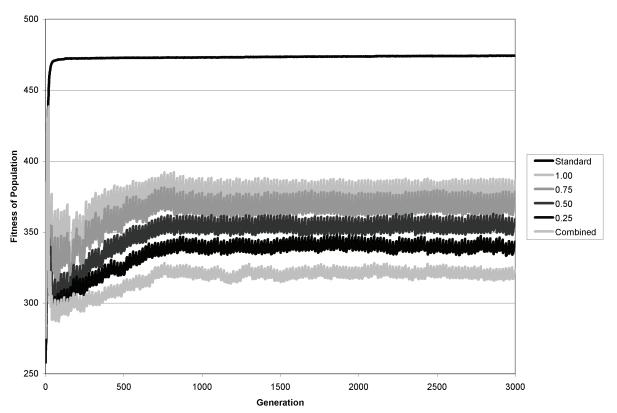

| Figure 3-6: Best Individuals at each Generation (Averaged over 100 Runs)              |    |

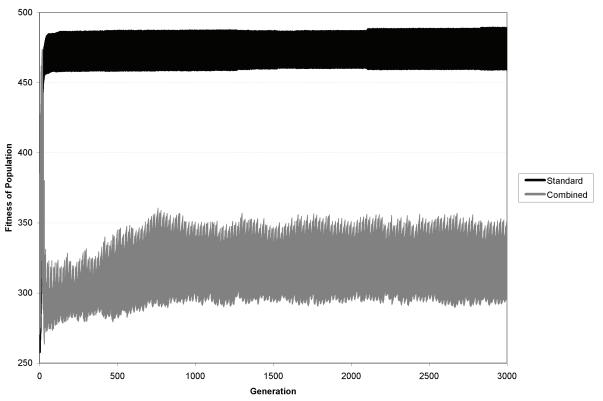

| Figure 3-7: Fitness of Population at each Generation (Averaged over 100 Runs)         | 64 |

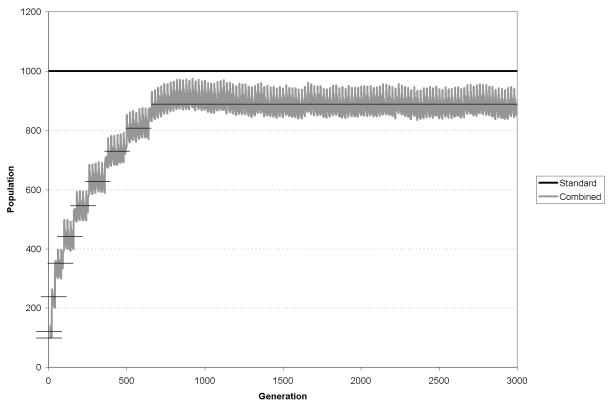

| Figure 3-8: Size of Population at each Generation (Averaged over 100 Runs)            | 65 |

| Figure 3-9: Best Individuals at each Generation (Averaged over 100 Runs)              |    |

| Figure 3-10: Fitness of Population at each Generation (Averaged over 100 Runs)        | 68 |

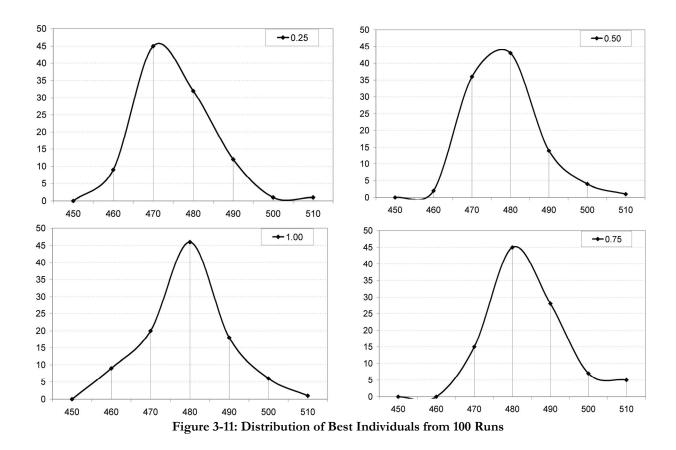

| Figure 3-11: Distribution of Best Individuals from 100 Runs                           | 69 |

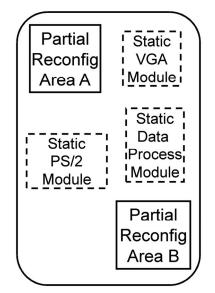

| Figure 4-1: Various Modules in an FPGA                                                |    |

| Figure 4-2: Early Access Partial Reconfiguration Flow [Xilinx 2006]                   |    |

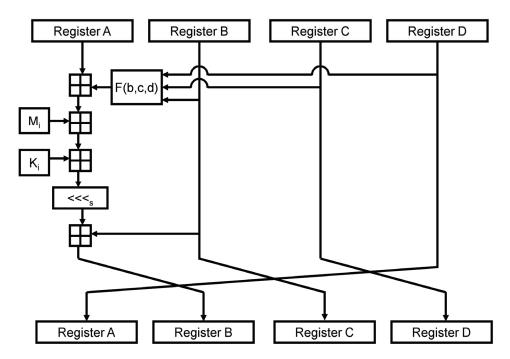

| Figure 4-3: MD5 Hash Algorithm Overview [Wikipedia Current]                           | 77 |

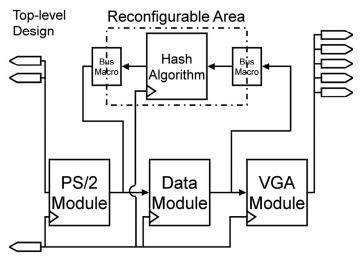

| Figure 4-4: Top-level View of Partial Reconfiguration Design                          | 79 |

| Figure 4-5: FPGA Implementation and Resource Utilization                              | 81 |

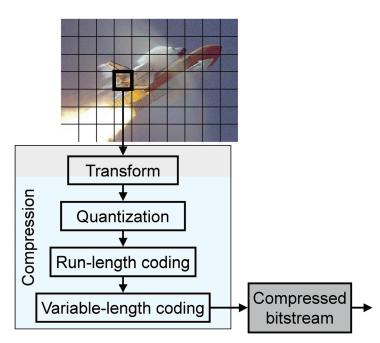

| Figure 5-1: Generic Image Compression Method                                          | 87 |

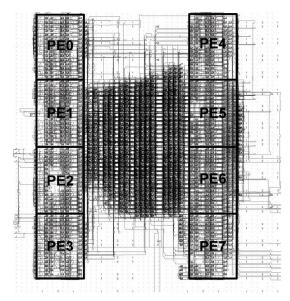

| Figure 5-2: Location of 8 PEs on a V4SX35 device [Huang et al. 2008]                  | 90 |

# LIST OF TABLES

| Table 2-I: Fault-Handling Characteristics and Considerations                  | 17 |

|-------------------------------------------------------------------------------|----|

| Table 2-II: Summary of Overhead-related Metrics                               | 42 |

| Table 2-III: Summary of Sustainability Metrics                                | 44 |

| Table 3-I: Summary of GA Parameters                                           | 57 |

| Table 4-I: Virtex-II Pro Bitstream and Area Sizes                             | 83 |

| Table 4-II: Virtex-4 Bitstream and Area Sizes                                 | 84 |

| Table 5-I: Full Precision PE Implementation Results                           | 91 |

| Table 5-II: Size and Configuration Times of Bitstreams [Huang et al. 2008]    |    |

| Table 5-III: Partial Reconfiguration Hardware Arrangements for 8 PE Locations |    |

|                                                                               |    |

## LIST OF ACRONYMS/ABBREVIATIONS

AFTB Atomic Fault Tolerant Block

AG Area Group

ALPS Age-Layered Population Structure

ASIC Application Specific Integrated Circuit

BIST Built-in Self Test

BLE Basic Logic Element

BUT Block Under Test

CED Concurrent Error Detection

CGT Combinatorial Group Testing

CLB Configurable Logic Block

CPLD Complex Programmable Logic Device

CRR Competitive Runtime Reconfiguration

DCT Discrete Cosine Transform

DSP Digital Signal Processor

EAPR Early Access Partial Reconfiguration

EPROM Erasable Programmable Read-Only Memory

FABRIC Fault-Bypassing Roving Configuration

FIFO First In, First Out

FPGA Field Programmable Gate Array

GA Genetic Algorithm

GND Electrical Ground

HDL Hardware Description Language

IOB Input Output Buffer

JPEG Joint Photographic Experts Group

I/O Input/Output

LOC Location

LPSIF Lander Pyro Switching Interface

LUT Look-up Table

MD5 Message-Digest Algorithm 5

ME Motion Estimation

MER Mars Exploration Rover

MGM Minimax Grid Matching

MUX Multiplexer

NASA National Aeronautics and Space Administration

NCD Native Circuit Description

ORA Output Response Analyzer

OTP One-time Programmable

PAR Place and Route

PE Processing Element

PLB Programmable Logic Block

PS/2 Personal System/2

RAM Random Access Memory

TBUF Tri-state Buffer

SEL Single Event Latchup

SEU Single Event Upset

SHA-1 Secure Hash Algorithm 1

SRAM Synchronous Random Access Memory

STAR Self-Testing Area

TMR Triple Modular Redundancy

TMRSB TMR with Standby

TPG Test-Pattern Generator

TREC Test and Reconfiguration Controller

VCC Electrical Positive Supply Voltage

VGA Video Graphics Array

WUT Wires Under Test

## CHAPTER 1 INTRODUCTION

### 1.1 Field Programmable Gate Arrays

After the advent of the transistor, Application Specific Integrated Circuits (ASIC) emerged to combine different types and numbers of transistors, allowing engineers to create complex digital designs on a single silicon substrate. To avoid expensive non-recurring engineering costs associated with custom ASIC designs, engineers could forgo the unrestrained flexibility of ASICs for quick programmability of simple, fabricated devices called Complex Programmable Logic Devices (CPLD). As a solution between these two extremes, Field Programmable Gate Arrays (FPGA) appeared in the 1980's to combine the complexity of ASICs with the programmability of CPLDs. Since their inception, FPGAs have enabled designers to develop complex systems quickly, decreasing the time-to-market and providing the public with the latest technologies more rapidly.

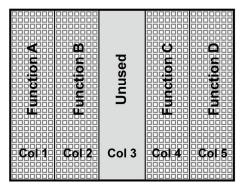

The hardware architecture of FPGAs originates from concepts found within CPLDs. As seen in Figure 1-1, an array of Programmable Logic Blocks (PLB) and programmable interconnect composes the architecture. PLBs contain logic and register resources to implement both sequential and combinatorial circuits whereas programmable interconnect combines PLBs across the FPGA to realize complex circuit designs. PLBs may implement logic functions with multiplexers (MUX) or Look-Up Tables (LUT). LUTs may have three or four inputs connected to an 8x1 or 16x1 table that utilizes the inputs as an address to select the logic stored at the appropriate location.

In addition to being LUT-based and MUX-based, FPGAs may be configured through antifuses [Actel 2005] or Static Random Access Memory (SRAM) cells [Altera 2008]. Anti-fuse FPGAs are One-Time Programmable (OTP) and, as such, configure logic and interconnect by sending a high programming current to form links between routing and voltage levels. The logic and inter-

Figure 1-1: Top-down View of a Simple, Generic FPGA Architecture [Maxfield 2004]

connect configuration of an SRAM FPGA is stored by SRAM cells, allowing unlimited configurability. Whereas anti-fuse FPGAs provide more protection against design theft and some inherent protection from space-borne radiation, SRAM FPGAs allow end-users to change the configuration of a design multiple times. This flexibility allows designers to test prototype designs on the FPGA prior to production. In addition, users are able to update the configuration of a design during the operation life of the FPGA and even designate certain areas of the FPGA to house various modules depending on the needs of the system.

FPGAs have found use among various applications including data processing, networks, automotive, and industrial. The reconfigurability of FPGAs decreases the time-to-market of these hardware applications that would otherwise require its functionality to be hard-wired by a manufacturer. Additionally, the ability to reconfigure its functionality in the field mitigates unforeseen design errors. Both of these characteristics make FPGAs an ideal target for spacecraft applications such as

ground support equipment, Reusable Launch Vehicles, sensor networks, planetary rovers, and deep space probes [Katz and Some 2003; Kizhner et al. 2007; Ratter 2004; Wells and Loo 2001].

## 1.2 Space Applications: Radiation-Induced Faults and Handling Techniques

In-flight devices encounter harsh environments of mechanical/acoustical stress during launch and high ionizing radiation and thermal stress while outside Earth's atmosphere. FPGAs must operate reliably for long mission durations with limited or no capabilities for diagnosis/replacement and little onboard capacity for spares. Mission sustainability realized by autonomous repair of these reconfigurable devices is of particular interest to both in-flight applications and ground support equipment for National Aeronautics and Space Administration (NASA) space missions [Yui et al. 2003].

When in the space environment, FPGAs are subject to cosmic rays and high-energy protons, which can cause malfunctions to occur in systems located on FPGAs. These malfunctions may be a result of *Single-Event Upsets* (SEU) or *Single-Event Latch-ups* (SEL) [Wirthlin et al. 2003]. SEUs are transient in nature, inverting bits stored in memory cells or registers, whereas SELs are permanent by inducing high operating current into logic or routing resources. Whereas all FPGAs containing memory cells or registers are vulnerable to SEUs, anti-fuse FPGAs are particularly resilient since they do not depend upon SRAM cells to store its configuration.

Reconfigurable SRAM FPGAs, on the other hand, store its configuration in SRAM cells, which increases the risk to SEUs. Additionally, decreasing operating voltages and transistor gate widths further increases the risk to SEUs. Before the availability of radiation-hardened SRAM FPGAs, designers of satellites and rovers had no serious alternative to the OTP anti-fuse FPGA. If

the inherent fault tolerant capability of anti-fuse FPGAs was not sufficient, designers were restricted to employing *Passive Fault-Handling Methods* such as Triple Modular Redundancy (TMR). Due to the reconfigurable nature of SRAM FPGAs, radiation-hardened SRAM FPGAs have enabled designers to consider other fault-handling methods such as the *Active Fault-Handling Methods* described in Sections 2.2 and 2.3.

Fault Avoidance strives to prevent malfunctions from occurring. This approach increases the probability that the system is functioning correctly throughout its operational life, thereby increasing the system's reliability. Implementing Fault Avoidance tactics such as increasing radiation shielding can protect a system from Single Event Effects. If those methods fail, however, Fault-Handling methodologies can respond to or recover lost functionality. Whereas some fault-handling schemes maintain system operation, other fault-handling schemes require removing the system offline to recover from a fault, thereby decreasing the system's availability. This limited decrease in availability, however, can increase overall reliability for extended missions.

Scrubbing is a fault-handling technique commonly used to reprogram affected FPGA configuration memory cells with viable configuration data. Scrubbing depends upon reading back the configuration memory cells and *detecting* faults by comparing them to the original configuration. Upon *isolating* a fault, the FPGA can *recover* the correct bitstream through reconfiguration. The Mars Exploration Rovers (MER) landing system successfully implemented this method to mitigate SEUs occurring within the Lander Pyro Switching Interface (LPSIF) during the 200-day transit to Mars [Ratter 2004]. As seen in Figure 1-2, about 10 errors had occurred halfway through the transit and approximately 25 errors can be predicted for the entire transit. For a critical system such as the landing pyrotechnics, scrubbing ensured mission success.

Figure 1-2: SEU Occurrences in Xilinx XQR4062XL FPGAs in the MER LPSIF [Swift 2006]

Whereas Scrubbing handles SEUs in the configuration memory, additional fault-handling methods are necessary to address both transient faults in non-configuration memory elements, such as flip-flops and the registers they compose, and other permanent faults in the remaining components of the FPGA. Sections 2.2, 2.3, and 2.4 classify such fault-handling methods and describe them in detail.

### 1.3 Partial Reconfiguration Overview

All SRAM FPGAs require a full-device reconfiguration upon power-up. Initialization involves programming the FPGA with a configuration bitstream file, which resets and configures all logic, interconnect, and Input/Output (I/O) resources. After initialization, *partial reconfiguration* is the capability to modify a fraction of the resources by programming the FPGA with a partial bitstream file. As discussed in detail within CHAPTER 4 and CHAPTER 5, a full bitstream may be as large as 1,712,614 bytes whereas a partial bitstream may be 2% of this size at 28,306 bytes. This multiple order-of-magnitude reduction in configuration file size can realize several benefits such as reduced

reconfiguration time, reduced storage requirements, and dynamic allocation of functionality as described in detail below in Section 1.4. For use with a fault-handling method such as scrubbing, an additional advantage of partial reconfiguration includes allowing normal operation of resources not affected by the partial reconfiguration [Carmichael et al. 2000; Yui et al. 2003].

Xilinx provides many FPGA devices that support partial reconfiguration, ranging from the simplest Spartan-3 device to the most complex Virtex-5 device. Due to their popularity and wide range of devices, partial reconfiguration is discussed in the context of the capability provided by Xilinx FPGAs. Xilinx provides two forms of partial reconfiguration: static and active [Kao 2005]. *Static* partial reconfiguration modifies a portion of the FPGA configuration while the entire device remains inactive and non-operational. *Active* partial reconfiguration, on the other hand, occurs while the device is active and operational. In the active case, portions of the FPGA not affected by reconfiguration continue nominal operations during the reconfiguration process. Further discussions of partial reconfiguration deal solely with active partial reconfiguration.

Two methods of generating an FPGA partial bitstream file exist: difference-based and module-based. *Difference-based* partial reconfiguration enables designers to make small modifications to the configuration of logic resources [Xilinx 2007a]. After synthesis, translation, as well as Place and Route (PAR) are complete for a design and a Native Circuit Description (NCD) file is generated, these small logic modifications are made. The Xilinx FPGA\_Editor design utility accesses this NCD file and allows users to modify LUT contents, I/O standards, and block RAM (Random Access Memory) contents. The Xilinx bitstream generation utility, BitGen, 1) generates a new full-device bitstream reflecting the modifications, 2) compares the new bitstream to the original bitstream, and 3) generates a partial bitstream only containing the differences between the two. When the FPGA\_Editor reconfigured using the partial bitstream, only those logic resources modified using the FPGA\_Editor

tool are modified. Depending on the type and number of modifications, the filesize of this partial bitstream is typically orders of magnitude less than the initial full-device bitstream and, consequently, requires a reconfiguration time orders of magnitude less. Difference-based partial reconfiguration is only applicable if the original and new FPGA configurations are available, which may not apply to Evolvable Hardware techniques.

The module-based design flow is a coarse-grained method where specific areas of the FPGA are designated as reconfigurable and can contain one or more modules within an application [Xilinx 2006]. Figure 1-3 shows a top-level view where the reconfigurable areas maintain a constant size and location throughout the life of the application. For each reconfigurable area, the design process forms boundaries into which all logic and interconnect resources of its module must reside. Additionally, *bus macros* define the static input/output ports through which all communication between its module and other modules must take place. The static nature of the reconfigurable area with respect to size and I/Os allows multiple versions of one module to be interchanged dynamically without affecting other portions of the FPGA. More detail on this topic is provided in CHAPTER 4, which

Figure 1-3: Module-based Design Layout with Two Reconfigurable Modules

explains the module-based design flow. It accompanies CHAPTER 5, which describes applications that utilize the module-based approach.

#### 1.4 Benefits of Partial Reconfiguration

Full-device reconfiguration is the process of changing the arrangement of all utilized resources on the FPGA. Due to the unlimited programmability of SRAM FPGAs, the configuration may be modified many times during an extended mission. One immediate benefit of full-device reconfiguration is that unforeseen design errors may be resolved by revising the bitstream to reconfigure the FPGA. Additionally, an FPGA with reconfiguration may time-multiplex between two functions that would otherwise not fit within the allocated number of resources on the FPGA; this would allow the FPGA to be configured with Function A at one time and at another time the FPGA is configured for Function B. With reconfiguration, each function may utilize the total number of resources on the FPGA by loading each function separately, whereas without reconfiguration both functions are loaded together, of which the sum of resources cannot exceed the total number of resources on the FPGA.

Partial Reconfiguration is the process where only a portion of the FPGA is reconfigured. Partial reconfiguration provides all the benefits of full-device reconfiguration with two additional advantages: 1) the unchanged portion of the FPGA is not affected and, in some cases, may continue execution, and 2) a partial bitstream is smaller in filesize than a full bitstream. Since partial reconfiguration does not affect the unchanged portion, applications that require critical components to continue operation may be implemented on the same chip as modules that undergo many modifications.

Since the size of the bitstream is directly proportional to the number of resources being configured, partial reconfiguration utilizes a smaller bitstream than a full bitstream for the FPGA. The

direct benefit is less space needed for storing the necessary configurations for operation. An additional benefit derived from a smaller bitstream is that the reconfiguration time is shorter. This savings in time may be particularly useful for systems that depend upon the configuration time such as repetitive intrinsic evolution processes utilizing Genetic Algorithms (GA).

With FPGAs increasing in size and capability, partial reconfiguration enables designers to realize implementations of multiple modules residing on one FPGA device. Whereas full reconfiguration implementations treat the entire FPGA as one module, partial reconfiguration decreases the module granularity from the size of an FPGA to a size as small as 16 PLBs in height [Lysaght et al. 2006]. Thus, an FPGA containing multiple modules operating simultaneously may be reconfigured to perform Function 2 instead of Function 1 while the remaining tasks continue to operate. As previously discussed, the partial bitstream filesize for Function 2 is smaller than the entire bitstream, thus this change between two functions may occur quicker. Without this finer granularity, a designer must generate and store a full bitstream for each combination of modules within the FPGA, exponentially increasing storage requirements for additional modules.

CHAPTER 4 and CHAPTER 5 demonstrate practical applications that exploit these benefits. For example, with partial reconfiguration a designer only generates one full bitstream with multiple partial bitstreams, each representing one module. For a significantly less amount of storage than what non-partial reconfiguration implementations require, a user may implement significantly more combinations of hardware arrangements, increasing the capability of one FPGA device. As suggested by CHAPTER 5, an increase in capability of smaller FPGAs through time-multiplexed pipelining of functions may be comparable to larger FPGAs not utilizing partial reconfiguration.

#### 1.5 Thesis Outline

Various time and space optimizations, along with architectural approaches to realize dynamic functionality, are discussed throughout the thesis. CHAPTER 2, PREVIOUS WORK, surveys the current research of fault-handling techniques for FPGAs, some of which utilize partial reconfiguration to decrease the size of alternative bitstreams used to tolerate faults. The capabilities of these fault-handling methods develop a descriptive classification ranging from simple Passive techniques to robust Dynamic methods. Fault-handling methods not requiring modification of the FPGA device architecture or user intervention to recover from faults are examined and evaluated against overhead-based and sustainability performance metrics such as additional resource requirements, operational delay, fault tolerance, and fault coverage. This classification alongside these performance metrics forms a standard for useful comparisons of fault-handling methods.

CHAPTER 3, EVOLVABLE HARDWARE OPTIMIZATION STRATEGIES, expands the discussion of Standard GAs in CHAPTER 2 to investigate techniques that improve the ability of a GA to repair FPGAs. To evolve and design higher-performing antennas, previous research partitions the population of a standard GA according to the longevity of individual designs within the population using an Age-layered Population Structure (ALPS). Whereas this application may be viewed a continuous search space, CHAPTER 3 reviews the techniques proposed and applies them to the discontinuous and multimodal search space of FPGA repair. The performance of these optimization techniques is compared to a standard GA used for FPGA repair. Parameters are then optimized to increase further the performance of the ALPS strategy.

CHAPTER 4, PARTIAL RECONFIGURATION AND FPGA ARCHITECTURE ANALYSIS, proposes a case study to refine some of the benefits of partial reconfiguration. The proposed system switches between two hash algorithms, Message Digest Algorithm-5 (MD5) and

Secure Hash Algorithm-1 (SHA-1), demonstrating the ability of partial reconfiguration to time-multiplex between two applications while only requiring the spatial resources of one. In implementing the case study on a Virtex-II Pro FPGA, each step of the module-based design process is described in detail. Then, a comparison is made between Virtex-II Pro and Virtex-4 implementations to demonstrate architectural portability and assess how specific hardware devices affect the results of the software-based partial reconfiguration design flow.

CHAPTER 5, DYNAMIC PROCESSOR ALLOCATION STRATEGIES, introduces a scalable architecture for video compression functions on FPGAs that exploits a wide range of benefits provided by partial reconfiguration. More specifically, the scalable architecture focuses on the Discrete Cosine Transform (DCT) function, which is reviewed briefly in the context of the video compression process. A DCT hardware implementation is optimized to form eight discrete Processing Elements (PE), each of which adds functionality to the DCT process. Through partial reconfiguration, these PEs may be added or removed in order to satisfy dynamic requirements of the user. The architecture is shown to be scalable in both the number of PEs allocated to the DCT function and the precision with which the DCT function is calculated. CHAPTER 6 concludes the work described herein and proposes future work from this research.

#### 1.6 Contribution of Thesis

The contributions of this thesis include the following:

1. Novel Taxonomy: Many different fault tolerance methods proposed by the research community, including those that detect, isolate, and repair faults, are considered to form a descriptive classification. Additionally, performance metrics that enable

- quantitative comparisons of capabilities are applied to the SRAM FPGA faulthandling methods surveyed.

- 2. FPGA Repair Optimization: The Age-layered Population Structure (ALPS) is applied to the FPGA repair domain to prevent convergence of the population of candidate solutions by partitioning the population into sub-populations and injecting random individuals at regular intervals. As a result, ALPS explores more of the repair search space, which decreases the population fitness by 30%, and produces complete repairs with 300% greater frequency than a standard GA. Furthermore, introducing a new selection strategy and optimizing the selection probability increases the complete repair frequency to 500%.

- 3. The technique of utilizing the age of individuals to subside population convergence for evolutionary antenna design are applied to the problem domain of repairing digital circuits located on FPGAs. In doing so, Furthermore, improvements to the aging strategy are introduced and optimized to enhance the performance of ALPS. In repairing a 3-bit adder, the results presented quantify the benefit of aging by producing complete repairs with greater frequency.

- 4. Architectural Analysis: The partial reconfiguration implementation process is completed on two FPGA architectures, Xilinx Virtex-II and Virtex-4, to reveal the benefits of the newer Virtex-4 architecture. Analysis of the partial bitstream filesizes identifies the Virtex-4 to have a smaller granularity configuration frame, which generates bitstreams that more closely represent the resources intended to be reconfigured. Applications reconfiguring small portions of the Virtex-4 FPGA generate bit-

streams smaller in filesize than the Virtex-II, which results in shorter reconfiguration times.

5. Adaptive Architecture Implementation: Partial reconfiguration is shown to make viable a dynamic and scalable video architecture that makes use of the benefits previously discussed in Section 1.4. Without partial reconfiguration, time multiplexing of video processing functions is not possible due to long interruptions of the application from configuration times. Not only does partial reconfiguration allow portions of the FPGA not affected by the reconfiguration to operate without interruption, configuration times are decreased, which reduces the length of interruptions to areas being reconfigured. Additionally, multiple reconfigurable areas within one FPGA are shown to significantly increase the capability of the device while maintaining storage requirements similar to an application with one reconfigurable area.

## CHAPTER 2 PREVIOUS WORK

### 2.1 Classification of Fault-Handling Techniques

As suggested by Cheatham et al. [2006], Figure 2-1 divides fault-handling approaches into two categories based on the provider of the method. *Manufacturer-Provided* fault recovery techniques [Cheatham et al. 2006; Doumar and Ito 2003] address faults at the level of the device, allowing manufacturers to increase the production yield of their FPGAs. These techniques typically require modifications to the current FPGA architectures that end-users cannot perform. Once the manufacturer modifies the architecture for the consumer, the device can tolerate faults from the manufacturing process or faults occurring during the life of the device. Concealing the fault through the underlying fabric of the FPGA is advantageous; users need not know of the occurring hardware faults. Despite making faults transparent to the user, the ability of these methods to tolerate faults is limited in both location and number.

User-Provided methods, however, depend upon the end-user for implementation. These high-

Figure 2-1: Classification of FPGA Fault-Handling Methods

er-level approaches use the configuration bitstream of the FPGA to integrate redundancy within a user's application. By viewing the FPGA as an array of abstract resources, these techniques may select certain resources for implementation, such as those exhibiting fault-free behavior. Whereas manufacturer-provided methods typically attempt to address all faults, user-provided techniques may consider the functionality of the circuit to discern between dormant faults and those manifested in the output. This higher-level approach can determine whether fault recovery should occur immediately or at a more convenient time.

Figure 2-1 further separates user-provided fault-handling methods into two categories based on whether an FPGA's configuration will change at run-time. *Passive Methods* embed processes into the user's application that mask faults from the system output. Techniques, such as TMR, are quick to respond and recover from faults due to the explicit redundancy inherent to the processes. Speed, however, does come at the cost of increased resource usage and power. Even when a system operates without any faults, the overhead for redundancy is continuously present. In addition to this constant overhead, these methods are not able to change the configuration of the FPGA. A fixed configuration limits the reliability of a system throughout its operational life. For example, a passive method may tolerate one fault and not return to its original redundancy level. This reduced reliability increases the chance of a second fault causing a system malfunction.

Active Methods strive to increase reliability and Sustainability by modifying the configuration of the FPGA to adapt to faults. This allows a system to remove accumulated SEUs and avoid permanently faulty resources to reclaim its lost functionality. In addition, active schemes can transform faulty resources into constructive components by incorporating stuck-at faulty behavior into the circuit's functionality. External processors, which cost additional space, typically determine how to recover from the fault. These methods also require additional time either to reconfigure the FPGA

Figure 2-2: Classification of Active Fault-Handling Methods

or to generate the new configuration. Figure 2-2 illustrates two classes—*A-priori Allocation* and *Dynamic Processes*— respectively described in Sections 2.2 and 2.3.

This survey focuses on methods modifying an FPGA's configuration during run-time to address transient and permanent faults. Since SRAM FPGAs can be 1) radiation-tolerant, 2) reconfigured, and 3) partially reconfigured with the remaining portion remaining operational, research has also begun to focus on exploiting these capabilities for use in environments where human intervention is either undesirable or impossible. Table 2-I lists various considerations addressed in Section 2.4.

Table 2-I: Fault-Handling Characteristics and Considerations

| Table 2-1. Fault-Handling Characteristics and Considerations |                    |                                            |

|--------------------------------------------------------------|--------------------|--------------------------------------------|

|                                                              | Metric             | Description                                |

| Overhead                                                     | Logic/Interconnect | additional number of resources required    |

|                                                              | Resources          | due to fault-handling strategy             |

|                                                              | Operational Delay  | reduced rate of computations due to        |

|                                                              |                    | fault-handling strategy                    |

|                                                              | Fault Latency      | amount of time required to begin           |

|                                                              |                    | addressing a detected and isolated fault   |

|                                                              | Unavailability     | amount of time system is offline to        |

|                                                              |                    | completely repair a fault                  |

|                                                              | Recovery Goodput   | percentage of correct outputs provided     |

|                                                              | necovery doodput   | during fault repair                        |

| Sustainability                                               | Fault Occlusion    | ability to bypass and/or exploit defective |

|                                                              |                    | resources                                  |

|                                                              | Repair Granularity | smallest arrangement of components that    |

|                                                              |                    | can be repaired                            |

|                                                              | Fault Tolerance    | maximum number of faults handled           |

|                                                              | Fault Coverage     | handling of permanent, transient, logic,   |

|                                                              |                    | or interconnect faults                     |

|                                                              | Critical           | external fault-handling components         |

|                                                              | Requirements       | required relied upon as fault free         |

#### 2.2 A-priori Allocation

Since a typical FPGA application does not utilize 100% of the resources, the standby-spare size can be reduced from an entire FPGA to unused resources within the FPGA. A-priori Allocation takes advantage of the regularity of the FPGA architecture by assigning spare resources during design-time, independent of fault locations detected during run-time. These techniques may recover from a fault utilizing design-time compiled *spare configurations* or re-mapping and rerouting techniques utilizing *spare resources*. Spare configuration methods must provide sufficient configurations whereas spare resource methods must allocate sufficient resources to facilitate a repair without incurring too much overhead. Sections 2.2.1 and 2.2.2 respectively address these two types of A-priori Allocation.

#### 2.2.1 Spare Configurations

### 2.2.1.1 Fine-grained Partitioning

Lach et al. [1998] implement a fine-grained partitioning technique where *tiles*, groups of logic and interconnect resources, are formed. The goal of the tiling technique is to partition FPGA resources in such a way that at least one spare Programmable Logic Block (PLB) is included within each tile to form *Atomic Fault-Tolerant Blocks* (AFTB). Since each AFTB contains at least one spare PLB, each tile is able to tolerate at least one PLB fault.

Alternate fine-grained configurations generated during design-time and stored in an external memory for run-time provide the ability to tolerate faults. For a significant reduction in storage space, each configuration is implemented as a partial configuration as opposed to a full configuration. The Xilinx Virtex-4 architecture, for example, allows two-dimensional partial configurations with a minimum height of 16 Configurable Logic Blocks (CLB) [Lysaght et al. 2006].

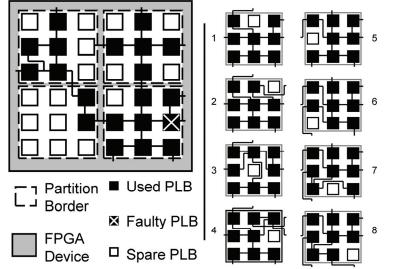

During design-time, tiling implements multiple arrangements of logic resources within an

Figure 2-3: Alternate Fine-grained Configurations for a Faulty 3x3 Partition

AFTB as separate configurations such that each PLB is represented as a spare in at least one configuration. As seen in Figure 2-3, the bottom-right AFTB in the FPGA produces eight alternate configurations. To tolerate a fault during run-time, the system implements the configuration of the faulty AFTB that renders the faulty PLB as spare, effectively bypassing the fault. Figure 2-3 depicts configuration #4 as one such alternate. Fixed inter-AFTB interfaces between alternate configurations render the arrangement of each AFTB logically independent.

#### 2.2.1.2 Medium-grained Partitioning

Since Triple Modular Redundancy (TMR) performs the majority vote of three modules, the voted output remains correct even if a single module is defective. Thus, TMR is a passive fault-handling technique widely used to mitigate permanent and transient faults. Whereas TMR can tolerate one faulty module, a fault occurring in a second module would produce a faulty functional output. As previously discussed, TMR is, thus, is limited in its fault tolerance.

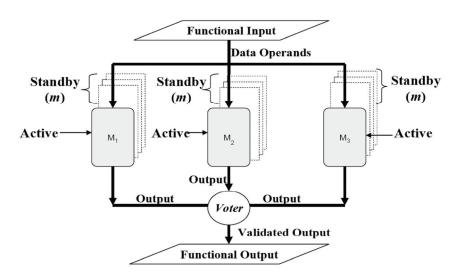

To increase system reliability, Zhang et al. [2006] combine TMR with Standby (TMRSB) to

Figure 2-4: Triple Modular Redundancy with Standby Configurations [Zhang et al. 2006]

create a medium-grained spare configuration method. In TMRSB, each module of the TMR arrangement contains standby configurations that are available at run-time. At design-time, each of these configurations is created to utilize varying FPGA resources. Upon detecting a fault within one of the modules, a standby configuration not utilizing a faulty resource is selected and implemented to bypass the fault. TMRSB exploits the ability of TMR to remain online with two functional modules while the defective module undergoes repair. Repairing modules at run-time increases the reliability of TMR by allowing another fault to occur in a second module while maintaining a correct functional output. The process repeats until all standby configurations are exhausted.

#### 2.2.1.3 Coarse-grained Partitioning

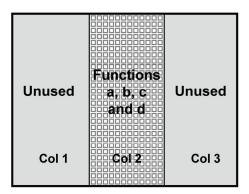

Mitra et al. [2004] present a coarse-grained fault-handling technique that reserves one or more columns of unused PLBs to tolerate faults. At design-time, multiple configurations are generated, each of which locates the spare columns in a distinct areas of the FPGA. Once a fault occurs and is located, the system implements a configuration that covers the fault with its spare columns. If the fault location is not available, then all configurations may be implemented and tested one at a time until a configuration provides a functional application.

Designers may partition the FPGA in one of two ways. If the application is small with respect to the FPGA device, then a *non-overlapping* method can be considered. The non-overlapping scheme separates the FPGA into columns, where one column contains the entire application. The remaining columns are not used by the application and are reserved as spares. As seen in Figure 2-5a, this method generates three distinct configurations, each of which utilizes non-overlapping FPGA resources. More generally, the number of generated configurations is m+1, where m equals the number of tolerable faulty columns.

a) Non-overlapping Scheme

Figure 2-5: Coarse-grained Partitioning Schemes for an FPGA

For larger applications, Figure 2-5b displays a configuration that separates the FPGA application into columns while reserving at least one column as spare. Alternate configurations are generated during design-time so that within each configuration a different column becomes the spare column. In the case of one spare column and four columns containing the application, five distinct configurations are generated. More generally, the number of generated configurations is  $\frac{(k+m)!}{k!m!}$ , where k is the number of columns containing the application. This scheme is *overlapping* since the various configurations generated overlap in utilizing FPGA resources. Unlike the non-overlapping scheme, some configurations, such as Figure 2-5b, may require horizontal routing resources within the spare column to connect the separated logic resources.

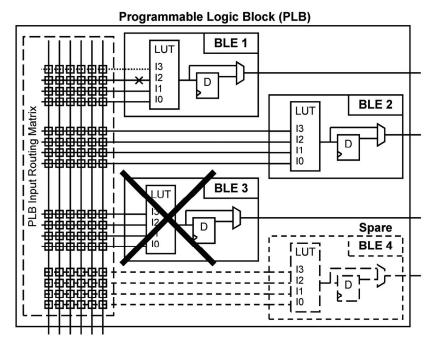

#### 2.2.2 Spare Resources

### 2.2.2.1 Sub-PLB Spares

Typical FPGA architectures implement logic functions with Look-Up Tables (LUT). As shown in Figure 2-6, *Basic Logic Elements* (BLE) combine each LUT with a flip-flop and output MUX

to enable sequential logic implementation. PLBs, in turn, contain multiple BLEs as in the Virtex-4 architecture, which contains eight BLEs per PLB.

By implementing ten benchmark-circuits, Lakamraju and Tessier [2000] found that, on average, 40% of the utilized 4-input LUTs contained one or more spare input. This suggests that an FPGA application contains inherent spares at a finer granularity than the PLB-level as previously discussed. This PLB repair strategy reserves spare BLEs and implements a hierarchy of fault-handling strategies to take advantage of these spare resources, beginning with the finest granularity: LUT input swap, BLE swap, PLB I/O swap, incremental reroute, and complete reroute.

Given the identification of a faulty LUT input by a fault-detection technique, the sub-PLB fault-handling method attempts to swap the faulty resource with a spare input of the same LUT. Figure 2-6 shows input I2 of BLE1 as a faulty LUT input that may be swapped with a spare LUT input such as input I3 to avoid the fault. After swapping the LUT inputs, the contents of the LUT are modified to compensate for the input change. Whereas Figure 2-6 depicts a full PLB input routing matrix, some FPGA architectures contain only a partial routing matrix, restricting the number of PLB inputs to which a given LUT input may connect. For these architectures, the LUT input swapping method must consider whether the spare LUT input has access to the same PLB inputs as the faulty LUT input to prevent rerouting. If spare LUT inputs with similar connections are available, this method is ideal as it does not require logical or connection changes outside of the BLE. If a spare LUT input is not available, then the entire BLE is considered faulty.

Figure 2-6: PLB Repair Strategies using Sub-PLB spares

When a BLE is considered faulty, as is the case with BLE 3 in Figure 2-6, it is swapped with the reserved spare shown as BLE 4. In the case of partial routing matrices, the BLE swapping method needs to ensure the spare BLE has access to the same PLB inputs as the faulty BLE to prevent rerouting. Figure 2-6 shows that BLE 3 can swap with BLE 4 because of the similarity in connectivity, thus the change only affects the PLB and not the remainder of the circuit. If a spare BLE is not available, then the entire PLB is considered faulty and *incremental rerouting* is required. Incremental rerouting is discussed further in Section 2.3.1.1. Similar to the LUT input swap, faulty PLB input/output wires may be swapped with spare wires that contain similar connections. If a spare PLB input/output wire is not available, then incremental rerouting is required.

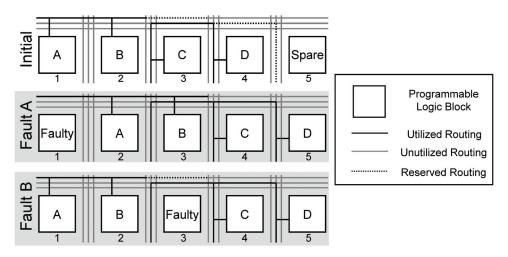

#### 2.2.2.2 PLB Spares

To tolerate logic and interconnect faults within a PLB, Hanchek and Dutt [1998] allocate the rightmost PLB of each row as spare. In the case of a fault, a string of PLBs beginning with the faulty PLB is shifted one PLB to the right. More formally, this technique is *node covering*, which allocates a cover PLB to each PLB. In the case of a fault occurring in a PLB, its cover replaces the functionality of the faulty PLB to avoid the fault. This covering continues within a row in a cascading fashion until the spare PLB at the end of the row is reached. For a PLB to become a cover, it must duplicate 1) its logic functionality and 2) its connectivity to other PLBs. Since PLBs within most FPGA architectures are identical, duplicating logic functionality between PLBs is inherent to the FPGA. Hanchek and Dutt ensure that cover cells duplicate connectivity by incorporating reserved wire segments during the design process.

As seen in Figure 2-7, some routing segments are utilized by the initial configuration whereas others are reserved, one of which is located above location 3. As is the case with Fault Scenario A, this reserved segment becomes utilized by the functionality of PLB B by shifting into location 3. Likewise, the two reserved segments above and to the right of location 4 become utilized by PLB D. Additionally, a design may contain inherent reserved segments where some utilized wire segments of the initial configuration also function as reserved wire segments in a fault scenario. This is seen in Fault Scenario A where PLB B allows its utilized wire segment above location 2 to be used by PLB A. During design-time, a custom tool determines the necessary reserved routing segments to enable the FPGA to tolerate one faulty PLB per row. Two heuristics that increase the efficiency of routing include Segment Reuse and Preferred Routing Direction. Segment Reuse allows a utilized net and a reserved net to map to the same wire segment if the utilized net will move off of the wire segment with the shifting the PLBs, therefore freeing up a wire segment for the reserved net. For nets that

Figure 2-7: Fault scenarios with spare PLBs [Hanchek and Dutt 1998]

cross the FPGA, Preferred Routing Direction encourages the router to extend such nets to the right, horizontally, as far as possible before extending the net in either vertical direction. Providing longer continuous horizontal segments allows greater opportunities for a design to contain inherent reserved segments as discussed above.

Whereas the authors specify that both the logic and interconnect fault-handling technique requires modification to the FPGA architecture and, thus, is intended for manufacturer yield enhancement, end-users may choose to implement the node-covering strategy for tolerating logic faults. Since the design process has ensured that the cover cells can duplicate functionality and connectivity, the routing phase of the place-and-route process is finalized during design-time. To avoid a faulty PLB within a row, an end-user only needs to re-place the PLBs by shifting a row of PLBs into a fault-free configuration. The time to modify an existing configuration by re-placing a row of PLBs is significantly less than the time required either to generate a new configuration from scratch or to incrementally reroute an existing configuration.

## 2.3 Dynamic Processes

Methods using dynamic processes aim to allocate spare resources or otherwise modify the configuration during run-time after detecting the fault. Whereas these approaches offer the flexibility of adapting to specific fault scenarios, additional time is necessary to generate appropriate configurations to repair the specific faults. *Offline* recovery methods require the FPGA's removal from an operational status to complete the refurbishment. *Online* recovery methods maintain some degree of data throughput during the fault recovery operation, increasing the system's availability. Sections 2.3.1 and 2.3.2 respectively address these two types of Dynamic Processes.

## 2.3.1 Offline Recovery Methods

#### 2.3.1.1 Incremental Rerouting Algorithms

The node-covering method discussed in Section 2.2.2.2 avoids a fault by re-placing a circuit into design-time allocated spares using design-time reserved wire segments. Dutt et al. [1999] expand this method by dynamically allocating reserved wire segments during run-time instead of design-time. Run-time reserved wire segments allow the method to utilize unused resources in addition to the spares allocated during design-time.

Emmert and Bhatia [2000] present a similar Incremental Rerouting approach that does not require design-time allocated spare resources. The fault recovery method assumes an FPGA to contain PLBs not utilized by the application, thus exploiting unused fault-free resources to replace faulty resources. Upon detecting and diagnosing a logic or interconnection fault by some detection method, Incremental Rerouting calculates the new logic netlist to avoid the faulty resource. The method reads the configuration memory to determine the current netlist and implements the incremental changes through partial reconfiguration.

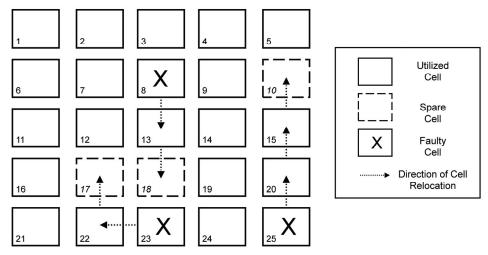

Figure 2-8: One Possible Minimax Fault-Handling Strategy for a 5x5 array

Since faulty PLBs may not be adjacent to a spare resource, a string of PLBs is created logically, starting with the faulty PLB and ending with the PLB adjacent to the spare resource. Figure 2-8 shows one such string, starting with PLB 25, including PLB 20, and ending with PLB 15. To avoid the fault, the string of PLBs shifts away from the faulty resource and towards the spare resource. In the case of node covering, every row has a spare resource so the string of PLBs within the row simply shifts to the right, leaving the faulty resource unused. Since this method does not allocate a spare resource for every row, the string of PLBs may extend into multiple rows to reach a spare PLB as shown in Figure 2-8.

This approach uses *Minimax Grid Matching* (MGM) to determine the optimum re-placement of faulty PLBs. Minimax refers to an algorithm that minimizes the maximum distance, L, between the faulty PLB and an unused, fault-free PLB. Beginning with L=1, Figure 2-8 shows that the faulty cell 23 is adjacent to the spare cell 18 and thus a match, but faulty cells 8 and 25 do not have adjacent spares and thus no matches. Incrementing L to two, faulty cell 23 matches cell 17 while maintaining its match to cell 18. Additionally, faulty cell 8 matches cell 18 and cell 10 whereas faulty cell

25 still has no matching spare. Incrementing L to three, faulty cell 23 acquires no new matches, faulty cell 8 acquires cell 17 as a match and faulty cell 25 matches cell 10 and cell 18. Since all cells have a match at minimax length L=3, one match is then chosen for each faulty cell. Figure 2-8 depicts one such possibility for the three faulty PLBs, where, for example, the logic in cell 23 shifts to cell 22 and the logic in cell 22 shifts to the spare cell 17.

Re-placing PLBs requires the wire segments of the moving PLBs to be rerouted. The configuration memory of the FPGA is read to determine which nets are affected by the re-placed PLBs. All faulty nets and those that solely connect the moved PLBs are ripped-up [Emmert and Bhatia 2000] while those that connect other unmoved PLBs remain unchanged. A greedy algorithm then incrementally reroutes each of the dual-terminal nets to reestablish the application's original functionality. Initially, the algorithm only uses spare interconnection resources within the direct routing path, but may expand its scope to encompass wider routing paths for unroutable nets. Lakamraju and Tessier [2000] expand this work by utilizing historical node-cost information from previous routing attempts to increase the probability of routing success.

#### 2.3.1.2 Genetic Algorithm Repair

Genetic Algorithms (GA) are inspired by evolutionary behavior of biological systems to produce solutions to computational problems [Mitchell 1996]. Suitable for complex search spaces, GAs have proven valuable in a wide range of multimodal or discontinuous optimization problems. Previous research has investigated the capability of GAs to design digital circuits [Miller et al. 1997] and repair them upon a fault [Keymeulen et al. 2000]. Vigander [2001] proposes the use of GAs to repair faulty FPGA circuits. As a proof of concept, Vigander implements extrinsic evolution, utilizing

a simulated feed-forward model of the FPGA device with genetic chromosomes representing logic and interconnect configurations.

The evolution process begins with initializing a population of candidate solutions. These initial solutions contain different physical implementations of the same functional circuit. In the midst of a fault, the performance of each configuration is evaluated, revealing which configurations are most affected by the fault. If none of the available configurations provides the desired functionality, then genetic operators create a new population of diverse candidate solutions from the previous configurations. Those previous configurations having a higher performance rating are more likely to be selected and to combine with other configurations by the *Crossover* genetic operator. Additionally, the *Mutation* genetic operator injects random variations in the newly created candidate solutions. Vigander also makes use of a *Cell Swap* operator that allows the functionality and connectivity of a faulty cell to swap with a spare cell. The GA evaluates the newly created solutions and replaces poorer performers in the old population with better performers in the current population to create a new generation of candidate solutions. This evolutionary process repeats, stopping when an optimal solution is discovered or after a specific number of generations.

## 2.3.1.3 Augmented Genetic Algorithm Repair

To decrease the amount of time required to generate a repair, Oreifej et al. [2006] augment Vigander's GA fault-handling concept with a *Combinatorial Group Testing* (CGT) fault isolation technique. Group Testing partitions suspect resources into groups and coordinates those groups into a minimal number of tests to isolate the faulty resource. If a group manifests a fault within one of these tests, then the group is known to contain the faulty resource and thus the resources within the

group are classified as suspect. In a deterministic manner, the suspect resources are partitioned into iteratively smaller groups and tested until the faulty resource is isolated.

A population within a GA contains various configurations, each of which categorizes the FPGA resources into two groups: utilized and unutilized resources. CGT evaluates each configuration for correct functionality. If a configuration manifests a faulty output, then the resources used by that configuration are considered suspect. Since the various configurations within the population form groups that overlap particular resources, CGT tests multiple configurations and accumulates the number of times each resource is considered suspect through a History Matrix. Configurations are rotated through the FPGA and tested until one element becomes the maximum value within the matrix, isolating the fault to one resource. The GA, in turn, uses the fault location information to avoid faulty resources while evolving a repaired configuration.

## 2.3.2 Online Recovery Methods

#### 2.3.2.1 TMR with Single-Module Repair

In Section 2.2.1.2, faults in TMR arrangements were handled with a-priori, design-time configurations. Methods presented by Ross and Hall [2006], Shanthi et al. [2002], and Garvie and Thompson [2004] address faults dynamically through GA repair. As shown by Figure 2-9, genetic operators and reconfiguration are invoked when a defective module is detected. At design-time, Ross and Hall [2006] produce a population of diverse configurations for implementation. At runtime, three of these configurations are implemented into the circuit and monitored for discrepancies. Agreeing outputs indicate that the modules are functioning correctly whereas discrepancies indicate defective resources utilized by one of the configurations. A simple mutation genetic operator is ap-

Figure 2-9: Single-Module Repair in TMR Arrangement

plied to defective modules and the fitness of the new individual is evaluated. The process repeats until the fault is occluded.

In addition to the strategy above, Shanthi [2002] utilize a deterministic approach in identifying faulty resources. By monitoring the resources within each configuration, resources utilized by viable modules gain confidence whereas resources utilized by faulty modules gain suspicion. This information allows fault handling by implementing configurations not using defective resources. Additionally, differing configurations can be rotated to reveal dormant faults in unused resources.

Instead of selecting from a diverse population, Garvie and Thompson [2004] implement three identical modules. The commonality between configurations permits a *Lazy Scrubbing* technique, which considers the majority vote of the three configurations as the original configuration when scrubbing a faulty module. Of course, Lazy Scrubbing only applies when a GA has not modified the original configurations to tolerate a permanent fault. To address permanent faults, a (1+1) Evolutionary Strategy [Schwefel and Rudolph 1995] provides a minimal GA, which produces one genetically modified offspring from one parent and chooses the most fit between the parent and offspring. To mitigate the possibility for a misevaluated offspring replacing a superior parent, a His-

FPGA operational inputs provide the test vectors to evaluate the fitness of newly formed individuals. To determine correct values, an individual's output is compared to the output of the voter. An individual's fitness evaluation is complete when it has received all possible input combinations.

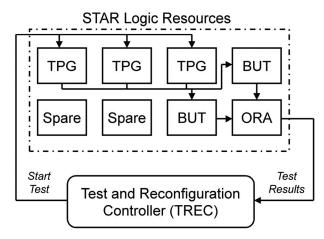

#### 2.3.2.2 Online Built-in Self Test

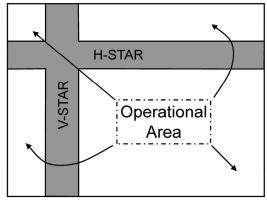

Emmert et al. [2007] present an approach that pseudo-exhaustively tests, diagnoses, and reconfigures resources of the FPGA to restore lost functionality due to permanent faults. The application logic handles transient faults through a Concurrent Error Detection (CED) technique and by periodically saving and restoring the system's state through checkpointing. As shown in Figure 2-10, this method partitions the FPGA into an Operational Area and a *Self-Testing ARea* (STAR), which consists of a Horizontal STAR and a Vertical STAR. Such an organization allows normal functionality to occur within the Operational Area while *Built-In Self Tests* (BIST) and fault diagnosis occurs within the STARs. Whereas other BIST methods may utilize external testing resources assumed fault-free, the resources-under-test also implement the Test-Pattern Generator (TPG) and the Output Response Analyzer (ORA).

To provide fault coverage of the entire FPGA, the STARs incrementally rove across the FPGA, each time exchanging its tested resources for the adjacent, untested resources in the Operational Area. The H-STAR roves top to bottom then bottom to top while the V-STAR roves left to right then right to left. Whereas one STAR can test and diagnose PLBs, two STARs are required to test and diagnose programmable interconnect—the H-STAR for horizontal routing resources and the V-STAR for vertical routing resources. Where they intersect, the two STARs may concurrently test both horizontal and vertical routing resources and the connections between them. Since faults

Figure 2-10: Roving STARs within an FPGA

have equal probability to occur within used resources with unused resources, Roving STARs provides testing for all resources. Uncovering dormant faults in unused resources prevents them from being allocated as spares to replace faulty operational resources.

In addition to facilitating testing, diagnosis, and reconfigurations, a *Test and Reconfiguration Controller* (TREC) is responsible for roving the STARs across the FPGA. The TREC is implemented as an embedded or external microprocessor that communicates to the FPGA through the Boundary-Scan interface. All possible configurations of the STARs are processed during design-time and stored by the TREC for partial reconfiguration during run-time. Relocating the STARs through partial reconfiguration only affects the logic and routing resources within the STAR's current and new locations. When a STAR's next location includes sequential logic, the TREC pauses the system clock until the logic is completely relocated. In addition to pausing the system clock, the TREC implements an Adaptable System Clock where the clock speed is adjusted to account for timing delays arising from new configurations that adapt to faults.

Roving STARs supports a three-level strategy to handling permanent faults. In the first level when a STAR detects a fault, it remains in the same position to cover the fault. Since a STAR contains only offline logic and routing resources, testing and diagnosing time is not at a premium and

the application can continue to operate normally while the TREC tests and diagnoses the fault. After diagnosing the fault, the TREC determines if the fault will affect the functionality that will soon occupy the faulty resources upon moving the STAR. If the fault will not affect the new configuration's functionality, such as only affecting resources that will be unused or spare, then the application's output will not articulate the fault and no action is required. If the fault will affect the new configuration's functionality, then the TREC generates a Fault-Bypassing Roving Configuration (FABRIC) to reroute incrementally the new configuration so that the fault will not affect its functionality. Whereas some FABRICs may be compiled during design-time, most fault scenarios will dictate compiling them online while the STAR covers the fault. While one STAR covers a fault for testing and diagnosis, the second STAR may continue roving the FPGA searching for faults in its respective routing resources and PLBs. The second level strategy then applies the FABRIC that either was compiled during design-time or was generated during the first-level strategy. Replacing a faulty resource with a spare one through a FABRIC thus releases the STAR covering the fault to continue roving the FPGA.

If the fault affects functionality and no spare resources are available to bypass the fault, then the third strategy is invoked. As a last resort, the TREC has an option to perform *STAR Stealing*, which reallocates resources from a STAR to the Operational Area to bypass the fault. Removing resources from a STAR immobilizes it from roving the FPGA. Whereas the second STAR can test all PLBs in an FPGA with an immobile STAR, only half of the routing resources can be tested. In some situations, however, a mobile STAR may intersect and forfeit its resources to an immobile STAR, which releases it to rove the FPGA and test the remaining routing resources.

Figure 2-11: 4x2 Array Configured for a PLB BIST

As previously stated, testing and diagnosis occurs within resources of a STAR as shown by Figure 2-11. Utilizing the resources of the STAR through partial reconfiguration, the TREC configures a TPG, an ORA, and either two Blocks Under Test (BUT) for a PLB test or two Wires Under Test (WUT) for an interconnect test. Since no resource may be assumed to be fault-free, the TPG, BUTs/WUTs, and ORA are rotated through common resources of the STAR. The TREC maintains the results for all test configurations so that the common faulty resources can be identified between the two parallel BUTs or WUTs and the rotation of resources.

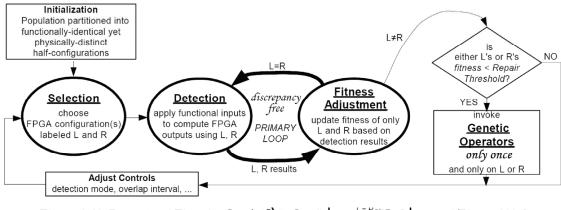

## 2.3.2.3 Consensus-based Evaluation of Competing Configurations

Whereas previous Online GA methods utilize an N-MR voting element, the *Competitive Runtime Reconfiguration* (CRR) proposed by DeMara and Zhang [2005] handle faults through a pairwise functional output comparison. Similar to previous GA methods, each of the two individuals is a unique configuration on the target FPGA exhibiting the desired functionality. CRR divides the FPGA into two mutually exclusive regions, allocating the *Left Half* configuration to one individual and the *Right Half* configuration to another individual in the population of alternate configurations.

This detection method realizes a traditional CED arrangement that allocates mutually exclusive resources for each individual. The comparison results in either a discrepancy or a match between half-configuration outputs, which detects any single resource fault with certainty. This indicates the presence or absence of a FPGA resource fault for all inputs that articulate the fault when applied to a combinational logic module or a pipeline stage consisting of combinational logic.

The Left and Right individuals of the pairwise comparison are selected from their respective Left and Right populations to maintain resource exclusivity. Functionally identical, yet physically distinct, <code>Pristine</code> individuals developed at design-time compose the initial population. As Figure 2-12 shows, the Left and Right individuals remain <code>Pristine</code> as long as the Left and Right individuals exhibit matching outputs. Additionally, the fitness values of both individuals are increased to encourage selection of individuals exhibiting correct behavior. Upon detecting a discrepant output, however, the fitness state of both individuals are demoted and labeled as <code>Suspect</code>. Furthermore, the fitness values of both individuals are decreased to discourage selection of individuals exhibiting discrepant behavior. Over many pairings and evaluations, the fitness value of individuals utilizing faulty resources, and therefore its probability for selection, will be decreased regardless of pairing. Moreover, non-faulty individuals that were previously paired with faulty individuals will eventually be exonerated.

Figure 2-12 shows that the fitness state of individual *i*, which has been labeled as Suspect, is further demoted when its fitness (f<sub>i</sub>) drops below the Repair Threshold (f<sub>RT</sub>). Genetic operators are applied to the Under Repair individual, until its fitness rises above the Operational Threshold (f<sub>OT</sub>). Selecting an Operational Threshold greater than the Repair Threshold increases confidence that the individual, in fact, is Refurbished. Further matching pairings with the Refurbished individual can result in either a Partial or Complete Regeneration of lost functionality. Nonetheless, if the

Figure 2-13: Procedural Flow for Competing Configurations [DeMara and Zhang 2005] COMPETITION integral with REGENERATION  $f_i < f_{RT}$  under repair

Figure 2-12: States of an Individual during its Lifetime [DeMara and Zhang 2005]

individual exhibits further discrepant behavior, its fitness state is returned to Under Repair and genetic operators are reapplied.

Figure 2-13 shows the CRR processes of Selection, Detection, Fitness Adjustment, and Evolution. These processes identify individuals utilizing faulty resources and refurbish those individuals in the midst of the fault. The Selection Process determines the two individuals that will occupy the Left and Right regions. Typically, one of the halves is reserved as a "control" configuration where fault-free operational individuals, such as Pristine, Suspect, and Refurbished in that order, are always preferred. The other half supersedes these operational individuals with Under Repair individuals at a rate equal to the Re-introduction Rate. Under Repair individuals that are genetically modified compete by being re-introduced into the operational throughput. The Re-introduction Rate can be adjusted to achieve a desired recovery goodput during the repair process. This assumes that alternative configurations exhibiting fault-free behavior over a window of recent inputs remain available or that the GA has already refurbished configurations within the population.

Applying an input to the Left and Right individuals invokes the Fitness Adjustment process. As previously discussed, matching outputs results in increases to the fitness value of both individuals. Discrepant outputs decrease the fitness value with a steeper gradient and, consequently, the probability that either individual is selected again. This process negatively or positively reinforces certain individuals by decreasing or increasing its fitness appropriately. If an individual's fitness is less than the Repair Threshold, a single application of genetic operators such as crossover and mutation are performed with a random Pristine individual. The checking logic is embedded in the individual and is dependent on the other half. Thus, if the checking logic in one of the halves experiences a fault, it will propagate to the other half, causing the fitness of the individuals to decrease. Additionally, the checking logic is subject to repair by the genetic operators. This implements a check-the-checker concept to enhance its fault tolerance. Variation of the Re-introduction Rate then allows control over how frequently the genetically modified offspring are allowed to compete with the rest of the population.