## SUSTAINABLE FAULT-HANDLING OF RECONFIGURABLE LOGIC USING THROUGHPUT-DRIVEN ASSESSMENT

by

CARTHIK ANAND SHARMA B.Tech. Kakatiya University, 2001 M.S. University of Central Florida, 2004

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2008

Major Professor: Ronald F. DeMara

© 2008 Carthik Anand Sharma

## ABSTRACT

A sustainable *Evolvable Hardware (EH)* system is developed for SRAM-based reconfigurable *Field Programmable Gate Arrays (FPGAs)* using outlier detection and group testing-based assessment principles. The fault diagnosis methods presented herein leverage throughput-driven, relative fitness assessment to maintain resource viability autonomously. Group testing-based techniques are developed for adaptive input-driven fault isolation in FPGAs, without the need for exhaustive testing or coding-based evaluation. The techniques maintain the device operational, and when possible generate validated outputs throughout the repair process.

Adaptive fault isolation methods based on discrepancy-enabled pair-wise comparisons are developed. By observing the discrepancy characteristics of multiple *Concurrent Error Detection (CED)* configurations, a method for robust detection of faults is developed based on pairwise parallel evaluation using Discrepancy Mirror logic. The results from the analytical FPGA model are demonstrated via a self-healing, self-organizing evolvable hardware system. Reconfigurability of the SRAM-based FPGA is leveraged to identify logic resource faults which are successively excluded by group testing using alternate device configurations. This simplifies the system architect's role to definition of functionality using a high-level *Hardware Description Language (HDL)* and system-level performance versus availability operating point. System availability, throughput, and mean time to isolate faults are monitored and maintained using an *Observer-Controller* model. Results are demonstrated using a *Data Encryption Standard*

*(DES)* core that occupies approximately 305 FPGA slices on a Xilinx Virtex-II Pro FPGA. With a single simulated stuck-at-fault, the system identifies a completely validated replacement configuration within three to five positive tests. The approach demonstrates a readily-implemented yet robust organic hardware application framework featuring a high degree of autonomous self-control.

I dedicate this to all those who believed in me, listened to me, and helped me. I wish to thank my grand mother Mrs. G. Bhageerathi Ammal, father Mr. V. Narayan, and sister Mrs. Gina Kartik for their phenomenal support in the 25 years I have spent in school. I also wish to thank Dr. DeMara for his patient guidance and technically-sound advice, Prerona Chakravarty for the mental and moral support, Kening Zhang for being the best colleague possible, and all my roommates past and present for their kindness.

# ACKNOWLEDGMENTS

The research presented in this dissertation was supported in part by NASA Intelligent Systems NRA Contract NNA04CL07A.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                                  |                                                                  |    |  |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----|--|

| LIST OF TABLES                                                                                   |                                                                  |    |  |

| LIST OF ACRONYMS/ABBREVIATIONS xiv                                                               |                                                                  |    |  |

| CHAPTER 1: INTRODUCTION                                                                          |                                                                  |    |  |

| 1.1. Need for Evolvable Hardware Regeneration Methods and Group Testing-based<br>Fault Diagnosis |                                                                  |    |  |

| 1.2.                                                                                             | Fault Handling in Reconfigurable Devices                         | 4  |  |

| 1.3.                                                                                             | Individual and Population-Centric Fault Assessment               | 6  |  |

| 1.4.                                                                                             | Group Testing Techniques and Applications to Fault Tolerance     | 8  |  |

| 1.5.                                                                                             | Contributions of this Dissertation                               | 10 |  |

| CHAPT                                                                                            | ER 2: PREVIOUS WORK                                              | 12 |  |

| 2.1.                                                                                             | Taxonomy and Nomenclature of FPGA Fault Tolerance Techniques     | 13 |  |

| 2.2. Static Run-time Fault Handling Methods                                                      |                                                                  |    |  |

| 2.3. Dynamic Run-time Fault Handling Methods                                                     |                                                                  |    |  |

| 2.3.1. Offline Recovery Methods                                                                  |                                                                  | 19 |  |

| 2.3.                                                                                             | 2. Online Recovery Methods                                       | 23 |  |

| 2.4.                                                                                             | Fault Detection and Location using Exhaustive Testing Techniques | 29 |  |

| 2.5.                                                                                             | Forming a Robust Consensus from Diversity                        | 31 |  |

| 2.6.                                                                                             | Improving Reliability using Autonomous Group Testing             | 32 |  |

| CHAPTER 3: COMPETITIVE RUNTIME RECONFIGURATION FAULT<br>HANDLING PARADIGM                        |                                                                  | 34 |  |

| 3.1.                                                                                             | Detecting Faults using a Population of Alternatives              | 35 |  |

| 3.2.                                                                                             | Assessing Individual Fitness and Managing Fitness States         | 36 |  |

| 3.3.             | Strategic Prioritization of Individuals for Assessment and Refurbishment 39 |      |

|------------------|-----------------------------------------------------------------------------|------|

| 3.4.             | Determination of Evaluation Window                                          |      |

| 3.5.             | Identifying Outliers using the Sliding Window Technique                     |      |

| 3.6.             | Outlier Detection and Fault Isolation Performance with Runtime Inputs .     |      |

| 3.7.             | Feed-Forward FPGA Circuit Representation Model                              | . 55 |

| 3.8.<br>Study    | Refurbishment of a Unique Failed Configuration – 3-bit×3-bit Multiplier C   |      |

| СНАРТИ           | ER 4: FAULT ISOLATION USING GROUP TESTING                                   | . 63 |

| 4.1.             | Motivating Example and Problem Definition                                   | . 63 |

| 4.2.             | Fault Isolation by Discrepancy-Enabled Repetitive pairing                   | . 65 |

| 4.3.             | Designing a Discrepancy Mirror – Case Study                                 | . 67 |

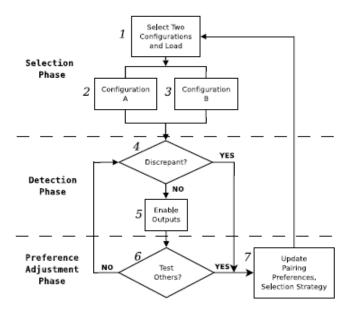

| 4.3.             | 1. Selection Phase                                                          | . 68 |

| 4.3.2            | 2. Detection Phase                                                          | . 68 |

| 4.3.             | 3. The Preference Adjustment Process                                        | . 72 |

| 4.4.             | Analysis of Fault Isolation with a Simplified Articulation Model            | . 72 |

| 4.5.             | Fault Isolation using Halving and Column-Swapping                           | . 78 |

| 4.6.             | Isolating Embedded Cores using Group Testing                                | . 81 |

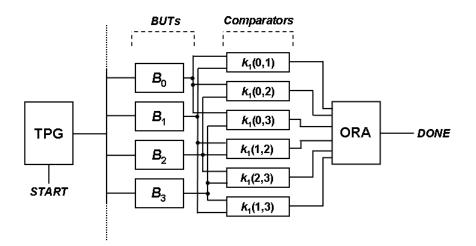

| 4.6.             | 1. BIST-based Testing of Embedded FPGA Cores                                | . 82 |

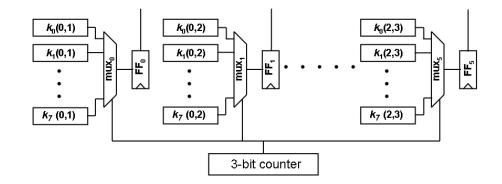

| 4.6.2            | 2. Enhancing Embedded Core BIST using Group Testing Techniques              | . 86 |

| 4.6.             | 3. Embedded Core Fault Isolation Experiments on Virtex-5 FPGAs              | . 88 |

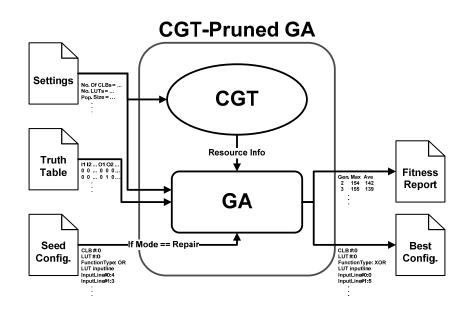

| 4.7.             | Improving GA Performance Using CGT                                          | . 91 |

| CHAPTE<br>TESTIN |                                                                             | )    |

| 5.1.<br>Techn    | Terminology and Nomenclature for Analysis of Autonomous Group Testing       |      |

| 5.2.             | Autonomous Group Testing Algorithm Overview                                 | . 97 |

| 5.3.            | Tracking Defectives Using the History Matrix                     |     |  |  |

|-----------------|------------------------------------------------------------------|-----|--|--|

| 5.4.            | The Equal Sharing Test Group Formation Strategy                  |     |  |  |

| 5.5.            | Adapting the Population Size for Optimal Resource Coverage       |     |  |  |

| 5.6.            | Overcoming Stasis During Isolation                               |     |  |  |

| 5.7.            | Walkthrough of Isolation Process                                 |     |  |  |

| 5.8.            | The Fault Isolation and Analysis Toolkit for Xilinx FPGAs        | 107 |  |  |

| 5.9.            | Creating and Modifying Alternatives with FIAT                    | 110 |  |  |

| CHAPT<br>SUSTAI | ER 6: CHARACTERISTICS, CAPABILITIES, AND METRICS FOR INABILITY   | 114 |  |  |

| 6.1.            | Experimental Configuration for the Xilinx Virtex II Pro FPGA     | 114 |  |  |

| 6.2.            | Isolation Progress Across Test Stages in AGT                     | 119 |  |  |

| 6.3.            | Effect of Population Preset on Defect Scouring Rate              | 121 |  |  |

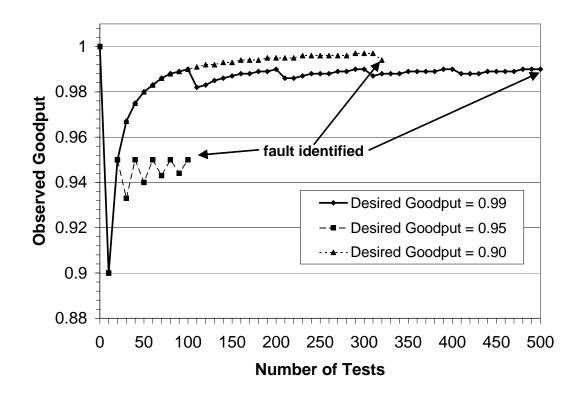

| 6.4.            | Maintaining System Throughput During Fault Isolation             | 125 |  |  |

| CHAPT           | ER 7: CONCLUSION                                                 | 128 |  |  |

| 7.1.            | Graceful Degradation of Performance                              | 128 |  |  |

| 7.2.            | Improving Evolutionary Repair using a Population of Alternatives | 130 |  |  |

| 7.3.            | Fast Fault Response using Group Testing                          | 131 |  |  |

| 7.4.            | Future Work                                                      | 132 |  |  |

| REFERENCES      |                                                                  |     |  |  |

# LIST OF FIGURES

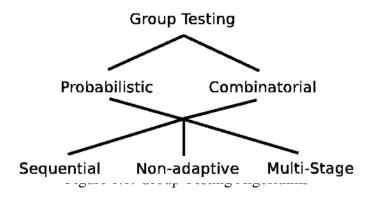

| Figure 1.1: Group Testing Algorithms                                                               |

|----------------------------------------------------------------------------------------------------|

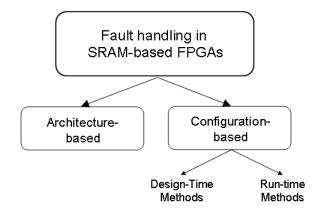

| Figure 2.1: Classification of FPGA Fault Handling Methods 14                                       |

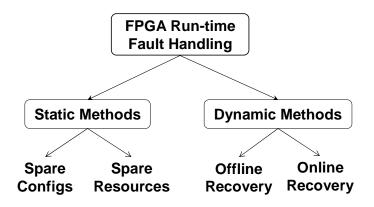

| Figure 2.2: Overview of Run-time Fault Handling Methods 15                                         |

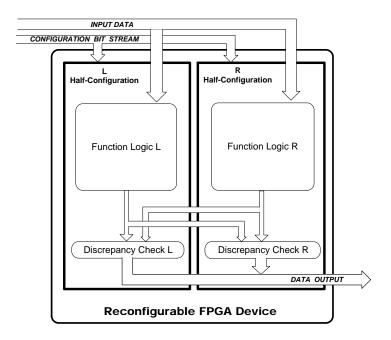

| Figure 3.1: Physical Arrangement with Two Competing Configurations                                 |

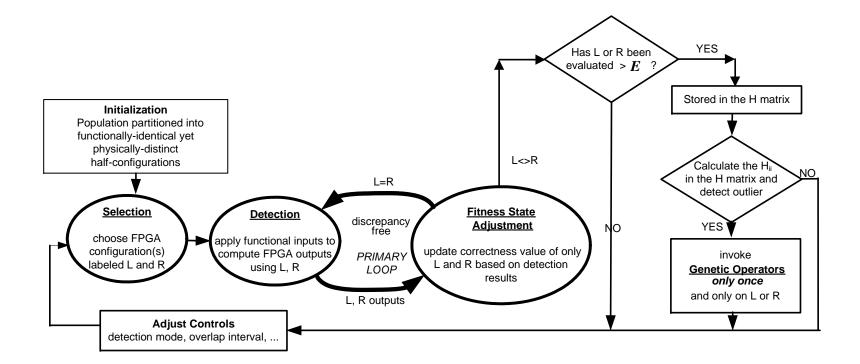

| Figure 3.2: Procedural Flow in the CRR Technique                                                   |

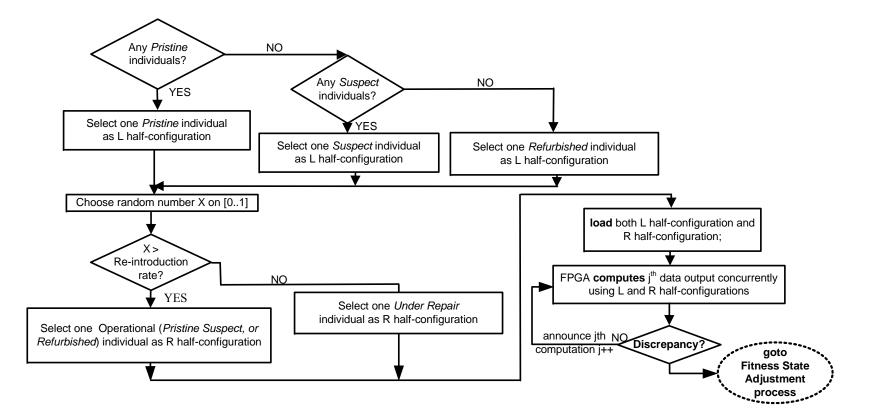

| Figure 3.3: Selection and Detection in the CRR Paradigm                                            |

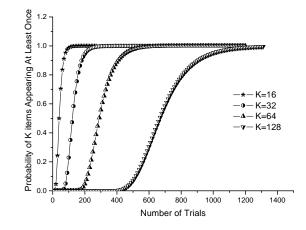

| Figure 3.4: Effect of Sample Size on Test Coverage                                                 |

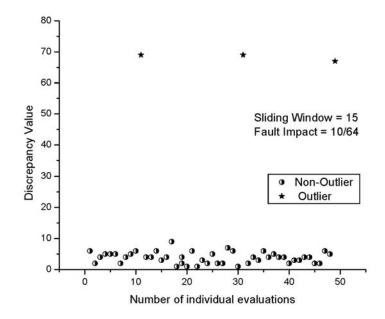

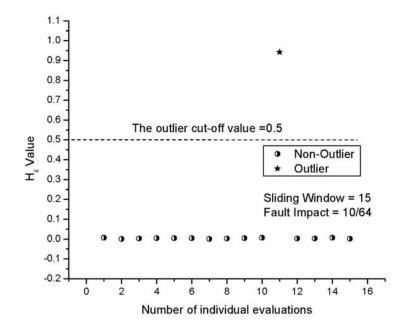

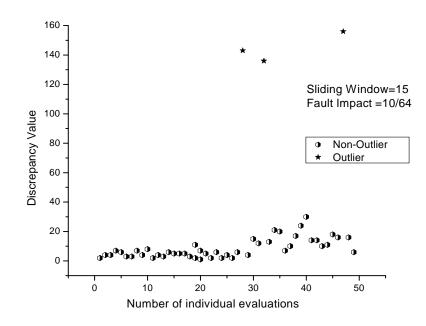

| Figure 3.5: Discrepancy Values Observed when One Individual has a 10-out-of-64 Fault<br>Impact     |

| Figure 3.6: Plot of $H_{ii}$ Showing Outlier Identification                                        |

| Figure 3.7: Discrepancy Values Observed When Hamming Distance is Used 51                           |

| Figure 3.8: Plot of $H_{ii}$ Showing Outlier Identification When Hamming Distance is Used 52       |

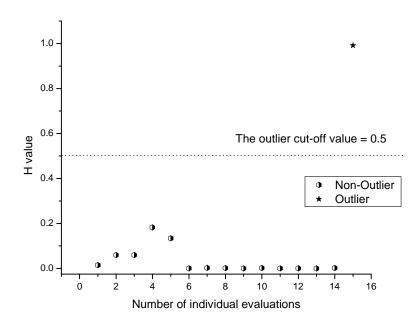

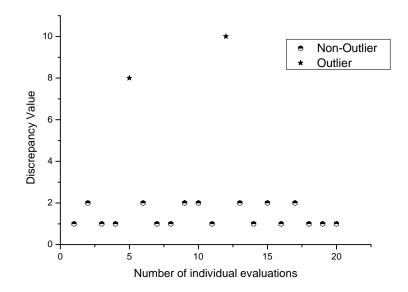

| Figure 3.9: <i>DV</i> of a Single Faulty <i>L</i> Individual With a 1-out-of-64 Fault Impact 53    |

| Figure 3.10: Isolation of a Single Faulty <i>L</i> Individual With a 1-out-of-64 Fault Impact . 53 |

| Figure 3.11: <i>DV</i> s Observed When a Single Faulty Individual has a 32-out-of-64 Fault Impact  |

| Figure 3.12: Isolation of a Single Faulty <i>L</i> Individual with a 32-out-of-64 fault Impact. 55 |

| Figure 3.13: Example of a 3-bit×3-bit Multiplier Design                                            |

| Figure 4.1: Discrepancy Mirror-based Scheme                                                        |

| Figure 4.2: Discrepancy Detection Circuit                                             | 68        |

|---------------------------------------------------------------------------------------|-----------|

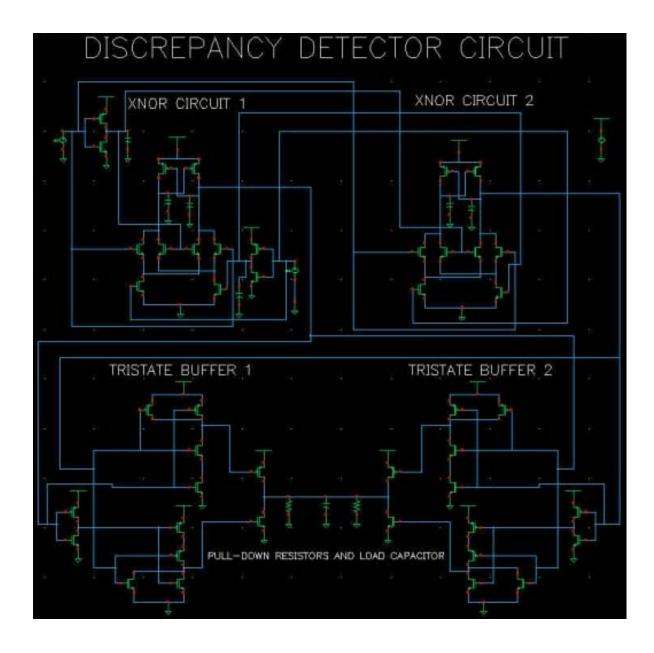

| Figure 4.3 Discrepancy Detector Circuit Schematic Layout                              | 70        |

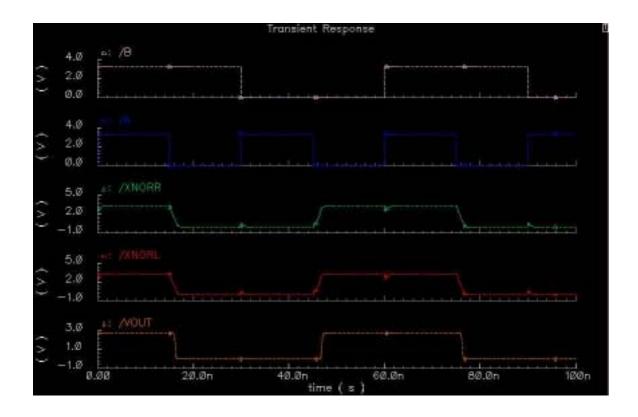

| Figure 4.4 Transient Response of the CMOS Discrepancy Detector Circuit                | 71        |

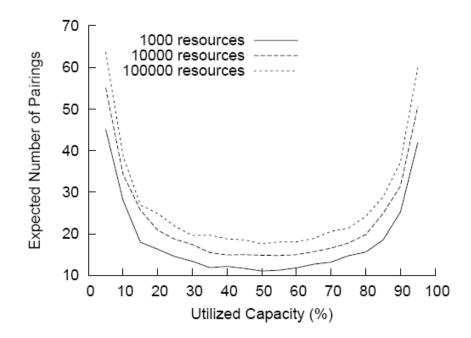

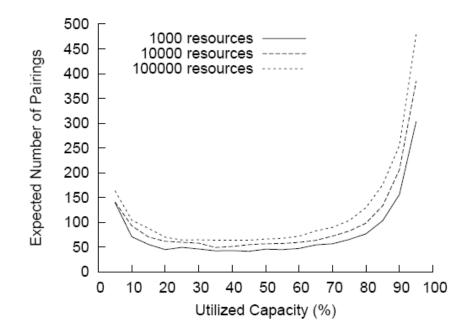

| Figure 4.5: Fault Isolation with Perpetually Articulating Inputs                      | 75        |

| Figure 4.6: Fault Isolation with Intermittently Articulating Inputs                   | 76        |

| Figure 4.7: Successive Isolation as Input Iterations Increase                         | 78        |

| Figure 4.8: Isolation Progress when Halving is used                                   | 79        |

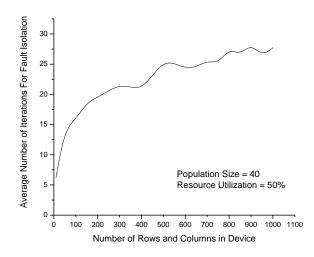

| Figure 4.9: Isolation Performance as a Function of the Total Number of Elements       | 80        |

| Figure 4.10: Isolation Performance as a Function of the Population Size               | 81        |

| Figure 4.11: BIST Structure for Testing a Group of Four Blocks Under Test             | 87        |

| Figure 4.12: BIST Structure used for Testing the XC5VLX30 Device                      | 89        |

| Figure 4.13: CGT-Pruned GA Simulator                                                  | 92        |

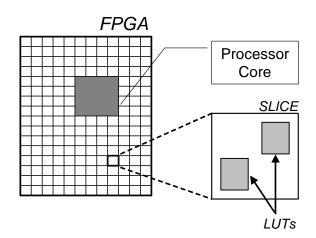

| Figure 5.1: FPGA Resources as Seen by the Group Testing Algorithm                     | 94        |

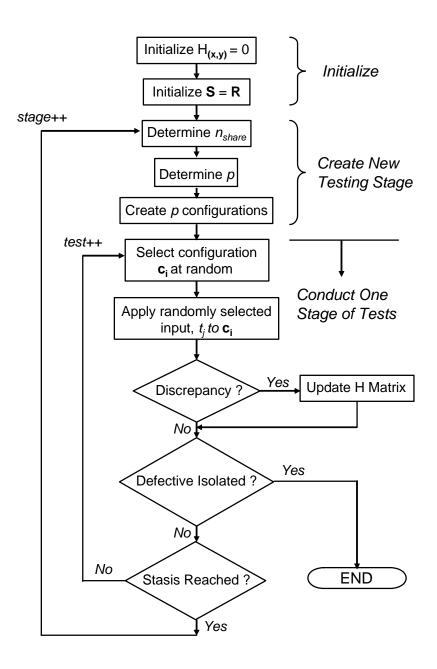

| Figure 5.2: AGT Process Flow                                                          | 98        |

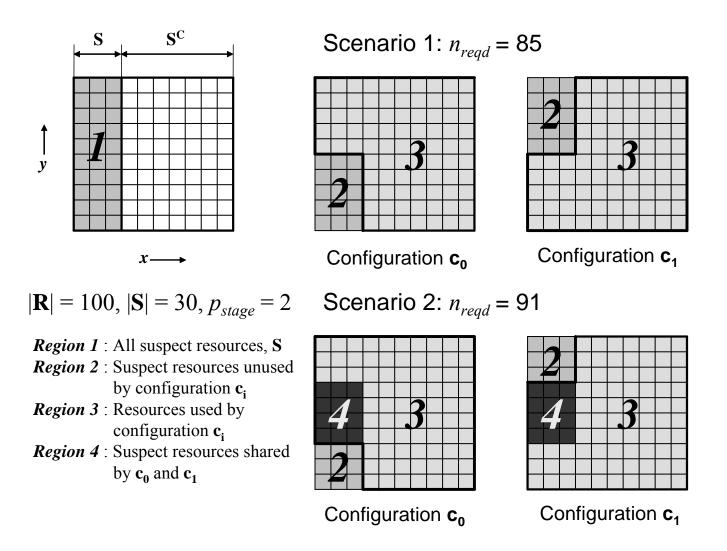

| Figure 5.3: Sharing the Suspect Resources Equally – Two Different Scenarios 1         | 02        |

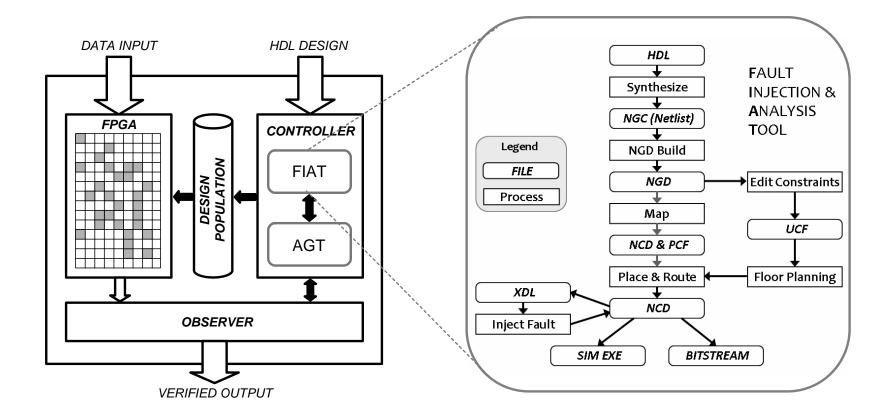

| Figure 5.4: Fault Isolation Using FIAT – An Overview 1                                | 12        |

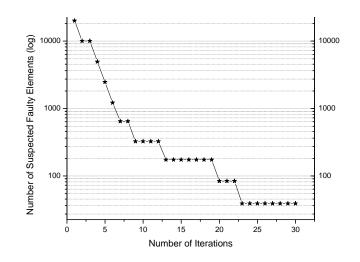

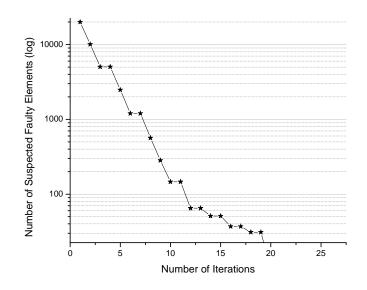

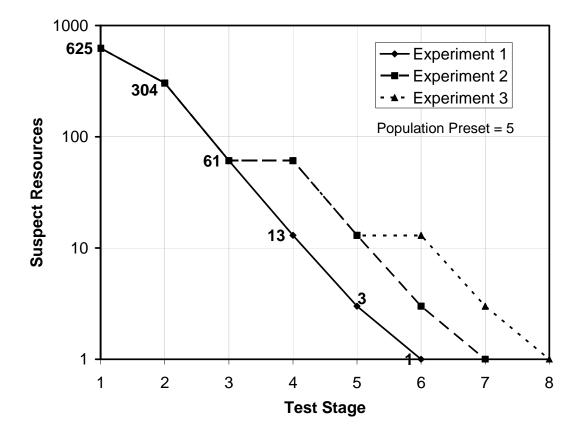

| Figure 6.1: Fault Isolation Progress Across Stages for $p_{preset} = 5$               | 20        |

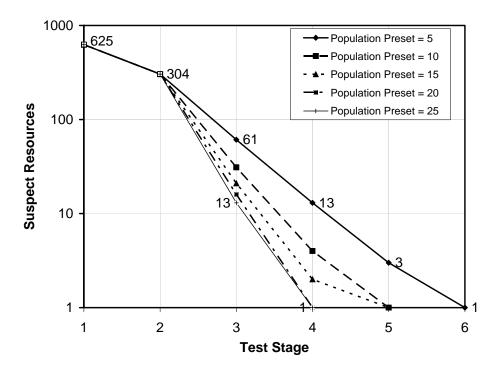

| Figure 6.2: Effect of Population Preset on the Scouring Rate                          | 23        |

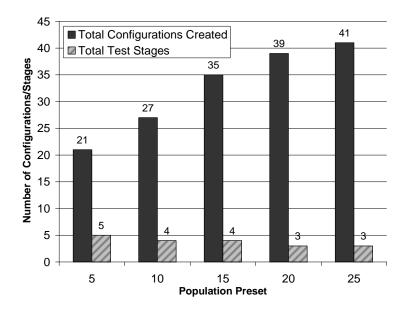

| Figure 6.3: Total Test Stages and Configurations Created for Varying Population Press | ets<br>24 |

# LIST OF TABLES

| Table 2.1: Characteristics of Related FPGA Fault-Handling Schemes       30                                        |

|-------------------------------------------------------------------------------------------------------------------|

| Table 3.1: Probability of all 64 Inputs Appearing At Least Once given D Evaluations 46                            |

| Table 3.2: Regeneration Characteristics for a Single Fault under CBE    59                                        |

| Table 4.1: Comparison of Fault-Detection Techniques    66                                                         |

| Table 4.2: Discrepancy Mirror Truth Table                                                                         |

| Table 4.3: Discrepancy Mirror Fault Coverage and Response    73                                                   |

| Table 4.4: Resource Utilization Results from Experiments Conducted on the Xiling         Virtex-5 Family of FPGAs |

| Table 4.5: CGT-Pruned GA - Repair Performance    93                                                               |

| Table 6.1: Results from Experiments With Varying Population Preset Values                                         |

# LIST OF ACRONYMS/ABBREVIATIONS

| ADAS | Advanced Data Acquisition System    |

|------|-------------------------------------|

| AGT  | Autonomous Group Testing            |

| BIST | Built-In Self Test                  |

| CBE  | Consensus Based Evaluation          |

| CED  | Concurrent Error Detection          |

| CGT  | Combinatorial Group Testing         |

| CLB  | Configurable Logic Block            |

| CRC  | Cyclic Redundancy Check             |

| CRR  | Competitive Runtime Reconfiguration |

| DES  | Data Encryption Standard            |

| DV   | Discrepancy Value                   |

| EH   | Evolvable Hardware                  |

| FIAT | Fault Insertion and Analysis Tool   |

| FPGA | Field Programmable Gate Array       |

| GA   | Genetic Algorithm                   |

| HDL  | Hardware Description Language       |

| LUT  | Look-Up Table                       |

| MTBF | Mean Time Between Failures          |

| MTTR | Mean Time To Recover                |

| TMR  | Triple Modular Redundancy           |

| VLSI | Very Large Scale Integrated         |

|      |                                     |

### CHAPTER 1: INTRODUCTION

Reliable and efficient detection, isolation, and handling of failures within electronic circuits are fundamental issues in the design of dependable devices. With production exceeding 100 million units per year, SRAM-based FPGA devices are frequently used in a wide range of embedded applications requiring high levels of reliability and availability.

## 1.1. <u>Need for Evolvable Hardware Regeneration Methods and Group Testing-</u> <u>based Fault Diagnosis</u>

Reconfigurable devices, such as FPGAs, enable new fault handling techniques based on *evolvable hardware regeneration*. Evolvable hardware regeneration techniques use the principle of biological evolution to handle faults. Using evolutionary techniques such as genetic algorithms and cellular automata, the existing redundant hardware resources are reused or rewired to occlude the fault. The repair process can take place *online* when the hardware is in active use, or *offline* when the regeneration occurs as part of a process outside the normal computation dataflow.

Such techniques are highly relevant to many embedded device applications, including remote sensing, applications in hazardous environments, and space missions. For instance, deep space satellites such as Stardust contain over 100 FPGA devices [1] while NASA terrestrial applications routinely employ FPGAs extensively for tasks ranging from launch control to signal processing. SRAM-based FPGAs are of significant

importance due to their high density, unlimited reprogrammability, and growing use in mission-critical/safety-impacting applications.

Depending on the application, these devices encounter harsh environments of mechanical/acoustical stress, high ionizing radiation, and thermal stress. Simultaneously, they are required to operate reliably for long durations with limited or absent capabilities for diagnosis/replacement in the case of remote applications. For example, in Aerospace Technology, Space Science, and Earth Science enterprises, the impact from increased safety and autonomy for FPGAs is highly relevant. On-going research at Ames [2] and JPL [3] has focused specifically on employing the reconfigurability inherent in various field programmable devices to increase their reliability and autonomy using evolutionary mechanisms.

Ground-based applications of FPGAs such as data acquisition devices and instrumentation systems seek to incorporate self-repair capabilities and provide extended calibration cycles. One such application is Kennedy Space Center's *Advanced Data Acquisition System (ADAS)* [4]. ADAS is a signal acquisition and processing system for launch control measurements typical of real-time NASA applications that heavily utilize FPGAs and have high reliability, availability, and maintainability requirements. Some target components that will benefit from evolvable hardware repair include Analog Signal Modules, Digital Signal/Control Modules, and Power Management Modules.

There is the need to integrate multiple phases of the fault handling process in an integrated manner. Further, this should ideally be done while maintaining the uptime,

and availability of the reconfigurable device. Evolutionary mechanisms can actively restore mission-critical functionality in SRAM-based FPGA devices. They provide an attractive alternative to device redundancy for resolving permanent degradation due to radiation-induced stuck-at-faults, thermal fatigue, oxide breakdown, electro-migration, and other failures. Potential benefits include recovery without the increased weight and size normally associated with spares. Without regeneration, spare capacity is finite. Therefore, an evolutionary fault handling strategy that relies upon resource recycling by means of leveraging the reconfigurability of FPGAs is required. Regeneration also provides for graceful degradation of performance with time, where resources are constantly recycled with minimal impact on system availability. The capability to recycle resources at a variable rate, as afforded by evolutionary mechanisms provides the capability to delay refurbishment to maintain required availability and throughput requirements. Such a strategy would rely upon fault isolation to accelerate the evolutionary repair. However, failures need not be precisely diagnosed due to automatic evaluation of FPGA residual functionality through intrinsic assessment using a specified fitness function.

Evolutionary mechanisms rely upon efficient fault detection and isolation schemes. Fault detection triggers the regeneration operation. Robust fault detection techniques are required to detect fault and failures with a low latency. Fault location methods provide inputs to the repair mechanism which accelerate the repair process, and reduce the search space of candidate solutions to the fault scenario. The fault isolation technique identified

in this work is one such method for isolating faults with low latency and minimal overheads.

### 1.2. Fault Handling in Reconfigurable Devices

An operational *failure* occurs when the service delivered deviates from its as-built specification. A resource *fault* is the cause of such failures. *Fault handling* refers to the entire process by which potential or actual failures are dealt with. Ideally, fault handling maintains failure-free functionality.

The process of improving fault handling typically involves *detection, isolation, diagnosis,* and *repair.* The detection phase consists of identifying the presence of a fault in the device. A fault is said to be *detected* when the effects of a corresponding failure is observed. Depending on whether the inputs applied manifest an observable failure, the fault is either be *perpetually articulated* or *intermittently articulated*. The articulation of the fault, and hence its potential for detection, relies on the mapping of the functional design to the physical resources. Once a failure has been detected, it may be possible to isolate the faulty resources. Fault *location* or *isolation* determines the physical location of the faulty components. The granularity of isolation may vary, depending on the architecture, the algorithm, and the isolation tools available. Fault *diagnosis* thus deals with the determination of the symptoms and the reason behind the observed failure. A *symptom* is an observable effect of a fault. Failures are among the most easily observed symptoms of a fault and are the basis for the isolation methods developed in the proposed research. The diagnosis phase may involve obtaining the response of the device to an

exhaustive set of inputs using a tool designed solely for performing diagnostic tests. The last phase consist of fault repair, wherein the effects of the fault are ameliorated to reduce the occurrence or impact of future failures.

The particular fault handling approach can be classified on the basis of when the faults are accounted for in the development cycle. *Design Time* approaches place the emphasis on *Fault Avoidance* strategies through design strategies that avoid the occurrence of faults. *Execution Time* or *Run Time* approaches tackle the problem by using *Fault Tolerance* and *Fault Evasion* methods. A *Fault-Tolerant system* is characterized by its ability to provide uninterrupted service, conforming to the desired levels of reliability even in the presence of faults. A *dependable* or *reliable system* is one which offers a level of service that is characterized by its *availability* or readiness for use when desired.

Embedded fault-handling techniques can also be broadly categorized as diagnostic-based [5], coding-based [6], or redundancy-based [7], depending on the method used to implement fault-handling. Diagnostic-based techniques execute a supplemental procedure that applies a test vector to a subset of the physical resources. While diagnostics offer a compact approach, they can suffer from unavailability of throughput during testing, a large detection latency, and intractability of search as the number of physical resources and their piecewise interactions grow large [8]. Coding-based techniques map the input values to an alternate representation to enforce constraints on the validity of the outputs. Such encodings based on parity, CRC, Berger, and other codes can be effective for data storage and transmission [9]. However, they preclude the occurrence of failures that might map one valid codeword onto another, and thus their

general applicability for FPGA logic resources is limited. To avoid such limitations, embedded techniques frequently rely on component or system-level redundancy.

Fault detection methods are central to fault handling strategies. Fault detection can be carried out by a mechanism outside the domain of the system under observation. In some cases it is not feasible to have a separate supervisory system in addition to the system under test. For such a system to be fault tolerant, it is imperative that the fault detection tool or system used be fault-tolerant as well, since it will be a part of the system under observation. To maintain acceptable availability levels, reduction of the fault detection latency is essential. An evolutionary hardware repair strategy can use the information provided by the fault isolation strategy to speed up the repair process. In CRR, accurate knowledge of the physical location of the fault can provide useful inputs to the repair algorithm. The fault detection and isolation strategy used should ideally be capable of identifying and locating faults without requiring special test inputs, or an interruption in the normal data throughput. The hardware resources used by the detector should be minimal, in order to reduce the number of points of failure, and to conserve floor space. The detector should be *fault-secure* meaning it does not propagate incorrect outputs in the presence of a fault. Section 2.2 provides a detailed overview of selected fault detection strategies.

#### 1.3. Individual and Population-Centric Fault Assessment

Traditional approaches to fault-detection typically rely on coding-based schemes or redundancy using a single voter, comparator, or error detector. Those fault checkers possess a single point-of-failure exposure involving the detector elements, or must rely upon special test-vectors or data encodings to isolate them. Detector components in the reliability path have been referred to as golden elements [10] because the fault-handling strategy relies on them to be fault-free. Also, significantly, previous methods test individual configurations or resource units to evaluate their *fitness*. While such individual-fitness centric methods provide fault coverage on the device level, they do not lend to an adaptive, evolving system.

In a redundant system, the problem of fault detection can be simplified by the fact that if there are no faults, then the outputs of the redundant elements should be identical. An observed deviation from the this property would imply that the disagreement is a result of a failure in at least one of the redundant components. Natural laws of competition, as seen in biological evolution can be applied to improve the performance of electronic circuits. In fault-detection, a deviation from the normal behavior, as determined by comparison with another individual design, signifies a state of decreased fitness, as a result of the manifestation of a hardware fault.

The idea of competition can also be extended to the repair problem, using competitive pairing as a fitness evaluation technique. Traditional GAs use an absolute measure of fitness for the individuals to search for improved solutions. In this work, the fitness of an individual design configuration depends on relative measures computed over a period of time. The proposed fitness assessment process involves accumulation of discrepancies across multiple random pairings with other individuals from the population. Such a population-based approach greatly simplifies the process of fault diagnosis, and uses the

fact that the circuit under test continues to operate for the duration of its useful lifetime to accrue information about the performance of competing individuals. By keeping the method of fault isolation simple, the cost of repair is reduced and amortized over time, thus providing a fault-secure system without acceptable overhead.

#### 1.4. Group Testing Techniques and Applications to Fault Tolerance

Group testing is a field of mathematics concerned with the development of efficient algorithms to identify defective members from a large population. The origin of group testing is attributed to Robert Dorfman who proposed the first application during World War II. He devised a scheme for testing blood samples from millions of United States army draftees for cases of syphilis [11]. He proposed that the blood samples be pooled for testing, in order to reduce the number of tests required and the associated cost and effort. If a pool of samples tested positive for syphilis, then the samples that contributed to the pool would be subject to individual testing. Though this idea of testing groups to identify faulty units was not practically implemented at the time, it gained currency and has been the subject of intensive research since. The monograph [12] provides a detailed look into the current state of group testing applications. The fundamental group testing problem is to identify a subset Q of defective items from a set P, by conducting the minimum number of tests on v – subsets of P. A test seeks to identify whether a particular v – subset is defective, as shown by a positive outcome of the test [11]. Group testing algorithms are classified as shown in Figure 1.1.

Probabilistic group testing theory assumes a known probability p of an item being defective, and uses it to guide the isolation process. In Combinatorial Group Testing (CGT), it is often assumed that D is the subset of defective items among S items whereby p = |D| = |S|. In sequential group testing algorithms, tests are conducted in succession so that the results of previous tests are known to guide the current test. In a non-adaptive test, the tests are pre-designed and executed in parallel, without cognition of the result of other tests. In a *multi-stage* algorithm, successive stages of tests utilize informative from previous stages, and tests in a particular stage are executed in parallel. Testing is conducted using a checker or a detector which tests subgroups comprising items from S. A group testing algorithm is *reasonable* if it contains no test whose outcome can be predicted from outcomes of other tests conducted either previously or simultaneously. To minimize the number of tests required to identify the defectives, it is sufficient to consider only reasonable algorithms as otherwise the algorithm would be sub-optimal with respect to this criteria. However, it is not necessary to restrict use to only reasonable algorithms as there many be me practical advantageous to the fault handling process when more general techniques are used. This is especially the case when FPGAs must be

supported on long missions without reducing availability due to the need to execute additional tests.

CGT techniques have been applied to DNA library screening [13] and more recently to hardware fault detection [14]. Efficient algorithms designed for reconfigurable architectures that are capable of solving the fault isolation problem are particularly useful in NASA applications.

#### 1.5. Contributions of this Dissertation

Improving the fault tolerance of reconfigurable devices is a fundamental issue to be considered while using such devices in failure-prone environments. This dissertation develops a strategy for the integration of multiple phases of the fault handling process for reconfigurable devices. While traditional approaches to these problems rely on unique instances of dedicated hardware elements, this dissertation investigates a new technique based on *iterative pairwise comparison* and *functional regeneration*. Under the proposed approach, an initial population consisting of a set of functionally identical (same input-output behavior), yet physically distinct (alternative design or place-and-route realizations) FPGA configurations are produced at design time. The performance of these configurations is evaluated by comparing them in pairs. The result of the pairwise comparisons are then utilized to realize a fault location strategy. The fault location information obtained can then be used to guide the hardware regeneration process. Evolutionary repair techniques inspired by *Genetic Algorithms (GAs)* are used to realize the repair. The methods presented here provide, for the first time, a fault isolation

strategy that works in conjunction with an evolutionary refurbishment mechanism. Significantly, the group testing-based isolation strategy presented here does not require the device to be taken completely offline, or for the resources to be tested exhaustively. This dissertation provides an example of how fault isolation can be achieved while maintaining the system's availability as measured by its goodput.

The competitive evolutionary method presented here leverages information contained in a population of alternatives to enable the refurbishment of faulty configurations. In the context that functional elements are groupings of the underlying physical resources, this research proposes utilization of *Combinatorial Group Testing (CGT)* methods to analyze the expected performance. A comprehensive toolkit for injecting stuck-at faults in FPGA logic for the purpose of evaluating group testing algorithms is developed. This is used to demonstrate the efficiency of CGT techniques in fault isolation. CGT methods are used to develop algorithms for isolating faults using the minimal number of pairings to establish optimality bounds. Further, analytical equation which describe the bounds of the system are derived.

### CHAPTER 2: PREVIOUS WORK

Fault tolerance techniques include both Fault Avoidance and Fault Handling approaches. *Fault Avoidance* strives to prevent malfunctions from occurring. This approach increases the probability that the system is functioning correctly throughout its operational life, thereby increasing the system's *reliability*. Implementing Fault Avoidance tactics such as increasing radiation shielding can protect a system from Single Event Effects. If those methods fail, however, *Fault Handling* methodologies can respond to or recover lost functionality. Whereas some fault handling schemes maintain system operation, some fault handling schemes require removing the system offline to recover from a fault, thereby decreasing the system's *availability*. This limited decrease in availability, however, can increase overall reliability.

Hardware failures in FPGA occur variously due to device degradation over age, or due to environmental factors. Ionization, electromigration, hot carrier effects, and other device degenerative effects may cause device faults in the FPGAs used by such applications. In all of the above scenarios, these devices are mandated to operate reliably for long mission durations with limited or absent capabilities for diagnosis/replacement and little onboard capacity for spares. Specifically, when in a space environment, FPGAs are subject to the effects of high-energy particles or radiation. Cosmic rays and high-energy protons can cause malfunctions to occur in systems located on FPGAs. These malfunctions may be a result of Single-Event Latch-ups (SELs) or Single-Event Upsets (SEUs). SEUs are transient in nature, inverting bits stored in memory cells or registers, whereas SELs may be permanent by inducing high operating current into sensitive devices. While all FPGAs containing memory cells or registers are vulnerable to SEUs, anti-fuse FPGAs are particularly resilient since they do not depend upon SRAM cells to store its configuration. Reconfigurable FPGAs, on the other hand, store its configuration in SRAM cells, which increases the risk to SEUs. Over the years, designers have developed methods for SRAM FPGAs to allow reconfigurability in space applications while mitigated the risk of SEUs.

Radiation-hard SRAM FPGAs have fulfilled the rising demand for FPGAs in space applications. Before their availability, designers of satellites and rovers had no serious alternative to the one-time programmable anti-fuse FPGA. If the inherent fault handling capability of anti-fuse FPGAs was not sufficient, designers were restricted to employing Design-time Redundancy methods. Due to the reconfigurable nature of SRAM FPGAs, radiation-hard SRAM FPGAs have allowed designers to consider other fault handling methods- namely Run-time Fault Handling methods.

#### 2.1. Taxonomy and Nomenclature of FPGA Fault Tolerance Techniques

Figure 1.1 primarily divides Fault Handling approaches into two categories based on its method of implementation [15]. *Architecture-based* fault recovery techniques [16] address faults at the level of the device, allowing manufacturers to increase the production yield of their FPGAs. These techniques typically require modifications to the current FPGA architectures that end-users cannot perform. Once the manufacturer modifies the architecture for the consumer, the device can tolerate faults from the manufacturing process or faults occurring during the life of the device. Concealing the

fault through the underlying fabric of the FPGA is advantageous; users need not know of the occurring hardware faults. Despite making faults transparent to the user, the ability of these methods to tolerate faults is limited in both type and number.

Figure 2.1: Classification of FPGA Fault Handling Methods

*Configuration-based* methods, however, depend upon the end-user for implementation. These higher-level approaches use the configuration bitstream of the FPGA to integrate redundancy with a user's application. By viewing the FPGA as an array of abstract resources, these techniques may select certain resources for implementation, such as those exhibiting fault-free behavior. Whereas Architecture-based methods typically attempt to address all faults, Configuration-based techniques may consider the functionality of the circuit to discern between dormant faults and those manifested in the output. This higher-level approach can determine whether Fault Recovery should occur immediately or at a more convenient time. Figure 2.1 further separates Configuration-based Fault Handling methods into two categories based on whether an FPGA's configuration will change at run-time. *Design-time Redundancy* methods embed processes into the user's application that mask faults from the system output. These methods are quick to respond and recover from faults due to the explicit redundancy inherent to the processes. This speed, however, does come at the cost of increased resource usage and power. Even when a system operates without any faults, the overhead for redundancy is continuously present.

In addition to this constant overhead, these methods are not able to change the configuration of the FPGA. A fixed configuration limits the reliability of a system throughout its operational life. For example, a Design-time redundancy method may tolerate one fault and not return to its original redundancy index. This reduced reliability increases the chance of a second fault causing a system malfunction.

Figure 2.2: Overview of Run-time Fault Handling Methods

*Run-time Fault Handling* methods strive to increase reliability and *Sustainability* by modifying the configuration of the FPGA to adapt to faults. This allows a system to

remove accumulated SEUs and avoid permanently faulty resources to reclaim its lost functionality. In addition, Run-time schemes can transform faulty resources into constructive components by incorporating stuck-at faulty behavior into the circuit's functionality. External processors, which cost additional space, typically determine how to recover from the fault. These methods also require additional time either to reconfigure the FPGA or to generate the new configuration.

Within Run-time Fault Handling, Figure 2.2 illustrates two classes: *Static* and *Dynamic* methods. Of these, Dynamic fault handling methods are the primary focus of this work. Section 2.2 describes and compares the existing Static Run-time techniques and Section 2.3 addresses the Dynamic Run-time approaches in relation to the concepts used in this work.

#### 2.2. Static Run-time Fault Handling Methods

Static methods may recover from a fault utilizing design-time compiled *spare configurations* or re-mapping and rerouting techniques utilizing *spare resources*. The resource allocation and/or pre-designed configurations are independent of the location an nature of faults detected during run-time. These methods take advantage of the regularity of the FPGA's architecture to implement redundancy structures or for designing alternate configurations. Spare configuration methods must provide sufficient configurations and require storage space overhead for these, whereas spare resource methods must allocate sufficient resources to facilitate a repair.

Spare Configuration-based approaches rely on a population of alternate configurations that each use a different set of logical resources to respond to faults. These can be created either at design-time, or at runtime, after the fault has occurred. The precompiled configuration based technique [17] creates alternative configurations at design time that use different equivalent columns of FPGA resources. In their non-overlapping scheme, which has the least resource overhead, a total of C(k+m, m) = (k+m)! / (m!k!)configurations are required to tolerate faults in m columns, where k is the number of columns in the base configuration. The required design-time effort for this approach is high, as it requires manual modification of the design to fit into column sets. Also, the number of horizontal routes available to the designer is reduced by the resources consumed by the approach. The fitness-based and population-based evolutionary hardware approaches for Field Programmable Transistor Arrays (FPTAs) proposed by Keymeulen et al. [18] creates alternative configurations for anticipated faults and at runtime for observed faults respectively. This method provides good resource coverage and passive runtime operation, however system uptime is impacted severely by failure occurrence. Also, additional external computational capacity is required to implement the genetic algorithm that creates the population-based solution at runtime.

*Spare Resource*-based methods such as the one proposed by lach et al [19] rely on the availability of standby resources of varying granularity to address faults. Lach's deterministic approach provided redundant resources at design time. This approach segments the FPGA into static tiles at design time with a known functionality, some

redundant resources, and a pre-designed alternate configuration. Spare tiles can be selected when needed, but their functionality is predetermined and thus limited. Dutt et al<sup>[20]</sup> provide an incremental re-routing method for increased flexibility to tolerate fault on-the-fly. In this method, the FPGA is initially routed without any extra interconnects for reconfiguration. The technique relies on node-covering in which reconfiguration is achieved by constructing replacement chains of cells from faulty cells to spare or unused cells. Using a cost-directed depth-first search strategy, they minimize the overheads involved in rerouting interconnects when responding to faults. Other innovative methods to tolerate faults using spare resources include Lakamraju and Tessier's[21] intra-cluster The authors approach fault tolerance for cluster-based FPGA which group repair. multiple LUT/FF pairs together in clusters. Their method that takes advantage of logical redundancy in such clusters by replacing fault LUT inputs and logic resources unused in the original design mapping by defining methods for LUT Input Exchange and Basic Logic Element exchange. All these re-routing strategies that involve spare resources require the device to be offline, and the support of an external system to complete the rerouting procedure.

#### 2.3. Dynamic Run-time Fault Handling Methods

Dynamic methods aim to allocate spare resources or otherwise modify the configuration during run-time after detecting the fault. Whereas these approaches offer the flexibility of adapting to emergent fault scenarios, additional time is necessary to generate appropriate configurations to repair the specific faults. *Offline* recovery methods require

the FPGA's removal from operational status to complete the refurbishment. *Online* recovery methods endeavor to maintain some degree of data throughput during the fault recovery operation, increasing the system's availability.

#### 2.3.1. Offline Recovery Methods

### 2.3.1.1. Genetic Algorithm Repair

Genetic Algorithms (GA) are inspired by evolutionary behavior of biological systems to produce solutions to computational problems [Mitchell 1998]. Suitable for complex search spaces, GAs have proven valuable in a wide range of multimodal or discontinuous optimization problems. Previous research has investigated the capability of GAs to design digital circuits [Miller et al. 1997] and repair them upon a fault [Keymuelen et al., 2000]. Vigander [2001] proposes the use of GAs to repair faulty FPGA circuits. As a proof of concept, Vigander implements extrinsic evolution, utilizing a simulated feedforward model of the FPGA device with genetic chromosomes representing logic and interconnect configurations.

The evolution process begins with initializing a population of candidate solutions. These initial solutions contain different physical implementations of the same functional circuit. In the midst of a fault, the performance of each configuration is evaluated, revealing which configurations are most affected by the fault. If none of the available configurations provides the desired functionality, then genetic operators create a new population of diverse candidate solutions from the previous configurations. Those previous configurations having a higher performance rating are more likely to be selected and combine with other configurations by the *Crossover* genetic operator. Additionally, the *Mutation* genetic operator injects random variations in the newly created candidate solutions. Vigander also makes use of a *Cell Swap* operator that allows the functionality and connectivity of a faulty cell to swap with a spare cell. The GA evaluates the newly created solutions and replaces poorer performers in the old population with better performers in the current population to create a new generation of candidate solutions. This evolutionary process repeats, stopping when an optimal solution is discovered or after a specific number of generations.

Garvie et al.'s method [22] tolerates permanent faults using jiggling. Jiggling involves repairing a faulty configuration by using an evolutionary algorithm that uses the other two healthy modules and fitness feedback from the TMR voting element. Vigander's, Garvie's and other *n*-plex *spatial voting* approaches [23] deliver real-time fault resolution, but increase power consumption and area requirement *n*-fold during fault-free operation. Previously, these evolutionary approaches have only been simulated using hypothetical device models. They did not attempt application to *Commercial Off The Shelf (COTS)* FPGAs and development tools.

### 2.3.1.2. Augmented Genetic Algorithm Repair

To decrease the amount of time required to generate a repair, Oreifej et al. [24] augment Vigander's Genetic Algorithm fault handling concept with a Combinatorial Group Testing (CGT) fault isolation technique. Group Testing partitions suspect resources into groups and coordinates those groups into a minimal number of tests to isolate the faulty resource. If a group manifests a fault within one of these tests, then the group is known to contain the faulty resource and thus the resources within the group are classified as suspect. In a deterministic manner, the suspect resources are partitioned into iteratively smaller groups and tested until the faulty resource is isolated.

A population within a GA contains various configurations, each of which categorizes the FPGA resources into two groups: utilized and unutilized resources. CGT evaluates each configuration for correct functionality. If a configuration manifests a faulty output, then the resources used by that configuration are considered suspect. Since the various configurations within the population form groups that overlap particular resources, CGT tests multiple configurations and accumulates the number of times each resource is considered suspect through a History Matrix. Configurations are rotated through the FPGA and tested until one element becomes the maximum value within the matrix, isolating the fault to one resource. The GA, in turn, uses the fault location information to avoid faulty resources while evolving a repaired configuration.

### 2.3.1.3. Incremental Rerouting Algorithms

The Node-Covering method discussed in Section 2.2 avoids a fault by rerouting a circuit into design-time allocated spares using design-time reserved wire segments. Dutt et al. [1999] expand this method by dynamically allocating reserved wire segments during run-

time instead of design-time. Run-time reserved wire segments allow the method to utilize unused resources in addition to the spares allocated during design-time.

Emmert and Bhatia [25] present a similar Incremental Rerouting approach that does not require design-time allocated spare resources. The fault recovery method assumes an FPGA to contain resources not utilized by the application, thus exploiting unused faultfree resources to replace faulty resources. Upon detecting and diagnosing a logic or interconnection fault by some other detection method, Incremental Rerouting calculates the new logic netlist to avoid the faulty resource. The method reads the configuration memory to determine the current netlist and implements the incremental changes through partial reconfiguration.

Since faulty cells may not be adjacent to a spare resource, a string of cells is created logically, starting with the faulty cell and ending with the logic cell adjacent to the spare resource. To avoid the fault, the string of cells shifts away from the faulty resource and towards the spare resource. In the case of Node-covering, every row has a spare resource so the string of cells within the row simply shifts to the right, leaving the faulty resource unused. Since this method does not allocate a spare resource for every row, the string of cells may extend into multiple rows to reach a spare cell.

Re-placing cells requires the wire segments of the moving logic cells to be rerouted. The configuration memory of the FPGA is read to determine which nets are affected by the re-placed logic cells. All faulty nets and those that solely connect the moved logic cells are ripped-up [25] while those that connect other unmoved logic cells remain unchanged.

A greedy algorithm then incrementally reroutes each of the dual-terminal nets to reestablish the application's original functionality. Initially, the algorithm only uses spare interconnection resources within the direct routing path, but may expand its scope to encompass wider routing paths for unroutable nets.

## 2.3.2. Online Recovery Methods

## 2.3.2.1. TMR with Single-Module Repair

Since Triple Modular Redundancy (TMR) performs the majority vote of three modules, the voted output remains correct even if a single module is defective. Exploiting this concept allows a system to remain online with two viable modules while a defective module undergoes repair. Methods presented by Ross and Hall [26], Shanthi et al. [27], and Garvie and Thompson [22] repair the defective module through genetic algorithms.

At design-time, Ross and Hall [26] produce a population of diverse configurations for implementation. At run-time, three of these configurations are implemented into the circuit and monitored for discrepancies. Agreeing outputs indicate that the modules are functioning correctly whereas discrepancies indicate defective resources utilized by one of the configurations. A mutation genetic operator is applied to defective modules and the fitness of the new individual is evaluated. The process repeats until the fault is occluded.

In addition to the strategy above, Shanthi et al. [27] utilize a deterministic approach in identifying faulty resources. By monitoring the resources within each configuration, resources utilized by viable modules gain confidence whereas resources utilized by faulty modules gain suspicion. This information allows fault handling by implementing configurations not using defective resources. Additionally, differing configurations can be rotated to reveal dormant faults in unused resources.

Instead of selecting from a diverse population, Garvie and Thompson [22] implement three identical modules. The commonality between configurations permits a *Lazy Scrubbing* technique, which considers the majority vote of the three configurations as the original configuration when scrubbing a faulty module. Of course, Lazy Scrubbing only applies when a genetic algorithm has not modified the original configurations to tolerate a permanent fault.

To address permanent faults, a (1+1) Evolutionary Strategy provides a minimal genetic algorithm, which produces one genetically modified offspring from one parent and chooses the most fit between the two. To mitigate the possibility for a misevaluated offspring replacing a superior parent, a History Window of past mutations is retained to enable rollback to the superior individual. Normal FPGA operational inputs provide the test vectors to evaluate the fitness of newly formed individuals. To determine correct values, an individual's output is compared to the output of the voter. An individual's fitness evaluation is complete when it has received all possible input combinations.

#### 2.3.2.2. Online Built-in Self Test

Emmert et al. [28] present an approach that pseudo-exhaustively tests, diagnoses, and reconfigures resources of the FPGA to restore lost functionality due to permanent faults. The application logic handles transient faults through a concurrent error-detection technique and by periodically saving and restoring the system's state through checkpointing. As shown in [28], this method partitions the FPGA into an Operational Area and a *Self-Testing ARea* (STAR), consisting of a Horizontal STAR and a Vertical STAR. Such an organization allows normal functionality to occur within the Operational Area while *Built-In Self Tests* (BISTs) and fault diagnosis occurs within the STARs. Whereas other BIST methods may utilize external testing resources assumed fault-free, the resources-under-test also implement the Test-Pattern Generator (TPG) and the Output Response Analyzer (ORA).

To provide fault coverage of the entire FPGA, the STARs incrementally rove across the FPGA, each time exchanging its tested resources for the adjacent, untested resources in the Operational Area. The H-STAR roves top to bottom then bottom to top while the V-STAR roves left to right then right to left. Whereas one STAR could test and diagnose programmable logic blocks (PLBs), two STARs are required to test and diagnose programmable interconnect, the H-STAR for horizontal routing resources and the V-STAR for vertical routing resources. Where they intersect, the two STARs may concurrently test both horizontal and vertical routing resources and the connections between them. Since faults have equal probability to occur within used resources with unused resources, Roving STARs provides testing for all resources. Uncovering dormant

faults in unused resources prevents them from being allocated as spares to replace faulty operational resources.

In addition to facilitating testing, diagnosis, and reconfigurations, a *Test and Reconfiguration Controller* (TREC) is responsible for roving the STARs across the FPGA. The TREC is implemented as an embedded or external microprocessor that communicates to the FPGA through the Boundary-Scan interface. All possible configurations of the STARs are processed during design-time and stored by the TREC for partial reconfiguration during run-time. Relocating the STARs through partial reconfiguration only affects the logic and routing resources within the STAR's current and new locations. When a STAR's next location includes sequential logic, the TREC pauses the system clock until the logic is completely relocated. In addition to pausing the system clock, the TREC implements an Adaptable System Clock where the clock speed is adjusted to account for timing delays arising from new configurations that adapt to faults.

Roving STARs supports a three-level strategy to handling permanent faults. In the first level, a STAR detects a fault and remains in the same position to cover the fault. Since a STAR contains only offline logic and routing resources, testing and diagnosing time is not at a premium; the application continues to operate normally while the TREC tests and diagnoses the fault. After diagnosing the fault, the TREC determines if the fault will affect the functionality that will soon occupy the faulty resources upon moving the STAR. If the fault will not affect the new configuration's functionality, such as only affecting resources that will be unused or spare, then the application's output will not

articulate the fault and no action is required. If the fault will affect the new configuration's functionality, then the TREC generates a *Fault-Bypassing Roving Configuration* (FABRIC) to reroute incrementally the new configuration so that the fault will not affect its functionality. Whereas some FABRICs may be compiled during design-time, most fault scenarios will dictate compiling them online while the STAR covers the fault. While one STAR covers a fault for testing and diagnosis, the second STAR, however, may continue roving the FPGA searching for faults in its respective routing resources and PLBs. The second level strategy then applies the FABRIC that either was compiled during design-time or was generated during the first-level strategy. Replacing a faulty resource with a spare one through a FABRIC thus releases the STAR covering the fault to continue roving the FPGA.

If the fault affects functionality and no spare resources are available to bypass the fault, then the third strategy is invoked. As a last resort, the TREC has an option to perform *STAR Stealing*, which reallocates resources from a STAR to the Operational Area to bypass the fault. Removing resources from a STAR immobilizes it from roving the FPGA. Whereas the second STAR can test all PLBs in an FPGA with an immobile STAR, only half of the routing resources can be tested. In some situations however, a mobile STAR may intersect and forfeit its resources to an immobile STAR, which releases the other STAR to rove the FPGA and test the remaining routing resources.

As previously stated, testing and diagnosis occurs within a STAR. Utilizing the resources of the STAR through partial reconfiguration, the TREC configures a TPG, an ORA, and either two Blocks Under Test (BUT) for a PLB test or two Wires Under Test

(WUT) for an interconnect test. Since no resource may be assumed to be fault-free, the TPG, BUTs/WUTs, and ORA are rotated through common resources of the STAR. The TREC maintains the results for all test configurations so that the common faulty resources can be identified between the two parallel BUTs or WUTs and the rotation of resources.

#### 2.3.2.3. Consensus-based Evaluation of Competing Configurations

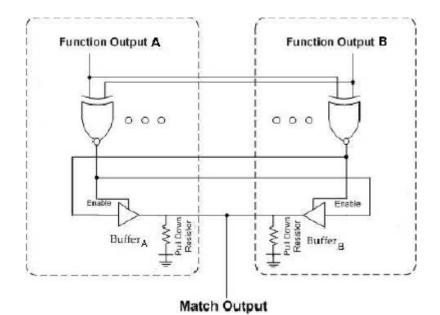

Whereas previous Online Genetic Algorithm-based methods utilize an N-MR voting element, the Competitive Runtime Reconfiguration (CRR) approach presented here handles faults through a pairwise functional output comparison. Similar to previous GA methods, each of the two individuals is a unique configuration on the target FPGA exhibiting the desired functionality. CRR divides the FPGA into two mutually exclusive regions, allocating all Left-Half configurations to one region and Right-Half configurations to the other region. Together, these configurations comprise the population of competing alternatives. The detection method realizes a traditional Concurrent Error Detection (CED) arrangement that allocates mutually exclusive resources for each individual, which detects any single resource fault. The comparison can result in either a discrepancy or a match between left-half and right-half configuration outputs, when resource faults are *articulated* by the configurations that utilize the faulty resources. Such discrepancies indicate the presence of FPGA resource faults in either the resources used to constitute the combinational logic module or a pipeline stage consisting of combinational logic.

### 2.4. Fault Detection and Location using Exhaustive Testing Techniques

Several approaches to GA-based fault handling in FPGAs utilize exhaustive testing for fault isolation and offline regeneration mechanisms. In addition to TMR, Table 2.1 also lists characteristics of fault-handling schemes that consider reconfigurability. TMR, Vigander's, and other n-plex spatial voting approaches deliver real-time fault resolution, but increase power consumption *n*-fold during fault-free operation. STARS [29] is an example of a resource-oriented diagnostic method that performs Built-in Self-Tests (BISTs) on sub-sections of the FPGA. STARS extends the concept of using exhaustive testing by exploiting reconfigurability to occlude faults in the circuits. Under this paradigm, the test area roves across all FPGA resources. Portions of the FPGA are continually taken offline in succession for testing while the functionality is moved to a new location within the reprogrammable fabric. The device, however, remains operational and hence online. One limitation is that detection latency can be large since tests must sweep through all intervening resources before a fault is detected. Potential throughput unavailability due to diagnostic reconfigurations when no faults have yet occurred is also a consideration. However, STARS is a successful example of a method that uses exhaustive online testing to realize regeneration. Methods proposed by Lohn [1] and Lach [19] either rely on offline regeneration supported by exhaustive functional testing, or pre-determined spares defined at design-time.

|                                                   |                                                                                  | Fault Detection                                 |                                               | Resource Coverage |                   |            | Fault Isolation                                             |  |

|---------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------|-------------------|-------------------|------------|-------------------------------------------------------------|--|

| Approach                                          | Fault Handling Method                                                            | Latency                                         | Distinguish<br>Transients                     | Logic             | Inter-<br>connect | Comparator | Granularity                                                 |  |

| TMR                                               | Spatial voting                                                                   | Negligible                                      | No                                            | Yes               | Yes               | No         | Voting element                                              |  |

| Vigander [30]                                     | Spatial voting & offline evolutionary regeneration                               | Negligible                                      | No                                            | Yes               | No                | No         | Voting element                                              |  |

| Lohn et al. [1] Offline evolutionary regeneration |                                                                                  | Negligible                                      | No                                            | Yes               | Yes               | No         | Unnecessary                                                 |  |

| Lach et al. [19]                                  | Static-capability tile<br>reconfiguration                                        | Relies on independent fault detection mechanism |                                               |                   |                   |            |                                                             |  |

| STARs [29] Online BIST                            |                                                                                  | Up to 8.5M erroneous outputs                    | Test pattern<br>transients                    | Yes               | Yes               | No         | LUT function                                                |  |

| Keymeulen[18]                                     | Population-based fault<br>insensitive design                                     | Design-time<br>prevention emphasis              | No                                            | Yes               | Yes               | No         | Not addressed<br>at runtime                                 |  |

| CRR                                               | Competitive runtime input<br>fitness evaluation and<br>evolutionary regeneration | Negligible                                      | Transients are<br>attenuated<br>automatically | Yes               | Yes               | Yes        | Unnecessary, but<br>can isolate<br>functional<br>components |  |

Table 2.1: Characteristics of Related FPGA Fault-Handling Schemes

Of the methods in Table I, only Keymeulen, Stoica, and Zebulum [18] investigate the possibility of using a population-based approach to desensitize circuits to faults. They develop evolutionary techniques so that a circuit is initially designed to remain functional even in presence of various faults. Their population-based fault tolerant design method evolves diverse circuits and then selects the most fault-insensitive individual. In this paper we propose a system that achieves improved fault tolerance by using a runtime adaptive algorithm that emphasizes the utilization of responses observed during the actual operation of the device. While their population-based fault tolerance approach provides passive runtime tolerance, CRR is dynamic and actively improves the fault tolerance of the system according to environmental demands.

### 2.5. Forming a Robust Consensus from Diversity

An evolutionary process that uses absolute fitness measures and exhaustive tests may not be able to provide adaptive fault tolerance. Layzell and Thompson [31] dealt with these aspects in terms of *Populational Fault Tolerance (PFT)* as an inherent quality of evolvable hardware. Under PFT, the creation of the best-fit individual proceeds by incrementally incorporating additional elements into partially-correct prototypes to adapt to faults. They speculate that PFT is less likely to occur for online evolution in dynamic environments. Nonetheless, evaluation becomes focused on the precise regions of relevance within the search space during the execution of online processes. This provides a powerful motivation to explore CBE.

Yao and Liu [32] emphasize that in evolutionary systems the population contains more information than any one individual. They demonstrate the utility of information contained within the population using case studies from the domains of artificial neural networks and rule based systems. In both cases, the final collection of individuals outperforms any single individual. The work in [33] further extends this concept by presenting four methods for combining the different individuals in the final population to generate system outputs. They provide similar results for three data sets, namely the Australian credit card assessment problem, the heart disease problem, and the diabetes problem. While the authors devise a method to utilize the information contained in the population to improve the final solution, they fail to use the information in the population to improve the learning and optimization process itself. The proposed CBE approach indicates that refurbishment problems can benefit from population information.

More recently, in [34] the authors describe using fitness sharing and negative correlation to create a diverse population of solutions. A combined solution is then obtained using a gating algorithm that ensures the best response to the observed stimuli. In evolvable hardware, it may not always be possible to combine solutions without additional physical resources that may also be fault-prone. In our approach, all individuals in the population are recognized as possible solutions, with the best emerging candidate being selected based on its runtime performance record. The authors also claim that applying the described techniques to evolvable hardware applications should be straightforward, but do not provide examples. They state the absence of an optimal way of predicting the future performance of evolved circuits in unforeseen environments as an impediment. Chapter 3 details how an adaptive system can keep track of the relative performances of individuals and implicitly build a consensus.

### 2.6. Improving Reliability using Autonomous Group Testing

In state-of-the-art Xilinx SRAM-based FPGAs, the device configuration can be modified without interrupting the normal operation of the device. For space applications, it is typical to perform such configuration scrubbing periodically to repair any configuration errors due to Single Event Upsets (SEUs) [35]. The Xilinx TMR tool software [36] can be used to not only triplicate the user's design, but also insert logic to repair transient user memory errors and upsets due to SEUs. TMR can be combined with the scrubbing method to have a reliable system while preventing soft errors. However, configuration scrubbing only refreshes a single complete configuration and therefore cannot be used to

address permanent faults [37]. While an *n*-modular redundancy scheme such as TMR ensures validated correct output, the proposed AGT-based technique can minimize the risk of having two faulty modules. The comparators of the Xilinx TMR tools can be used to detect the discrepancy among the redundant modules. Discrepancies reported by the comparators can be used to target all resources used by a faulty module. Once the faulty module is identified, the GT-based algorithm can localize the fault to a logic slice. Autonomous group testing aims to avoid system failure by providing methods to isolate permanent faults and maintain a healthy population of configurations for each redundant module.

# CHAPTER 3: COMPETITIVE RUNTIME RECONFIGURATION FAULT HANDLING PARADIGM

While the fault repair capability of *Evolvable Hardware (EH)* approaches have been previously demonstrated, further improvements to fault handling capability can be achieved by exploiting population diversity during all phases of the fault handling process. In existing fault-handling methods for reconfigurable hardware, fault-tolerance is evolved at design time, or achieved at repair-time using evolution after taking a detected failed unit offline. In both cases, GAs provided a population-based optimization algorithm with the objective of producing a single best-fit individual as the final product. They rely on a pre-determined static fitness function that does not consider an individual's utility relative to the rest of the population. The evaluation mechanisms used in previous approaches depend on the application of exhaustive test vectors to determine the individual with the best response to all possible inputs.

However, given that partially complete repairs are often the best attainable [1], [30], other individuals may outperform the best-fit individual over the range of inputs of interest. In particular, there is no guarantee that the individual with the best absolute fitness measure for an exhaustive set of test inputs will correspond to the individual within the population that has the best performance among individuals under the subset of inputs actually applied. Thus, exhaustive evaluation of regenerated alternatives is computationally expensive, yet not necessarily indicative of the optimal performing individual among a

population of partially correct repairs. Hence, two innovations are developed herein for sustainable EH regeneration:

## 1. Elimination of additional test vectors, and

2. Temporal Assessment based on aging and outlier identification

In CRR, an initial population of functionally identical (same input-output behavior), yet physically distinct (alternative design or place-and-route realization) FPGA configurations is produced at design time. During runtime, these individuals compete for selection based on discrepancy favoring fault-free behavior. Discrepant behavior, where the outputs of two competing individuals do not agree on a bit-by-bit basis, is used as the basis for the performance evaluation process. Any operationally visible fault will decrease the fitness of just those configurations that use it. Over a period of time, as the result of successive comparisons, a consensus emerges from the population regarding the relative fitness of all individuals. This allows the classification of configurations into ranges of relative reliabilities based on their observed performance during online operation.

## 3.1. Detecting Faults using a Population of Alternatives

In order to provide fault coverage for the voting element, a distributed discrepancy detector circuit may be used, as described in Section 4.3. Each individual in the population has an instance of one of the two complementary halves of the discrepancy detector circuit. When two competing L and R half-configurations are loaded on the

FPGA, the discrepancy detector circuit is completed. The design of the discrepancy detector accounts for the possibility of error in either, or both of the complementary halves of the detector. Such an error would reflect on the performance of the half-configurations that instantiated the detector hence degrading any preference for selection of those individuals as described below.

Figure 3.1: Physical Arrangement with Two Competing Configurations

#### 3.2. Assessing Individual Fitness and Managing Fitness States

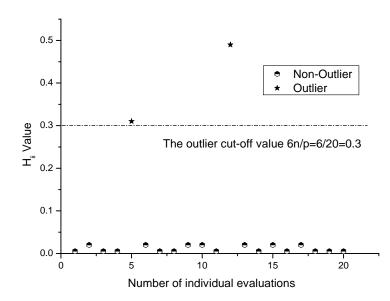

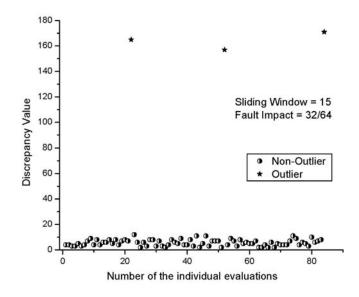

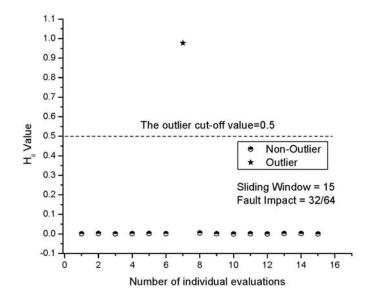

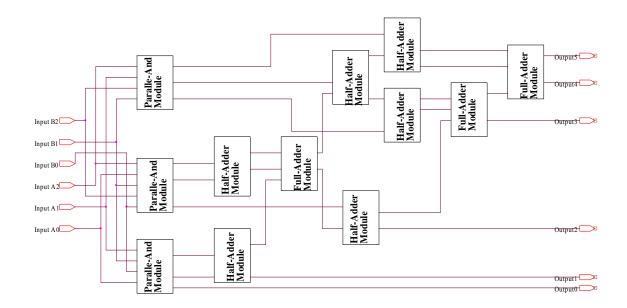

Instead of using an absolute fitness function with exhaustive testing, outlier identification can be achieved using techniques such as the *hat matrix* [38], *H*, where the diagonal elements  $H_{ii}$  are used to identify the threshold to isolate faulty individuals as outliers. The threshold value is determined by an analysis of the diagonal elements  $H_{ii}$  of the hat matrix generated from population statistics accumulated over an evaluation window. The relative reliability of an individual is indicated by its instantaneous fitness state. Through run-time competition, and the concomitant fitness state assignment, a fault becomes occluded from the visibility of subsequent FPGA operations.