# CASCADED DIGITAL REFINEMENT FOR INTRINSIC EVOLVABLE HARDWARE

by

# VIGNESH THANGAVEL B.E. (Hons.) Birla Institute of Technology and Science, Pilani, 2013

# A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Spring Term 2015

Major Professor: Ronald F. DeMara

© 2015 Vignesh Thangavel

# ABSTRACT

Intrinsic evolution of reconfigurable hardware is sought to solve computational problems using the intrinsic processing behavior of System-on-Chip (SoC) platforms. SoC devices combine capabilities of analog and digital embedded components within a reconfigurable fabric under software control. A new technique is developed for these fabrics that leverages the digital resources' enhanced accuracy and signal refinement capability to improve circuit performance of the analog resources' which are providing low power processing and high computation rates. In particular, Differential Digital Correction (DDC) is developed utilizing an error metric computed from the evolved analog circuit to reconfigure the digital fabric thereby enhancing precision of analog computations. The approach developed herein, Cascaded Digital Refinement (CaDR), explores a multi-level strategy of utilizing DDC for refining intrinsic evolution of analog computational circuits to construct building blocks, known as Constituent Functional Blocks (CFBs). The CFBs are developed in a cascaded sequence followed by digital evolution of higherlevel control of these CFBs to build the final solution for the larger circuit at-hand. One such platform, Cypress PSoC-5LP was utilized to realize solutions to ordinary differential equations by first evolving various powers of the independent variable followed by that of their combinations to emulate mathematical series-based solutions for the desired range of values. This is shown to enhance accuracy and precision while incurring lower computational energy and time overheads. The fitness function for each CFB being evolved is different from the fitness function that is defined for the overall problem.

I dedicate this work to my family who constantly supported me and believed in me even in the face of complete loss of hope of further progress, only to steer me to turn it around to what it is now. I also dedicate this work to my advisor and guru, Dr. Ronald F. DeMara for being patient and tolerant of my quirks, for giving the right push time and again, streamlining the occasional eccentricity into worthwhile products and for imbibing in me a spirit of professionalism for life! I also dedicate this work to my best friends, Hariharan Ramakrishnan and Arvind Ranganathan for providing constant motivation and to help me take it easy just as much as I needed both.

# ACKNOWLEDGMENTS

I would like to express my deepest gratitude and sincere thanks to my advisor Dr. Ronald F. DeMara, for providing me with extensive guidance, astute insights and tremendous support in every leg of research, without which this thesis would not have been possible. I would like to extend special thanks to Dr. Zixia Song for being in my thesis committee, brainstorming and adding a new mathematically richer perspective to the thesis to help alter its course for the better. I would also like to thank Dr. Kalpathy Sundaram for serving as my thesis committee member and for the constant encouragement to pursue excellence in research. I would like to take this opportunity to thank my research partner Mr. Steven Pyle, for providing brilliant suggestions and brainstorming ideas at crucial moments to ensure successful development of well-motivated research. I would also like to extend my thanks to all members of the UCF Computer Architecture Lab team for their encouragement and support.

# TABLE OF CONTENTS

| LIST OF FIGURES                            | x  |

|--------------------------------------------|----|

| CHAPTER ONE: INTRODUCTION                  | 1  |

| Significance and Context of the Work       | 1  |

| Motivation                                 | 2  |

| Platform and Resources                     |    |

| PSoC's Reconfigurable Digital Fabric       | 4  |

| Contributions of Thesis                    | 5  |

| Organization of Thesis                     | 5  |

| CHAPTER TWO: LITERATURE REVIEW             |    |

| Related Works                              |    |

| Evolutionary Algorithms                    |    |

| CHAPTER THREE: PROGRAMMABLE SYSTEM ON CHIP |    |

| PLD Architecture                           |    |

| Macrocell Architecture                     | 14 |

| Experimental Configuration                 | 14 |

| LUT instantiation and wiring               | 14 |

| Force Directives – Pins                    |    |

| Forcing resource utilization and implementation of LUTs in the PLD space 1 | 6  |

|----------------------------------------------------------------------------|----|

| Constraints in Digital Configuration of 1 PLD:1                            | 9  |

| Number of input terms that can simultaneously enter a PLD 1                | 9  |

| Selection of input lines used by the PLD in implementing the LUT 1         | 9  |

| Storing the configuration:                                                 | 20 |

| Writing back configurations to the chromosomes:                            | 20 |

| Writing back configuration to the corresponding registers:                 | 21 |

| CHAPTER FOUR: DIFFERENTIAL DIGITAL CORRECTION                              | 2  |

| Differential Digital Correction Technique 2                                | 2  |

| Representation Scheme and Chromosome Structure:                            | 23 |

| Active Lines:                                                              | 24 |

| AND array parameters:                                                      | 25 |

| OR array parameters:                                                       | 25 |

| DDC Genetic Algorithm                                                      | 26 |

| Generation of random individuals and the population size:                  | 26 |

| Elitism and selection of individuals for crossover:                        | 27 |

| Crossover:                                                                 | 27 |

| Mutation:                                                                  | 29 |

| Improving performance of the GA and overcoming stasis conditions: | 30 |

|-------------------------------------------------------------------|----|

| PLD allocation and utilization:                                   | 31 |

| Cascaded DDC:                                                     |    |

| CHAPTER FIVE: COEFFICIENT PREDICTION                              |    |

| Coefficient Prediction Technique                                  |    |

| Coefficient Prediction Genetic Representation                     |    |

| Chromosome Structure:                                             |    |

| Coefficient Prediction Genetic Algorithm                          |    |

| CPGA Algorithm Flow                                               |    |

| Range Scaling                                                     |    |

| Generation of random individuals and the population size:         |    |

| Dynamic Range Adaptation:                                         |    |

| Elitism and selection of individuals for crossover:               |    |

| Crossover:                                                        |    |

| Mutation:                                                         |    |

| Improving performance of the GA and overcoming stasis conditions: | 40 |

| Scaling back to original range                                    | 40 |

| CHAPTER SIX: CASCADED DIGITAL REFINEMENT                          | 41 |

| CHAPTER SEVEN: RESULTS                                                     | 47 |

|----------------------------------------------------------------------------|----|

| CHAPTER EIGHT: CONCLUSION AND FUTURE WORKS                                 | 62 |

| Reliable Evolution Control through Periodic BIST Based Fitness Adjustments | 63 |

| APPENDIX A: SAMPLE DDC EVOLUTION CODE                                      | 66 |

| APPENDIX B: SAMPLE CPGA CODE                                               | 84 |

| LIST OF REFERENCES                                                         | 94 |

# LIST OF FIGURES

| Fig      | gure 1: Paradigm of Analog – Digital Computations [35]                                 |

|----------|----------------------------------------------------------------------------------------|

| Fig      | gure 2: Organization of Thesis                                                         |

| Fig      | gure 3: Collection of Related Works [35]                                               |

| Fig      | gure 4: Simplified PSoC PLD Architecture adopted from [6]                              |

| Fig      | gure 5: Schematic showing instantiated resources and connections                       |

| Fig      | gure 6: Design Wide Resources file showing pin assignment15                            |

| Fig      | gure 7: UDB mapping scheme within PSoC build files adopted from [36] 17                |

| Fig      | gure 8: Design Wide Resources file showing force directives for PLD placement 18       |

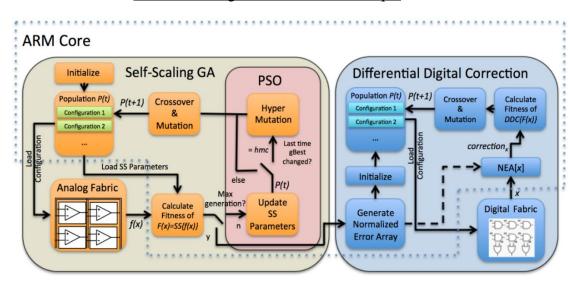

| Fig      | gure 9: DDC and Self-Scling GA schematic for analog-digital evolution [35]             |

| Fig      | gure 10: Example of selection of active lines by IDE for logic implementation. Adopted |

| from [6] |                                                                                        |

| Fig      | gure 11: Chromosome representation for each UDB evolved in DDC                         |

| Fig      | gure 12: Chromosome representation for coefficients evolved in CP                      |

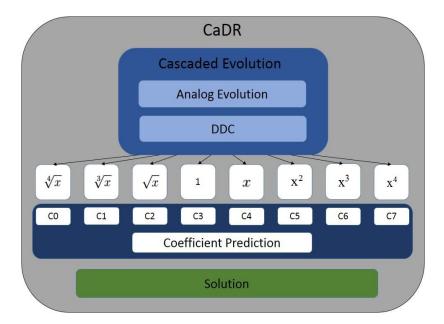

| Fig      | gure 13: CaDR scheme for solving approximating solution function to a DE 41            |

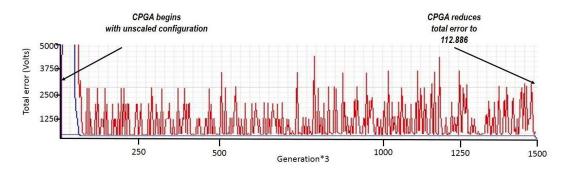

| Fig      | gure 14: Coefficients evolved to approximate fifth power of <i>x</i>                   |

| Fig      | gure 15: Coefficients evolved to approximate fourth power of <i>x</i>                  |

| Fig      | gure 16: Collection of comparative performance of DDC against previous works [35]47    |

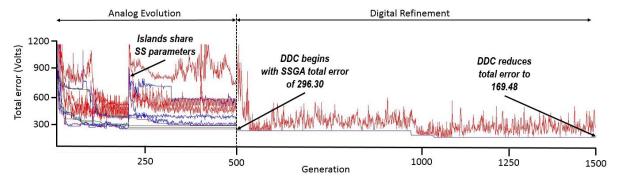

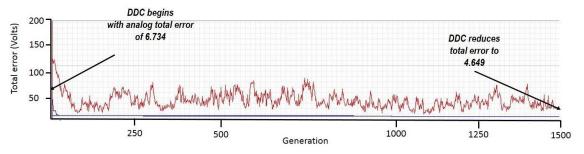

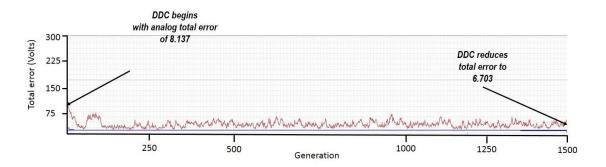

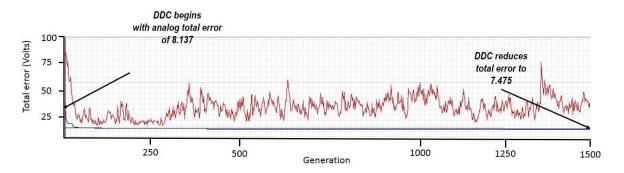

| Fig      | gure 17: Evolution of cube circuit and its refinement using DDC                        |

| Fig      | gure 18: DDC Evolution of Fourth Root circuit without hypermutation                    |

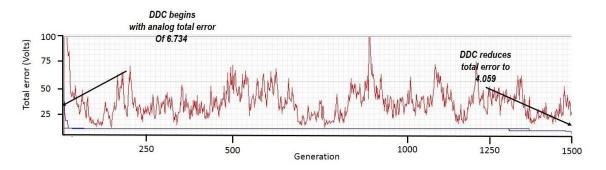

| Figure 19: Best case DDC evolution of Fourth Root circuit with a hypermutation rate of     |

|--------------------------------------------------------------------------------------------|

| 300                                                                                        |

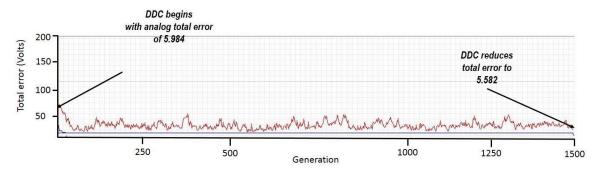

| Figure 20: DDC Evolution of Cube Root circuit without hypermutation                        |

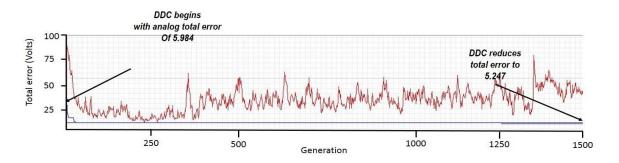

| Figure 21: Best case DDC evolution of Cube Root circuit with a hypermutation rate of       |

| 300                                                                                        |

| Figure 22: DDC Evolution of Square Root circuit without hypermutation                      |

| Figure 23: Best case DDC evolution of Square Root circuit with a hypermutation rate of     |

| 200                                                                                        |

| Figure 24: DDC Evolution of First Power circuit without hypermutation                      |

| Figure 25: DDC Evolution of Square circuit without hypermutation                           |

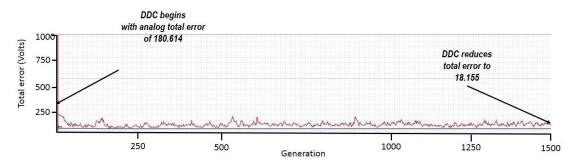

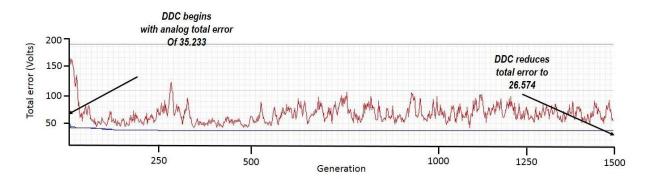

| Figure 26: DDC Evolution of Cube circuit without hypermutation                             |

| Figure 27: DDC evolution of Cube circuit with a hypermutation rate of 200                  |

| Figure 28: DDC Evolution of Fourth Power circuit without hypermutation                     |

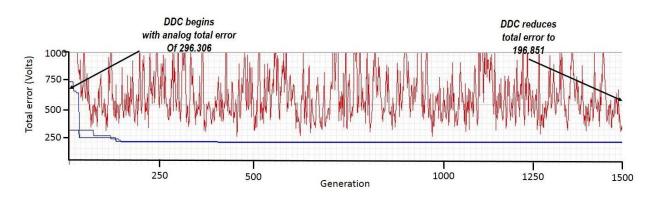

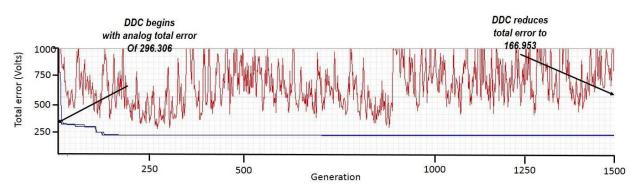

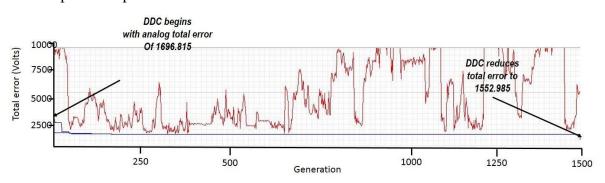

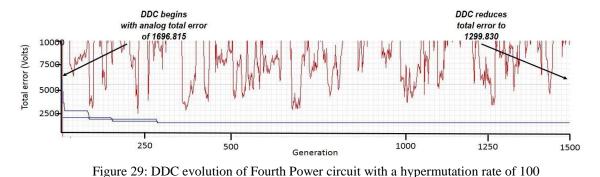

| Figure 29: DDC evolution of Fourth Power circuit with a hypermutation rate of 100 56       |

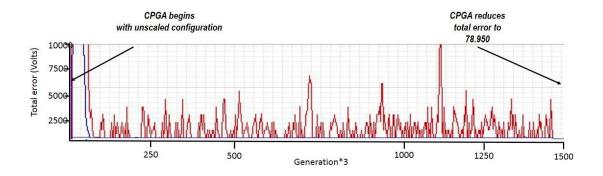

| Figure 30: CPGA evolution of coefficients for $sin(x)$ without range forcing               |

| Figure 31: CPGA evolution of coefficients for $sin(x)$ with range forcing for error<100.58 |

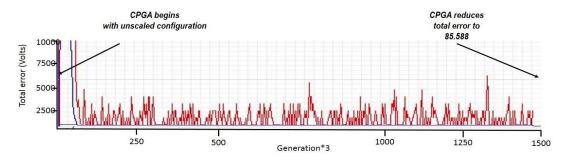

| Figure 32: CPGA evolution of coefficients for $cos(x)$ without range forcing               |

| Figure 33: Coefficients evolved to approximate sine of <i>x</i>                            |

| Figure 34: Coefficients evolved to approximate cosine of <i>x</i>                          |

# **CHAPTER ONE: INTRODUCTION**

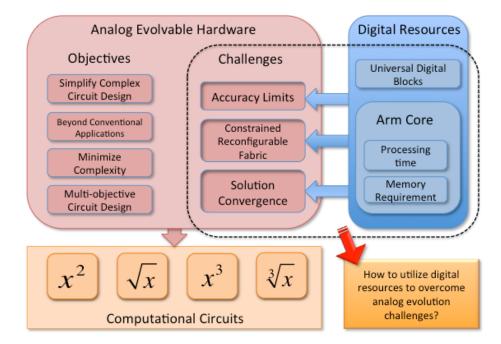

Technology scaling and the criticality of issues like power wall and dark silicon as elaborated in [1] are magnified in pure digital frameworks for computation, thereby compromising the enhancement in computational efficiency otherwise sought and expected. One viable candidate to navigate through this labyrinth of deeply interconnected problems is the emerging field of cooperative analog-digital computations which leverages the complementary benefits of both as demonstrated successfully in the signal processing domain in [2]. Design of analog circuits to perform computations, though attractive, is highly non-trivial and is fraught with issues of scalability and flexibility to perform a wide range of computations with added noise issues. They however handle continuous ranges very cost-effectively and interface well with real world data. Pure digital design on the other hand is very systematic and offers great computational versatility and robustness, but is prohibitively costly and complex to handle continuous data ranges and requires lot of conversions to interface well with real world data.

# Significance and Context of the Work

While analog and digital computations have their own pros and cons, it is distinctly visible that these are complementary as well and can be exploited intelligently if present and available for reconfiguration, ideally on the same platform with complete interconnection of both types of resources. PSoC 5LP is one platform that offers reconfigurable analog and digital fabrics at a low cost for developing low power applications. Though it doesn't offer much interconnection between

every unit of the analog and digital fabrics, respectively, it does offer reconfigurable resources in both domains under the software control of a single embedded ARM Cortex-M3 core. However, due to the limited memory and silicon availability on chip, their reconfigurable use for bigger and complex applications is limited especially by parallelizability of processes. In spite of these limitations, this platform provides an impressive variety of resources considering its cost and ability to emulate general purpose computations.

Figure 1: Paradigm of Analog – Digital Computations [35]

# **Motivation**

Evolutionary algorithms (EAs) are a well-known bio-inspired meta-heuristic to find solutions to complex multi-objective problems especially where the fitness function being evaluated for quality of solutions is multi-modal and a population of good solutions is desired as [3] elaborates. Genetic Algorithm (GA) in particular, are a very popular class of EAs that mimic Darwinian evolution and the process of natural selection to pick candidate solutions from populations of configurations. As [3] explains, GA's implicit parallelism and the uncanny ability of finding building blocks inspire one to think of new ways to solve problems that differ from the tried and tested classical approaches which tend to incur more computational costs in many settings. One main characteristic of solutions developed by GAs is the inherent approximations that make them suitable for the application at hand to the desired degree without compromising on accuracy where necessary. The paradigm of approximate circuit synthesis as outlined in [4], introduces the notion of a very effective practical tool of functional approximation to achieve objectives of lower computational overheads. Also, intrinsic evolution helps exploit device properties beyond simulations and design abstractions and assumptions otherwise used which often face risk of violation in practical circuits as the pioneering work in [5] elaborates. Though [5] predicts limited applications such as signal processing for intrinsic evolution, it could possibly be applied to a broader range of scenarios and inspire better approaches to perform computations. These qualities encouraged the cascaded approach developed herein, which starts by evolving building blocks to the solution at hand with desired levels of tunable accuracies, followed by the process of combining them appropriately, all intrinsically on chip.

## Platform and Resources

To develop techniques for intrinsic evolution of the digital fabric to improve upon the outputs of the analog fabric, a clear understanding of PSoC's capabilities and limitations is necessary. The following section outlines the same for PSoC 5LP System-on-Chip platform.

The major systems interoperating in PSoC 5LP devices are the Digital System, Analog System, Memory System, CPU System, Program/Debug Section, Clocking System, and Power Management System. These systems are equipped with the following features as listed in the PSoC architecture TRM [6]:

- ARM Cortex-M3 CPU with a nested vectored interrupt controller and a high-performance DMA controller

- Several types of memory elements including SRAM, flash, and EEPROM

- System integration features, such as clocking, a feature rich power system, and versatile programmable inputs and outputs

- Digital system that includes configurable universal digital blocks (UDBs) and specific function peripherals, such as CAN and USB

- Analog subsystem that includes configurable switched capacitor (SC) and continuous time (CT) blocks, up to 20-bit Delta Sigma converters, 8-bit DACs that can be configured for 12-bit operation, more than one SAR ADC, comparators, PGAs, and more

- Programming and debug system through JTAG, serial wire debug (SWD), and single wire viewer (SWV)

#### PSoC's Reconfigurable Digital Fabric

PSoC's digital fabric consists of PLDs or programmable logic devices organized in pairs inside the universal digital blocks or UDBs which can all be interconnected with one another in a desired fashion and hence constituting a reconfigurable digital fabric. There are 24 UDBs or 48

PLDs in total. The routing is not easily reconfigurable programmatically, involving too many register writes for each configuration and in the absence of clear documentation or support, routing is practically fixed based on the schematic configuration at boot time by the IDE. In addition to combinational logic, PSoC 5LP also has sequential logic in each UDB consisting of ALU, registers, FIFO and comparators. However, the datapath isn't very flexible to support dynamic reconfiguration and is hence not explored in this work.

# Contributions of Thesis

- A novel refinement technique implemented with a small amount of digital logic and memory to improve the accuracy of computations performed by analog circuits significantly.

- 2. Reducing chromosome lengths and introducing a new paradigm of piecewise evolution in cascaded stages followed by higher level evolution for control of these pieces.

- 3. An exploration in the mathematical decomposition and techniques of approximation of functions using variations of Laurent and Puiseux series to develop newer and better adjustments that can improve accuracy of calculations with available resources significantly.

#### Organization of Thesis

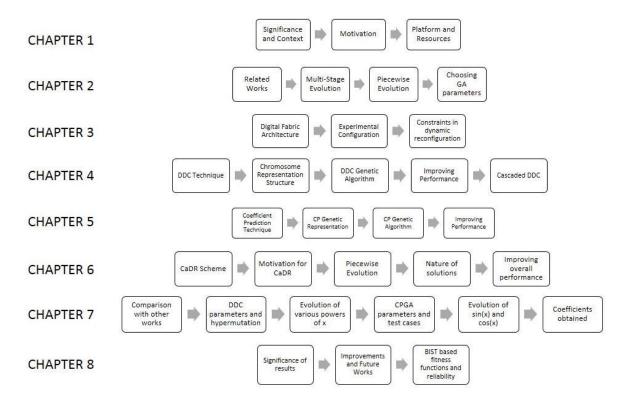

This thesis is organized into eight chapters. First the significance and context of this thesis is enumerated upon, motivation explained and the platform and resources used in building this work is described in the introductory chapter. Next, related works are explored, paradigms of

multi-stage and piecewise evolution introduced and the rationale behind choice of mode of crossover, mutation implementation and elitism and selection procedures are justified based on literature in this chapter on literature review. In chapter 3, the Programmable System on Chip platform (PSoC) and the resources available on it for dynamic reconfiguration are explored. In Chapter 4, Differential Digital Correction (DDC) technique developed to evolve various powers of x is elaborated on. In Chapter 5, the Coefficient Prediction (CP) technique developed to predict coefficients of various powers of x evolved in DDC is elaborated on. In chapter 6, the Cascaded Digital Refinement (CaDR) technique is reviewed and the nature of solutions obtained is discussed to improve on the scheme. In Chapter 7, Results of the work done are summarized, starting with comparison with other works, evolution of various powers of x using DDC and their use in CPGA to evolve solutions to sine and cosine of x. The coefficients obtained are also discussed. In Chapter 8, Conclusions about the significance of results, improvements and suggestions for future work and use of Built in Self-Test (BIST) based fitness functions to improve system reliability are discussed.

Figure 2: Organization of Thesis

# **CHAPTER TWO: LITERATURE REVIEW**

# Related Works

A variety of Evolutionary Algorithms (EAs) have been used to realize novel electronic circuit designs intrinsically on reconfigurable fabrics. Numerous innovative works have contributed to the literature of which only a few are highlighted in Table 1 relating to analog and hybrid analog-digital domains. For example, Koza et al. demonstrated an approach to automatic synthesis of analog circuits using Genetic Programming (GP) which included crossover and lowpass filters at various frequencies, an amplifier, a source identification circuit, a CC (cube-root), a time-optimal controller circuit, a voltage reference circuit, and a temperature-sensing circuit, all extrinsically using DC sweeps for fitness evaluation [16]. Mydlowec and others followed the path of Koza, evolving other CCs extrinsically [17, 18], in some cases using multiple time domain simulations to improve robustness.

| <b>Research Work</b> | Analog Circuits Evolved                          | EA Type   | Platform                                                                     | Contribution                                                                                                          |

|----------------------|--------------------------------------------------|-----------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| [Koza 1997]          | Square root                                      | Extrinsic | SPICE                                                                        | Used GP to design analog circuits using DC sweeps.                                                                    |

| [Mydlowec 2000]      | Square, square root, multiplier, and lag circuit | Extrinsic | SPICE                                                                        | Synthesis of computational circuits using multiple time-<br>domain simulations for robustness fitness evaluation.     |

| [Keymeulen 2000]     | Multiplier                                       | Intrinsic | Custom FPTA with 48<br>switchable transistor<br>terminals in two 0.5um chips | Population-based and Fitness-based fault tolerance.                                                                   |

| [Streeter 2002]      | Cube                                             | Extrinsic | Weakly-constrained virtual<br>fabric under progressive<br>voltage conditions | Average error 7-fold less than human design.                                                                          |

| [Cornforth 2014]     | Random Black Box Non-<br>linear circuits         | Extrinsic | NG-SPICE                                                                     | Demonstrated that an age-fitness incremental algorithm is<br>better for non-linear analog circuit fitness evaluation. |

| This work            | Square root, cube root,<br>square, cube          | Intrinsic | Cypress<br>PSoC-5LP                                                          | Digital resources enhance accuracy of self-scaling GA with PSO.                                                       |

Figure 3: Collection of Related Works [35]

Keymeulen et al. demonstrated intrinsic EHW on Field Programmable Analog Arrays (FPAAs) for population-based and fitness-based evolution of fault-tolerant analog circuits [30].

Later, Streeter et al. [29] also showed that GP was able to iteratively evolve circuits that could be attached to computational circuits to refine their performance. In [26] EAs were used to evolve four analog CCs as well as two digital circuits using analog components. In [23] swarming algorithms such as PSO were used to evolve analog circuit sizing. Recently, Cornforth et al. evolved non-linear circuits by utilizing a strategic fitness evaluation scheme without necessarily optimizing them for area. They were able to show that a variety of stimuli can extrinsically evolve nonlinear analog circuits, which conform to randomly generated black-box circuits, demonstrating the strength of the method.

While several previous works in analog CC design using EAs have involved simulation, recent Programmable System on Chip (PSoC) devices providing reconfigurable analog fabric, digital logic, and ARM cores enable new capabilities. Analog fabrics allow rapid evolution, but are limited by precision and/or accuracy, which may be refined with evolved digital circuits. The ARM core on the PSoC allows on-chip execution of EAs such as the GAs developed herein.

The work done by Shin and Hitoshi [32] describes the paradigm of multi-stage evolution to increase evolutionary pressure to manage circuit area more efficiently. This work also shows the advantages of using multi-stage evolution with regards to power, memory usage and better conformation to stringent accuracy requirements. Every succeeding stage of evolution leverages the results of the previous stage to evolve solutions that satisfy more strict accuracy and quality requirements than the previous stages, thereby supporting the fact that evolution in stages is desirable for design of complex circuits. This supports the idea of cascaded evolution stage followed by coefficient prediction developed herein. Work done by Kazadi, et.al [33], on the other hand explores piecewise evolution to evolve pieces of a circuit in discrete functional stages and breakdown of the problem into independent output units. They have shown that piecewise evolution that involves relatively random breakdown of a problem into independent units doesn't guarantee any improvements over overall evolution of the whole circuit as one piece. However, their work also mentions, "What would seem to be the correct line of future work in this area would be the investigation of viable ways of breaking down complex problems into simple connected parts". Hence, for problems where it is possible to achieve breakdown into simple connected stages, the paradigm of piecewise evolution is feasible. In the approach developed herein, it is mathematically shown that such breakdown is achieved for any mathematical function and hence the idea of cascaded evolution of powers of x followed by their combination is expected to be advantageous and better than the evolution of the complete solution function directly using all resources in one single stage. Additional reasons for using a flavor of piecewise evolution in multiple stages are the memory and fabric constraints which encourage this approach taken here.

#### **Evolutionary Algorithms**

Evolutionary algorithms rely on the building block hypothesis and questions about granularity of the building blocks used to build the candidate solutions are of prime importance when designing the chromosome representation and GA for the problem at hand. The most important considerations in the design of GAs are the genetic representation, fitness function and its complexity, selection scheme for the crossover function, mutation rate and adaptability of its rates and functionality to overcome stasis.

Various selection schemes are suggested for the crossover function. Selection schemes that favor crossover only among the fitter individuals result in premature convergence and though suitable for evolution in small search spaces, it is quite ill-behaved for larger search spaces. This was verified in this work, by starting with the evolution of 2:4 decoders which would converge to a decent solution (12 out of 16 outputs correct) within the first 100 generations and not improve at all owing to excessive presence of certain genes only, whereby at least one other important gene was always discarded in the selection process. Fitness proportional selection scheme is better and selects individuals for crossover with probability proportional to their respective fitness. This approach too suffers from some inadequacies. The work done by Annie S. Wu, et.al [12] elaborates on the commonly used selection schemes for crossover and introduces a fitness uniform selection scheme which preserves fitness diversity across generations and hence virtually guarantees good solutions with a well regulated convergence rate. This approach though, excellent for nondeceptive problems, doesn't perform well for deceptive problems. Tournament selection [34] is one popular scheme which is capable of producing good solutions with optimal convergence rates. In this work, as it is difficult to identify if the problem is deceptive or not, a variation of binary tournament selection with ideas inspired by fitness uniform selection scheme have been used.

With regards to fitness functions, the major drawback is with the complexity of evaluation and hence several approaches to tackle these problems have been presented. The paper by Haddow [11] provides an overview of the field of Evolvable Hardware (EHW) and pinpoints to the divide and conquer strategy that aims at simplifying the fitness evaluation space. Modularization and development of fitness functions on its basis are able to overcome scalability challenges in EHW to a very good extent, but determining modularity and determining fitness functions for the genes desirable to be retained is a highly involved and almost always a non-trivial task. This work ensures modularity and utilizes individual fitness functions for the same to ensure simplification of the computation process to enhance computational accuracy.

Royal Road functions [8] and experiments on them [9, 13] have revealed that, in general, it is best to combine building blocks that represent the finest granularity available for manipulation than coarser blocks owing to the fact that premature convergence has a very high probability of occurring in the latter. This is found to be essential in preserving genetic diversity as identified in [13] for fixed populations begin evolved. Thus, in order to determine series expansion to approximate a solution function, it is desirable to determine coefficients for each power of the independent variable being combined, separately than to attempt to find coefficients for groups of these terms. Thus, in this work, the coefficient prediction algorithm attempts to find coefficients for each power in consideration and combines them to obtain a decent approximation of the solution function. The coefficients are weights and CaDR may be viewed as a GA handling weights and develops on some of the ideas presented in [22] on weighted GA for multi-objective optimization.

# **CHAPTER THREE: PROGRAMMABLE SYSTEM ON CHIP**

#### PLD Architecture

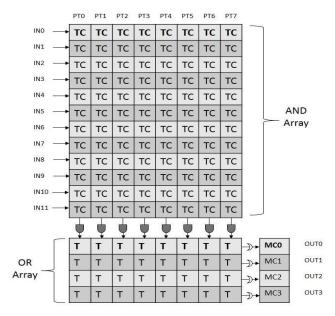

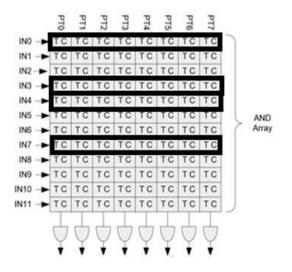

Figure 4: Simplified PSoC PLD Architecture adopted from [6]

Each PLD consists of an AND array with 12 input terms (IT) producing 8 product terms (PT) and an OR array that can programmatically access the 8 PTs to produce 4 output terms accessible either as combinational or registered outputs based on configuration written into each of the macro-cells (MCs) that control the nature of the output. This architecture is referred to as 12C4, where 12 stands for the number of input terms, C indicates that the PTs are constant and are accessible to the OR array and 4 indicates the number of output terms emerging from the OR array. Each input term in the AND array may be asserted as true or complement input, thereby contributing to the corresponding product in that fashion. Each term in the OR array may or may not be asserted, thereby allowing different logic combinations based on product terms arriving from the AND array.

# Macrocell Architecture

The outputs produced by the logic combinations in AND and OR arrays appear in macrocells that have carry in and carry out signals and provisions for XOR feedback, set/reset select, true or inverted registered output and output bypass that can be configured to have combinational or registered outputs. Configuring Macrocells to produce pure combinational outputs requires setting constant to logic 0 (this produces the output from the OR gate as is) and the output bypass for the macrocell under consideration to logic 1 (this multiplexes out the combinational output only).

# **Experimental Configuration**

LUT instantiation and wiring

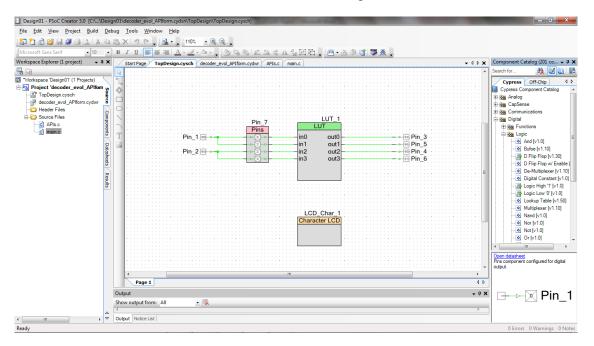

Figure 5: Schematic showing instantiated resources and connections

PSoC has no LUTs in hardware and the LUTs instantiated in the schematic are implemented in the PLDs. As illustrated in the above figure, a bus of pins maybe created anywhere in the schematic to connect input and output pins to different LUTs in the schematic as desired. This can be done only in the beginning, while boot-loading the code to the PSoC device though. The total number of LUTs that can instantiated for use is limited by the design space available in the schematic editor.

Force Directives - Pins

Figure 6: Design Wide Resources file showing pin assignment

For the simple design shown in the schematic in figure 5, specifying pin usage and is done as in the figure 6. For each pin used in the schematic, its placement may be directed in the .cydwr file which is also configured for many other components that may be used. Forcing resource utilization and implementation of LUTs in the PLD space

Placement directives, such as force directives may be used to force placement of LUT implementation to any specific PLD, which is analogous to the PROHIBIT command in the Xilinx User Constraint File [7]. Thus, through register writes, the logic function of each LUT implemented in each PLD is reconfigured in runtime. Hence logic configurability of each PLD is achieved through code eventually.

LUTs in the schematic are implemented in the PLDs. The number of input signals/bits available to each LUT in the schematic is restricted to a maximum of 5 by the IDE. The number of output signals/bits that can be forced out of a single LUT is 8. Each PLD however, only produces 4 output bits. In order to force the implementation of a LUT (instantiated in the schematic), the output bits of the LUT need to be placed in the PLD of interest, 4 at a time for each PLD. This is done by using the ForceSignal directive to place the corresponding output signal names to the PLD of interest. This imposes the restriction that each PLD can only accept 5 input bits and produce 4 output bits, since each LUT has an input width of only 5 bits. Hence, in the design, each LUT with 4 output bits maps to a single PLD. UDBs are identified by a pair of indices which indicate the

| 0    | 1 | 2 | 3  | 4  | 5  |

|------|---|---|----|----|----|

| 0 10 | 9 | 9 | 10 | 13 | 14 |

row and column number of the UDB in the following ordering grid:

4

7

4

3

0

5

6

6

5

2

1

Figure 7: UDB mapping scheme within PSoC build files adopted from [36]

The above chart indicates how UDBs are indexed in PSoC. There are two banks of UDBs available on PSoC – bank 0 and bank 1. Each UDB has a corresponding row and column number as indicated above, that uniquely identifies it irrespective of bank number. Each such UDB has two PLDs that are indicated by A and B. The general syntax is thus U(row\_number, column\_number)PLD\_index, where PLD\_index could be A or B depending on whether PLD 0 or PLD 1 is being referenced. Thus, for instance, if we are to reference PLD 0 (or A) of UDB 0, it would be written as U(2, 5)A. This information is used in forcing signals that arrive as outputs of LUTs to specific PLDs. In order to do so, the correct signal name is to be obtained from the report file generated when the project is built. Thus when attempting to find the signal name (also called

signal alias in the report), the project with a single LUT in the schematic is built without forcing directives. This randomly places the signals across different PLDs in the fabric. From the report file, the signal alias name is identified and then used for forcing corresponding signals. The general format of a signal alias is as follows:

\LUT\_x:tmp\_\_LUT\_x\_reg\_y\. Here x represents the number(/name) of the LUT as it appears in the schematic when instantiated and y represents the output bit/signal number arriving from that LUT. To force a signal to a particular PLD, two components are necessary– signal/alias name, UDB and PLD index obtained by referring to the chart above and following the referencing rule as detailed above. In addition to these, the force signal directive is to be chosen from the dropdown to force one output's placement in a specific PLD of choice. The following example shows how forcing is done for LUT\_1 instantiated in the schematic:

|                                                                  | esign01\decoder_evol_APIform.cydsn\decode | r_evol_AP[form.cydwr]                                                  |                       |

|------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------|-----------------------|

| <u>File Edit View Project Build</u>                              |                                           |                                                                        |                       |

|                                                                  | 🗈 🖭 🗙 🔊 (° 🖕 🔜 - 🖕 56%                    | • (4, C, _                                                             |                       |

| 普•孟 🍭 诸 👹 🔆 🖕                                                    |                                           |                                                                        |                       |

| Workspace Explorer (1 project) 🔹 🕈                               |                                           | oder_evform.cydwr APIs.c main.c                                        | <b>→</b> 4            |

| <b>4</b> G                                                       | Add Directive                             |                                                                        |                       |

| *Workspace 'Design01' (1 Projects) Project 'decoder_evol_APIform | Component (Signal) Name                   | Directive Type Directive Value                                         |                       |

| TopDesign.cysch                                                  | VLUT_1:tmp_LUT_1_reg_0                    | ForceSignal VU(2,5)A                                                   |                       |

|                                                                  | LUT_1:tmp_LUT_1_reg_0                     | ForceSignal 💌 U(2.5)A                                                  |                       |

| 🤄 Header Files                                                   | R VLUT_1:tmp_LUT_1_reg_0\                 | ForceSignal VU(2,5)A                                                   |                       |

| Source Files                                                     | UUT_tmp_LUT_treg_0                        | ForceSignal VU(2.5)A                                                   |                       |

| c) main.c                                                        | nex .                                     |                                                                        |                       |

|                                                                  | ×                                         |                                                                        |                       |

|                                                                  | 2                                         |                                                                        |                       |

|                                                                  | atas                                      |                                                                        |                       |

|                                                                  | hee                                       |                                                                        |                       |

|                                                                  | 8                                         |                                                                        |                       |

|                                                                  | 7                                         |                                                                        |                       |

|                                                                  | 8                                         |                                                                        |                       |

|                                                                  | 2                                         |                                                                        |                       |

|                                                                  | <u> </u>                                  |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  |                                           |                                                                        |                       |

|                                                                  | Pins AA Analog (+) Clocks                 | 💉 Interrupts 🗧 DMA 🛛 🐺 System 📲 Directives 🧧 Flash Security 🛛 🖆 EEPROM |                       |

|                                                                  | Output                                    |                                                                        |                       |

|                                                                  | Show output from: All                     |                                                                        |                       |

|                                                                  | 4                                         | ^                                                                      |                       |

|                                                                  | △ Output Notice List                      |                                                                        |                       |

|                                                                  | * Output Nouce List                       |                                                                        |                       |

| ady                                                              |                                           |                                                                        | 0 Errors 0 Warnings 0 |

Figure 8: Design Wide Resources file showing force directives for PLD placement

In order to add additional PLDs with the restrictions as mentioned above it is required to extend these placement directives, to all the PLDs of interest, keeping in mind the placement of all pins instantiated in the schematic and the way they are interconnected in the schematic as well. Following a similar procedure, the signal names are identified and are forced to the corresponding PLDs of interest.

### Constraints in Digital Configuration of 1 PLD:

Several constraints were encountered in the configuration of a single PLD of a specific UDB which implemented a single LUT placed in the schematic. The major constraints were as follows:

# Number of input terms that can simultaneously enter a PLD

Only 5 inputs could be fed to a single LUT and use of force directives wasn't able to achieve placement of inputs to a PLD, but only the placement of output signals to a specific PLD. Thus, only the corresponding input signals would arrive at the input end of the PLD. Though, there are 12 inputs available in a PLD, when placement is forced by the user, only as many inputs as an LUT supports can be accommodated in a PLD. This gives a constraint of being able to support only 5 input terms out of the 12 input terms available in the PLD architecture.

Selection of input lines used by the PLD in implementing the LUT

The input lines that are actually used by the PLD are randomly chosen out of the 12 input lines available to the PLD at design time, i.e. when the boot-loader programs the PSoC device.

This constraint is made more severe by the fact that the other input lines are in high Z state and hence if one of those lines are asserted in the OR array, then the corresponding output from the macrocell is also in high Z state. Thus, in order to avoid driving outputs to high Z state, the actual input lines initialized for use by the schematic need to be identified after the schematic configuration is built from the boot loaded code. These input lines are referred to as active lines and custom code was developed to identify these active lines by searching in the address space corresponding to the PLD(s) being used.

#### Storing the configuration:

PSoC's  $g^{++}$  compiler doesn't support Boolean type variable and hence several bit manipulation and type conversion operations had to be performed, to carefully extract out configuration from each register and store the same in the chromosome for that individual.

# Writing back configurations to the chromosomes:

Following the problem with inactive input lines and their potential to drive output to high Z state if asserted, reconfiguration of the PLD also involves writing only to the active lines identified. This restriction is limited only to the AND array, while the OR array has no such restrictions when 4 output terms are derived from the same. It has to be noted that if there are fewer product terms than 8 arriving at each line of the OR array, the other product terms if asserted later can result in high Z output for that line. Thus special care is taken to evolve the whole PLD with

non-coding sequences participating in evolution, but only the configuration of the active lines being written back in both arrays. This constraint provides an opportunity to test the effect of evolution of introns and their effect in convergence of the overall GA as and when required.

Writing back configuration to the corresponding registers:

Owing to the limitations of g++ compiler and the possibility of driving outputs to high impedance, writing back configuration to the registers, involved bit manipulations and type conversions and writing only if the corresponding active line were asserted in the chromosome.

# **CHAPTER FOUR: DIFFERENTIAL DIGITAL CORRECTION**

Differential Digital Correction Technique

Figure 9: DDC and Self-Scling GA schematic for analog-digital evolution [35]

The solutions obtained from analog evolution can rapidly approximate the desired solutions, although their accuracy is limited and susceptible to imprecision. The results of the analog stage are obtained and written to files. These files are then included in DDC code as header files for subsequent digital evolution. The Differential Digital Correction (DDC) technique selects a correction factor for each test input from a Normalized Error Array (NEA), which contains fractions of the maximum analog error. In order to build the NEA, the deviations of the analog outputs from the oracle are obtained and compared to obtain the maximum deviation or the maximum analog error. Following this, the NEA is constructed by generating fractions of the maximum analog error upto 256 levels with positive and negative correction factors adjusted to be able to provide correction to the case corresponding to maximum error as well, as shown below:

```

for (i=0;i<256;i++) {

if (i < 128)

NEA[i] = -((float)(127-i)/127.0) *

winner.maxDeviation;

else

NEA[i] = ((float)(i-127)/128.0) *

winner.maxDeviation;

}

</pre>

```

This DDC utilizes correction factors quantized to 256 levels and hence evolves PLDs to produce an 8-bit mapping for the 256 test inputs to reduce the error at each test point to the best possible extent. The DDC fitness is evaluated as follows:

# for i:= 0 to 255 fitness += oracle[i]-outanalog[i]-NEA [D]

The NEA containing correction factor elements called normalized differences is indexed by the instantaneous 8-bit output D, to realize the 8-bit output mapped to one of the 256 values which provides a correction factor of proportional magnitude. The D values so obtained are stored as the LUT configurations corresponding to the test inputs for which they appear. The fitness function thus represents cumulative error which is minimized through a GA which intrinsically evolves the digital fabric.

#### Representation Scheme and Chromosome Structure:

In order to evolve a single PLD, its configuration bits are encoded into a chromosome which genetic operators can act upon. The configuration bits consist of the following: active lines, AND array parameters and OR array parameters. Input lines that are active, i.e. not in high impedance state, in the actual implementation are determined from the register configuration immediately after booting and are marked as active lines; other lines cannot be written. There are 12 input lines for the AND array and four output lines for the OR array.

# Active Lines:

Input lines that are active in the actual implementation are determined from the register configuration immediately after booting and are marked as active lines. There are 12 input lines for the AND array and 4 output lines for the OR array. Hence we have a total of 16 active lines depending on the usage of resources determined from the schematic at the time of booting. Active lines are copied as is for all individuals generated for a particular PLD and remain, for all practical purposes, a constant gene of the chromosome.

Figure 10: Example of selection of active lines by IDE for logic implementation. Adopted from [6]

#### AND array parameters:

For each input line that is active, the input bit can be asserted as true or complement input in each of the product terms that will be calculated for each column in the array. There are 12 input lines with 8 columns each corresponding to the 8 product terms. For each column corresponding to an input line, the bit being considered can be asserted as true (0) or complement (1) and are encoded only for active lines in the same fashion in the chromosome. In order to encode the configuration, the configurations of the active input lines alone are to be recorded and hence up to eight such 32-bit integers store the configuration from the corresponding registers for two PLDs constituting a Universal Digital Block (UDB) in the fabric.

Initially, the bits of every input line in the AND array were considered and encoded for evolution. This resulted in larger evolution times with more time and resources being spent on introns or unexpressed genes. Additionally it also posed a greater risk of performing erroneous register writes. This process was found to be wasteful and hence introns were pruned out in encoding and subsequently in evolution. The current structure for evolution contains only the extrons and is hence much less resource and time intensive.

#### OR array parameters:

Like the AND array, for the OR array, each of the product terms arriving from the AND array may be asserted (1) or not asserted (0) and is encoded likewise in the chromosome. We have four such 16-bit integers that store the configuration from the corresponding registers. Hence we have an array containing 32 values for the OR array.

The chromosome for each PLD is encoded as a structure with three arrays: AL (active

lines), AND array parameters and OR array parameters representing configuration bits as described above and effectively describing contents of one UDB.

| 16 | bits | 32bits               | 32bits | 32bits | 32bits | 32bits | 32bits | 32bits | 32bits              | 16bits | 16bits | 16bits | 16bits |

|----|------|----------------------|--------|--------|--------|--------|--------|--------|---------------------|--------|--------|--------|--------|

| A  | AL   | AND array parameters |        |        |        |        |        |        | OR array parameters |        |        |        |        |

| _  |      |                      |        |        |        |        |        |        |                     |        |        |        |        |

|    |      |                      |        |        |        |        |        |        |                     |        |        |        |        |

| _  |      |                      |        |        |        |        |        |        |                     |        |        |        |        |

| 0  | 1    | 0 1                  | 1 1    | 1 0    | 1 0    | 1 1    | 1 1    | 1 1    |                     |        |        |        |        |

Figure 11: Chromosome representation for each UDB evolved in DDC

## DDC Genetic Algorithm

Generation of random individuals and the population size:

Individuals with the chromosome structure described above are randomly generated initially. The configuration of each of these individuals is programmed and the output is tested against various inputs applied to the board to evaluate fitness. The elite individuals are chosen for crossover with other individuals and their crossover probabilities are assigned based on their fitness. With regards to successful generation of random individuals, it was realized that seeding the random number generator appropriately was an important step. Seeding very often or too less often resulted in poor randomness and hence in the diversity of the populations in the initial or subsequent generations, accordingly as the case was observed to be. Also, a population of sufficiently large size was necessary to ensure that the search space was large enough not to lead the GA to a local extremum. Various population sizes were attempted given the memory limitations of the fabric. A population size of 80 was deemed suitable for evolution.

Elitism and selection of individuals for crossover:

An elitism of 2 is implemented where the two best fit individuals don't undergo mutation but have a high chance of crossing over with other individuals. In order to select individuals for crossover, binary tournament selection is implemented. Two adjacent individuals in the population array are checked for their fitness and the fitter one is chosen and stored in a separate array containing winners of the tournament in every such pair of individuals compared.

## Crossover:

The crossover operation is performed separately in each iteration for the AND arrays and OR arrays owing to their inherent functional differences. Crossover operation entails choosing a random crossover point (single point crossover) and copying the configuration bits from one end to the crossover point, respectively from each parent to generate the configuration bit-stream for the offspring. Crossover points were chosen to be at the boundaries between the eight 32 bit numbers in the AND array and the boundaries between four 16 bit numbers in the OR array respectively. Tournament selection is done with a tournament size of two and constitute 40 of the total 80 individuals per generation. Single-point crossover is then performed between one of these 40 fitter individuals and another individual randomly chosen from the whole population. The individuals so generated replace a fraction of the individuals in the population, while the remainder are from the fitter half of the population selected by binary tournament selection. The fraction of evolution. The fittest individual is marked to be preserved intact while other individuals undergo mutation.

Various schemes have been attempted for crossover. The first (and very ineffective scheme) involved choosing a class of elite individuals –fittest, second, third and fourth fittest individuals- and preforming crossover only between them to generate 6 new individuals which would replace the other 6. This resulted in a lack of genetic diversity and very quick convergence to a solution that wouldn't improve any further owing to very similar genes.

To improve performance, the crossover pattern was modified to pick the fittest and the second and perform crossover with probabilities of 100% and 50% and with a probability of 30% with the rest. This resulted in a slight increase in performance, but wasn't encouraging enough. The probabilities of crossover were then modified to 10%, 10% and 80% respectively for the crossover with the fittest, second and the rest, respectively. Again, the performance improved but only marginally.

The probabilities of crossover were modified to see improvements in performance and justifiably, a proportional search scheme was chosen for implementation. This scheme assigns a fixed probability of crossover for each individual based on its relative fitness value among all individuals. The probability of being chosen for crossover is essentially the ratio of the fitness of that individual to the maximum possible fitness that can be achieved. Individuals so chosen produce new individuals whose fitness is evaluated and subsequent replacement of less fit individuals in the older generation occurs. New individuals so generated replace the older individuals while the fittest and the second fittest individuals of each generation are retained. This approach resulted in good improvements in performance. Considering the success of the proportional search scheme above and the need for fitness diversity while still finding the problem of evolution not entirely classifiable as non-deceptive, the fitness uniform selection scheme as discussed in Dr. Wu's work [12] couldn't be adopted as is. Tournament selection was selected to offer better fitness diversity, while the scheme for replacement of individuals involving maintaining all or a fraction of the fitter individuals selected in the tournament tries to emulate the advantages of the proportional search scheme and possibly overcoming the problem if deception where it appears. Maintenance of an elitism of 2 helped with debugging and code development, especially when concerns of losing the best individual appeared.

#### Mutation:

Mutation is implemented as a simple bit flip with a finite probability of occurring at any position on the chromosome. All but the two most elite individuals undergo simple bit flip mutation with a default mutation rate of 0.1% per bit in the chromosome. In order to deal with a potential stasis condition several schemes were attempted. The mutation rate was ramped up by 1 (or a small increment) percent every few hundred iterations in a fixed fashion. The number of iterations after which the rise occurred was tuned to determine a suitable empirical number, but this approach failed to produce good results for all the different circuits being evolved. Unusually high mutation rates were also used in hopes of improving the performance.

Mutation rate was observed to be a crucial factor in the performance of the DDCGA with adaptive mutation being very useful in overcoming stasis. Other mutation altering strategies discussed before weren't as effective in improving performance. A condition of stasis is detected and reported if the best fitness achieved hasn't changed in 50 iterations using a single control bit. The difference between average fitness and best fitness achieved is compared and encoded likewise in the stasis information to decide whether mutation should be enabled at the default rate or at an incremented rate, where increments in steps of 0.01 improved performance. Faster rates destroyed good solutions and slower rates couldn't help maintain enough diversity to search for better solutions.

Improving performance of the GA and overcoming stasis conditions:

In order to improve the performance of the GA, initially parameters were tuned using different crossover parameters. Choosing boundaries that match with the chromosome structure better proved to be beneficial. Also, choosing a random point for crossover instead of a fixed point on the chromosome helped improve the search space. Initially, evolution was attempted with crossover at mid-point only. This was followed by attempts within a fixed set of points. These experiments produced poor results as the genetic diversity was severely restricted. Completely random crossover points with no strictly defined boundaries were then attempted and it was noticed that good solutions disappeared very soon after their appearance owing to extreme variations. A fair balance was achieved when crossover boundaries matched with the chromosome definitions introducing randomness within reasonable limits.

One other technique to add to genetic diversity involved creating and introducing some random individuals into the gene pool after a few hundred iterations when a potential stasis like situation was expected. This helped improve the randomness and hence the search space in some cases. Unlike mutation, however, the randomness introduced by addition of new individuals easily went beyond control when more than 2 individuals were introduced at a high frequency (less than 50 generations). Very controlled addition of a single random individual resulted in performance mostly at par with the case where such an addition weren't being made. Like in the case of mutation, it is expected that performance could improve if addition of random individuals were performed on demand with an adaptive flavor to resemble what is popularly called hyper mutation. This approach is still under investigation.

Evolving individuals by building chromosomes only form the extrons resulted in quicker evolution times and gave better scope for scalability and extension to multi-PLD chromosome. Evolution with active lines alone results in better utilization of memory and is largely used. Evolution with introns is attempted as an additional exercise to study their benefits.

## PLD allocation and utilization:

Differential Digital Correction GA (DDCGA) reconfigures the digital fabric. The DDCGA evolves four PLDs of two chromosome sets per individual: one each for the AND and OR arrays, and one set of individuals for each pair of four PLDs, given constraints of the digital fabric. Use of fewer PLDs was found to provide insufficient resources for evolution, while the use of a larger number of PLDs didn't produce better results than with 4 PLDs. Also, considering the memory constraints of PSoC, parallel evolution of more PLDs introduced issues with randomness and loss of tractability owing to insufficient memory to have a sufficiently large population for all PLDs to evolve, thereby resulting in a drop in performance once the population size was affected by the resource allocation for all PLDs for each step in evolution.

## Cascaded DDC:

Following the success of DDC in evolving powers of x such as square, cube, square root and cube root, a few other powers of x were evolved too. These included the analog computational circuits for fourth root and fourth powers of x which were then refined by DDC. Circuits to compute zeroth and first powers of x were trivial and required very short evolution times to obtain corresponding analog computation circuits, followed by short DDC stages to refine them. Thus, different powers of x starting from fourth root through fourth power of x were evolved in a cascaded fashion, one following the other and the arrays containing the outputs of each of these stages were stored separately for the coefficient prediction stage to act on the same.

# **CHAPTER FIVE: COEFFICIENT PREDICTION**

#### **Coefficient Prediction Technique**

Following the cascaded DDC stage, the coefficient prediction (CP) stage attempts to predict coefficients of the evolved circuits that can be combined through addition to approximate the available range of functional values of the independent variable, x, to best represent the composite function in terms of the independent variable. Coefficients are randomly assigned initially to each of the eight powers of the independent variable, evolved by cascaded stages of DDC starting from the most accurate to the least accurate power (smallest to largest). The coefficient prediction phase first performs range scaling of the computed oracle by dividing all the values in it by a scaling factor that is determined from overflow considerations in calculations involving multiplication of the largest coefficient assignable and the largest value of biggest power of x used and the sum of all such products for all powers of x that would not result in an overflow in the results computed. Once range scaling is performed, CPGA randomly initializes a population with random coefficients for each power of x and performs fitness evaluations, selects good individuals, performs single-point crossover at a randomly determined point to exchange genetic material followed by mutation to evolve a suitable set of coefficients that act as weights in combining different powers of x to produce functions that approximate the solution function as closely as possible given the number of iterations after which it is terminated. The chromosome for  $x^0$  function is trivial and hence in order to reduce overall evolution time, it isn't evolved, but the values are directly written to the corresponding array.

## Coefficient Prediction Genetic Representation

## Chromosome Structure:

The chromosome is a simple array of 8 floating point numbers, each of which is within the range determined after range scaling. Bitwise manipulations of the chromosome aren't performed from code in any step in the CPGA. Each chromosome is equivalent to set of coefficients for all the data points for all powers of x. The following is the chromosome for one individual:

| x^1/4 | x^1/3 | x^1/2 | 1  | x  | x^2 | x^3 | x^4 |

|-------|-------|-------|----|----|-----|-----|-----|

| CO    | C1    | C2    | C3 | C4 | C5  | C6  | C7  |

Figure 12: Chromosome representation for coefficients evolved in CP

The chromosome and the corresponding correlations between the coefficients and various powers of x are as indicated above. Each of the coefficients C0 through C7 in the above chromosome is within the scaled range obtained after performing range scaling.

# Coefficient Prediction Genetic Algorithm

# CPGA Algorithm Flow

Range Scaling:

- Determine largest value of the largest power of *x* from cascaded DDC

- Determine the range of values for each coefficient being evolved from the following relation:

- C\_range\*A\_largest\*8 = range( float32)

- Or C\_range = range(float32)/(A\_largest\*8)

# Initialize Population:

• Randomly pick values using rand()%C\_range for all the coefficients C0, C1, C2, C3, C4, C5, C6, C7

- Initialize 80 individuals or more with randomly chosen coefficients *Dynamic Range Adaptation:*

- Check if best fit individual has a total error greater than 100

- Halve C\_largest and re-initialize population with new coefficients in smaller range except first 10 individuals

- Continue narrowing search space by reducing C\_largest till a comfortable range is found

- *Range forcing*: Further narrow range by halving C\_largest for half the population after error goal is achieved

# Fitness Evaluation:

- Store the values of {oracle[i]-(output[i]-NEA[D\_array[i]]} in a separate array called results \_DDC\_C0 for x^(1/4) and likewise for other powers: results \_DDC\_C1, results \_DDC\_C2, results \_DDC\_C3, results \_DDC\_C4, results \_DDC\_C5, results \_DDC\_C6, results \_DDC\_C7 for C1 through C7 as well respectively

- Multiply C0\* results \_DDC\_C0 and store in array S0

- Multiply C1\* results \_DDC\_C1 and store in array S1

- Multiply C2\* results \_DDC\_C2 and store in array S2

- Multiply C3\* results \_DDC\_C3 and store in array S3

- Multiply C4\* results \_DDC\_C4 and store in array S4

- Multiply C5\* results DDC C5 and store in array S5

- Multiply C6\* results \_DDC\_C6 and store in array S6

- Multiply C7\* results \_DDC\_C7 and store in array S7

- Add  $S0+S1+S2+S3+S4+S5+S6+S7 = \Sigma S$

- Error =  $S \Sigma S$

- Fitness = sum(Error)

# Crossover:

- Select elite 2

- Binary tournament selection

- Single point crossover with tunable number of individuals to be replaced in the population and fitter individuals pool as in DDC

# Mutation:

- With probability of mutation Pm, add rand(-1, 1) (is this the best way to mutate them??) to each gene of the chromosome

- Leave out elite 2 unaltered

# Continue GA:

- When stasis is detected adapt mutation rates

- Introduce hypermutation as introduction of random individuals if necessary on demand to improve genetic diversity

Terminate and Present Solution:

- Terminate when maximum number of iterations is reached (or if the fitness goal is achieved)

- Print coefficients and error of the best fit individual obtained

## Range Scaling

As in indicated in algorithm flow above, the coefficients C0 through C7 are all floating point numbers. However, each is multiplied by the corresponding power of x to calculate the solution at every test point. Consider the following calculation of the solution at a test point i:

# Sol[i] = $C0*x^{(1/4)}[i] + C1*x^{(1/3)}[i] + C2*x^{(1/2)}[i] + C3 + C4*x^{[i]} + C5*x^{2[i]} + C6*x^{3[i]} + C7*x^{4[i]}$

For the above calculation at a test point i, it is seen that the sum of products must be a value within the range of Sol[i], which is a 32 bit floating point number. In order to ensure that all coefficients have the same scaled range for easy scalability of the final solution obtained, the scaling factor, A\_largest is determined by dividing overall range of values of float32 by  $8*x^4[255]$ . Coefficients are randomly picked within this scaled range to initialize the population for evolution.

#### Generation of random individuals and the population size:

Individuals with the chromosome structure described above are randomly generated initially. The configuration of each of these individuals is programmed and the output is tested against various inputs applied to the board to evaluate fitness. The elite individuals are chosen for crossover with other individuals and their crossover probabilities are assigned based on their fitness. With regards to successful generation of random individuals, it was realized that seeding the random number generator appropriately was an important step. Seeding very often or too less often resulted in poor randomness and hence in the diversity of the populations in the initial or subsequent generations, accordingly as the case was observed to be. Also, a population of sufficiently large size was necessary to ensure that the search space was large enough not to lead the GA to a local extremum. Various population sizes were attempted given the memory limitations of the fabric. A population size of 80 was deemed suitable for evolution.

## **Dynamic Range Adaptation:**

When arbitrarily large coefficients are chosen for evolution, the total error is observed to be arbitrarily large as well and the search space in this case is too large for a GA to be able to navigate through in a fixed number of generations. Mutations and crossovers aren't sufficient to sufficiently alter the coefficients to be able to reduce the search space and obtain fitter individuals. Thus a technique to dynamically alter the range of coefficients defining the chromosome is used. Every iteration where the total error is larger than 100, the range of the coefficients chosen for all but the first ten individuals is halved. Crossover and mutation are then performed. This results in production of fitter individuals or otherwise depending on the nature and characteristics of the solution function. Range adaptation reduces the range of exploration of coefficients to a more likely range for all powers of *x* involved. Range forcing is also attempted when the total error is less than 100, in which case the coefficients of a quarter of the individuals is halved. Range forcing hasn't been able to produce significant results for sin(*x*) but may

produce better results for other functions. Dynamic range adaptation is essential in order to ensure meaningful evolution of coefficients and spans the first few iterations in CPGA.

#### Elitism and selection of individuals for crossover:

An elitism of 2 is implemented where the two best fit individuals don't undergo mutation but have a high chance of crossing over with other individuals. In order to select individuals for crossover, binary tournament selection is implemented. Two adjacent individuals in the population array are checked for their fitness and the fitter one is chosen and stored in a separate array containing winners of the tournament in every such pair of individuals compared.

## Crossover:

The crossover operation is performed by choosing a random crossover point between two of the eight coefficients in the chromosome. Crossover operation entails choosing a random crossover point (single point crossover) and copying the configuration bits from one end to the crossover point, respectively from each parent to generate the coefficients defining the offspring. Tournament selection is done with a tournament size of two and constitute 40 of the total 80 individuals per generation. Single-point crossover is then performed between one of these 40 fitter individuals and another individual randomly chosen from the whole population. The individuals so generated replace a fraction of the individuals in the population, while the remainder are from the fitter half of the population selected by binary tournament selection. The fraction of individuals that would be replaced with new individuals is a parameter tunable at the beginning of evolution. The fittest individual is marked to be preserved intact while other individuals undergo mutation. Following the success of tournament selection for DDC and for reasons concerning deceptiveness of the problem at hand and offering fitter individuals a higher chance to pass on their genes, as discussed in the crossover section of DDC, binary tournament selection was chosen for implementation.

## Mutation: