# **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# UM®

# HIGH PERFORMANCE TERMINATION DETECTION TECHNIQUES SUPPORTING MULTITHREADED EXECUTION

by

YILI TSENG B.S.M.E. National Taiwan University, Republic of China, 1985 M.S. University of Florida, 1990 M.S. University of Central Florida, 1995

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2000

Major Professor: Ronald F. DeMara

UMI Number: 9990651

UMI Microform 9990651

Copyright 2001 by Bell & Howell Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

©2000 Yili Tseng

# ABSTRACT

Efficient detection of execution termination is essential for optimizing throughput of multithreaded parallel computer architectures. In particular, an ensemble of processing elements (PEs) is said to have reached termination of processing upon completion of each interval of concurrent activity. Points at which synchronization occur are referred to as *synchronization barriers*. The design objective is to minimize the amount of overhead required to enforce completion of each barrier prior to the resumption of subsequent processing.

This dissertation begins by developing a novel taxonomy for termination detection techniques based on thread allocation strategy and degree of processor reactivation support. A capability class hierarchy ranging from *Static-Binding Idle-Tasking* to *Dynamic-Binding Any-Tasking* is derived as a result of the taxonomy. Together they assist significantly in identification of properties which facilitate algorithm assessment and refinement. A message, bit, time, and space optimality analysis indicates that as few as (E-N) additional messages can be utilized to realize dynamic binding rather than static binding of threads on N PEs with E reporting events. These results are assessed against those for the CV, LTD, Credit, and Tiered algorithms to demonstrate the corresponding time and space performance which are achievable in practice.

The *Tiered Detection Algorithm* is shown to approach practical efficiency limits and is further refined in terms of its global invariant across non-serializable message communication channels. By attaching the level of thread nesting to thread consumption and production counts, it prevents false termination hazards. Its advantage in detection delay is revealed in average and worst cases over CV and LTD algorithms concerning the traversal of processor hierarchy and implementation performance of the Credit Algorithm.

The Tiered algorithm is then extended to a hardware-based approach, which is shown to be time and wire-efficient. The *Distributed-Sum Bit-Comparison (DSBC)* logic developed is capable of supporting dynamic allocation of tasks for multithreaded execution on shared-memory, message-passing, and/or single-chip multiprocessors. For a system of N PEs, a single instance of global logic and N instances of local logic interconnected by 3N wires are shown to provide direct support to the compiler and programmer for any arbitrary number of barriers. DSBC detection time upon completion of the last task is shown to scale linearly in terms of the number of active barriers in the

system. Comparison to Wired-NOR hardware and shared-lock software approaches demonstrate reduced barrier detection time, decreased inter-PE wiring requirements, and increased functionality. Finally, a version is designed using *Null Convention Logic* to provide a delay-insensitive alternative implementation that eliminates race conditions and timing considerations in distributed environments.

Dedicated to my father and mother, Mr. Pao-Tung Tseng and Mrs. Hsueh-Ju Liu

# 高效能支援多軌執行之偵測程式終結技術

謹以此博士論文獻給我的雙親 — 曾保堂先生與劉雪如女士

暂屹立

vi

# ACKNOWLEDGMENTS

First, I would like to appreciate my parents, Mr. Pao-Tung Tseng and Mrs. Hsueh-Ju Liu. Without their love and financial support during the course of my pursuit of the Ph.D. degree, there will be no existence of this dissertation. I will make them proud of this son by my future contribution to this universe.

Next, I want to acknowledge my advisor, Dr. Ronald. F. DeMara. His considerateness and supportive personality gave me a precious opportunity to tackle my health problem before working on the academic research. Not every advisor owns this noble character and that proves to be more valuable than the academic ability is. His master style instruction gave me the greatest freedom to challenge myself and explore the unknown space of knowledge while his insight provided a clear direction. It is not only beneficial but also pleasant to practice researching under his instruction. I will reward him by my future achievements.

I also would like to express my gratitude to an unsung heroine, my wife, Chyong-Ru. I appreciate her support and companion through the ordeal of my work toward the Ph.D. degree. My unusual experience is not worth mentioning to others, however it provides useful practice to both of us, which will benefit the rest of our life. The adversity and adversary in the past turned out to be stepping stones rather than obstacles in the road.

The success of my elder brother and sister-in-law, Drs. Yi-Ping Tseng and Huei-Chu

Liao inspired my desire to explore more knowledge. Their encouragements keep me motivated in difficult times. They will always be my role models.

As for the roles of my sons, David and Daniel, the usual scenario in a dissertation's acknowledgments is " I appreciate my sons' cooperation by going to bed at 9 P.M. everyday so that I have time to finish my research. ". Since that never applies to them, I have made the following decision. If they want their names to be inscribed in any dissertation, they have to write their own!

#### 銘謝

首先我要感謝我的雙親, 曾保堂先生與劉雪如女士。在攻讀博士學位過程中, 如無他們精神上與經濟上的支持, 今日即無此博士論文之存在, 我將以未來對宇宙 之貢獻榮耀他們。

其次我要感謝我的指導教授,隆纳德·狄邁拉博士,其熱心助人及體諒他人之 個性,使我有實實之機會調養好身體健康再進行學術研究。並非每位指導教授都有 此高貴情操,且此情操證明比學術能力更有價值。他的洞察力及眼光指點了明確的 研究方向,但其大師式的教導讓我有極大自由挑戰自我及探索未知之知識空間。在 其指導下作科學研究,非但獲益良多且是令人愉快之人生經驗。我將以未來成就回 報。

我也要對一位幕後英雄表達謝意,即內子莊瓊如。感謝她的支持與伴隨我走過 邁向博士之路之嚴苛考驗。我比他人艱辛的境遇不足為外人道,但卻提供了彌珍足 貴之人生歷練,將使我們夫婦終生受益。過去的逆境與阻撓者證明不成為路上之障 礙物,反是助我成功之踏腳石!

我的大哥與大嫂,曾一平博士與廖惠珠博士,當年他們的成就激發了我追求更 多知識之欲望,他們的鼓勵與支持使我在低潮時候依然鬥志昂揚,他們永遠是我的 楷模。

至於我兒,曾翔緯與曾勛熠,尋常博士論文銘謝頁都寫道:『感謝我子女之合作, 每晚九時準時就寢,使我有餘暇完成博士學位。』然因此情從未在我二子身上發生, 故我決定,如果他們想要名字被寫入任何博士論文,他們必須撰寫各自之博士論文!

viii

# TABLE OF CONTENTS

# LIST OF FIGURES

xii

| LI | ST ( | OF TABLES                                                | xiii |

|----|------|----------------------------------------------------------|------|

| 1  | INT  | TRODUCTION                                               | 1    |

|    | 1.1  | The Barrier Synchronization Problem                      | 1    |

|    | 1.2  | Significance of Synchronization and Quiescence Detection | 2    |

|    | 1.3  | Application-Driven Synchronization Requirements          | 3    |

|    |      | 1.3.1 Granularity of the Application Tasks               | 3    |

|    |      | 1.3.2 Degree of Thread Concurrency                       | 3    |

|    |      | 1.3.3 Apriori Knowledge of PE Participation              | 4    |

|    | 1.4  | Architecture-Driven Synchronization Requirements         | 5    |

|    |      | 1.4.1 Interprocessor Communication Strategy              | 5    |

|    |      | 1.4.2 Machine-Specific Configuration Parameters          | 5    |

|    |      | 1.4.3 Availability of Barrier Hardware                   | 6    |

|    | 1.5  | Taxonomy of Termination Detection Techniques             | 6    |

|    |      | 1.5.1 Capability Categories                              | 6    |

|    |      | 1.5.2 Class Hierarchy                                    | 7    |

|    | 1.6  | Organization of the Dissertation                         | 9    |

| 2  | PRI  | EVIOUS WORK                                              | 10   |

|    | 2.1  | Overview                                                 | 10   |

|    | 2.2  | Static-Binding Idle-Tasking Capable Techniques           | 10   |

|    |      | 2.2.1 Butterfly Barrier                                  | 10   |

|    |      | 2.2.2 U-cube Tree Algorithm                              | 12   |

|    | 2.3  | Static-Binding Same-Tasking Capable Techniques           | 16   |

|    |      | 2.3.1 CV Algorithm                                       | 16   |

|    |      | 2.3.2 LTD Algorithm                                      | 18   |

|    | 2.4  | Static-Binding Different-Tasking Capable Techniques      | 21   |

|    |      | 2.4.1 Collective Synchronization Tree                    | 21   |

|    |      | 2.4.2 Fetch-and-Add                                      | 22   |

|    | 2.5  | Static-Binding Any-Tasking Capable Techniques            | 24   |

|    | 2.6  | Dynamic-Binding Idle-Tasking Capable Techniques          | 25   |

|    |      | 2.6.1 AND Gate Barrier                                   | 25   |

|    |      |                                                          |      |

|   |            | 2.6.2 TTL_PAPERS                                       | 6  |

|---|------------|--------------------------------------------------------|----|

|   | 2.7        | Dynamic-Binding Same-Tasking Capable Techniques        | 7  |

|   |            | 2.7.1 Simultaneous Access Variable                     | 7  |

|   |            | 2.7.2 The Counting Algorithm                           | 0  |

|   | 2.8        | Dynamic-Binding Different-Tasking Capable Techniques   | 2  |

|   |            | 2.8.1 Wired-NOR Barrier                                | 2  |

|   |            | 2.8.2 Barrier Synchronization Register Hardware        | 3  |

|   | 2.9        | Dynamic-Binding Any-Tasking Capable Techniques         | 6  |

|   |            | 2.9.1 Credit Algorithm                                 | 6  |

|   | 2.10       | Summary 3                                              | 7  |

| 3 | OP         | <b>FIMALITY ANALYSIS OF TERMINATION DETECTION TECH</b> | [- |

|   | NIC        | UES 3                                                  | 8  |

|   |            | Basis                                                  | 9  |

|   | 3.2        | Preliminary Analysis                                   | 0  |

|   | 3.3        | Analysis of Optimality Cases                           | 3  |

|   | 3.4        | Optimality for Static-Binding Category                 |    |

|   | 3.5        | Optimality for Dynamic-Binding Category                |    |

| Л | TIE        | RED DETECTION ALGORITHM 4                              | 8  |

| T | 4.1        | Overview                                               |    |

|   | 4.1        | Operation of the Processing Element                    |    |

|   | 4.2<br>4.3 | Operation of the Controller                            |    |

|   |            |                                                        |    |

|   | 4.4        |                                                        |    |

|   |            | <b>-</b>                                               |    |

|   |            | 8                                                      |    |

|   |            | 4.4.3 Bit Complexity                                   |    |

|   |            | 4.4.4 Detection Delay                                  |    |

|   |            | 4.4.5 Space Complexity                                 |    |

|   | 4.5        | Software Design Optimizations                          |    |

|   | 4.6        | Summary                                                | 8  |

| 5 |            | TRIBUTED-SUM BIT-COMPARISON LOGIC 6                    |    |

|   | 5.1        | Overview                                               |    |

|   | 5.2        | Operational Concept                                    |    |

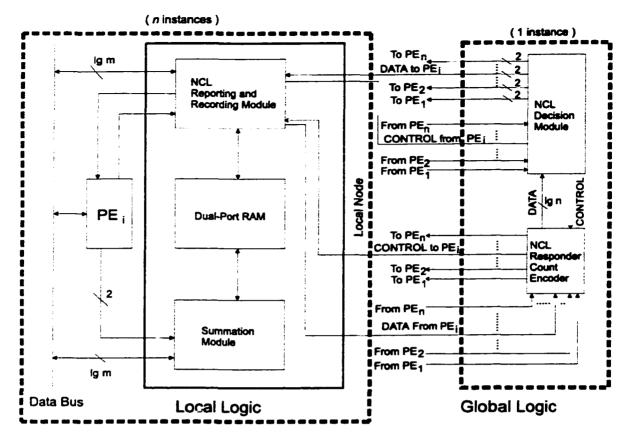

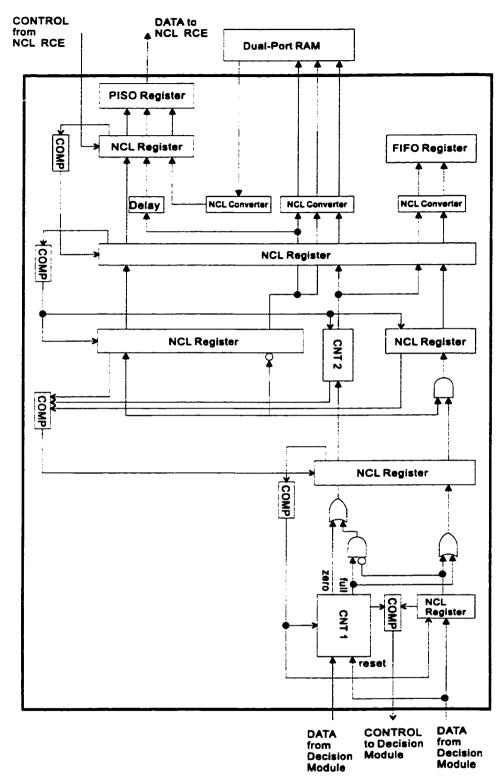

|   | 5.3        | Hardware Components                                    |    |

|   |            | 5.3.1 Local Logic                                      |    |

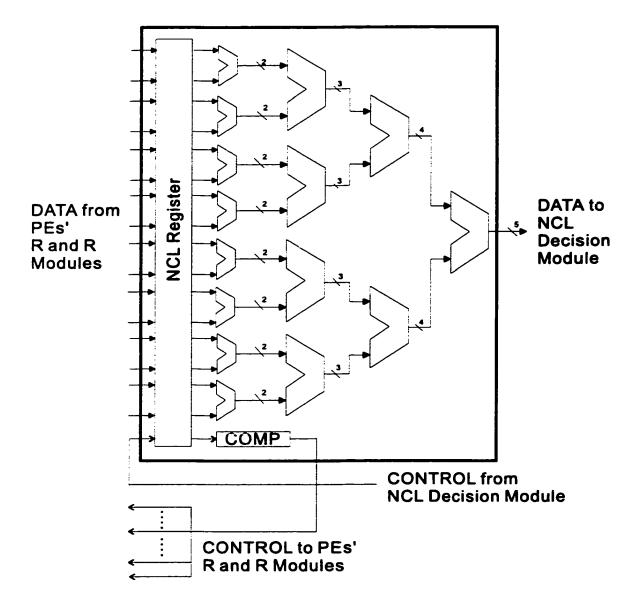

|   |            | 5.3.2 Global Logic                                     | 6  |

|   | 5.4        | Performance Analysis                                   | 9  |

|   |            | 5.4.1 Detection Time                                   | 9  |

|   |            | 5.4.2 Comparisons of Performance and Features          | 3  |

|   | 5.5        | Delay-Insensitive Design                               | 6  |

|   |            | 5.5.1 Null Convention Logic                            | 7  |

|   |            | -                                                      |    |

|    | 5.6         | 5.5.2 NCL Version DSBC Logic                                         |                       |

|----|-------------|----------------------------------------------------------------------|-----------------------|

| -  | 6.1         | NCLUSION       9         Summary       1         Future Work       1 | <b>98</b><br>98<br>01 |

| LI | <b>ST C</b> | F REFERENCES 10                                                      | )3                    |

# LIST OF TABLES

|     | Operations in the Router for CS Tree [29] . |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|-----|---------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 2.2 | SAV Value Returned by PEs                   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 27 |

| 3.1 | Notation used in Performance Analysis       | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 39 |

| 4.1 | Comparison of Message Complexity            |   | • | • |   |   |   |   |   |   |   | • |   | • | • | 58 |

| 4.2 | Comparison of Message Bit Complexity        | • | • | • |   |   |   | • | • | • |   | • | • |   |   | 62 |

| 4.3 | Comparison of Detection Delay Complexity    | • | • |   |   |   | • | • | • |   | • |   |   | • | • | 65 |

| 4.4 | Comparison of Aggregate Space Complexity    |   | • |   |   |   |   |   |   |   |   |   |   |   |   | 67 |

# LIST OF FIGURES

| 1.1  | Parallelizable Code Fragment Requiring Synchronization                 |

|------|------------------------------------------------------------------------|

| 1.2  | Classification Scheme based on Functionality of Barrier                |

| 1.3  | Hierarchy of Barrier Classes                                           |

| 2.1  | 2-Process Butterfly Barrier                                            |

| 2.2  | Butterfly Barrier Expanded to Support Multiple Processors 12           |

| 2.3  | U-cube Tree Algorithm [23]                                             |

| 2.4  | Example for U-cube Tree Algorithm                                      |

| 2.5  | Procedures used in CV Algorithm [10]                                   |

| 2.6  | Procedures used in CV Algorithm [10]                                   |

| 2.7  | Procedures used in CV Algorithm [10]                                   |

| 2.8  | Algorithm for $p_i, 1 \le i \le n$ , in LTD Algorithm [12]             |

| 2.9  | Procedures used in LTD Algorithm [12]                                  |

| 2.10 |                                                                        |

| 2.11 | Fetch and Add Barrier Code                                             |

|      | Simple AND Gate Barrier                                                |

| 2.13 | NAND Tree in TTL_PAPERS                                                |

| 2.14 | SAV Algorithm [22]                                                     |

|      | Counting Algorithm [31]                                                |

|      | Wired NOR Barrier                                                      |

|      | Single Barrier Register Hardware [27]                                  |

|      | Multiple Barrier Register Hardware [27]                                |

| 3.1  | Case A for Optimality Analysis                                         |

| 3.2  | Case B for Optimality Analysis                                         |

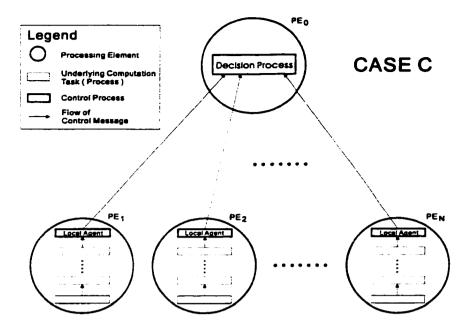

| 3.3  | Case C for Optimality Analysis                                         |

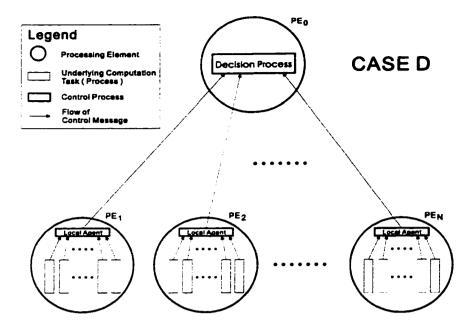

| 3.4  | Case D for Optimality Analysis                                         |

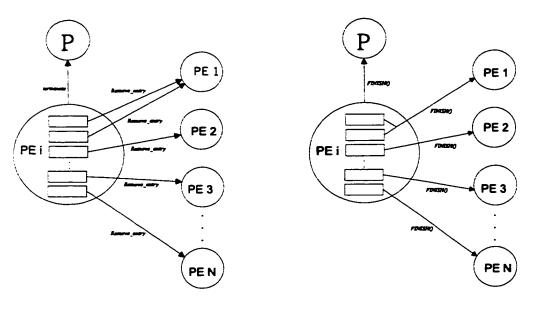

| 4.1  | Operation of the Processing Element in Tiered Detection Algorithm . 50 |

| 4.2  | Activity Table                                                         |

| 4.3  | Operation of the Controller in Tiered Detection Algorithm 53           |

| 4.4  | Messages Sent After the PE turns Idle                                  |

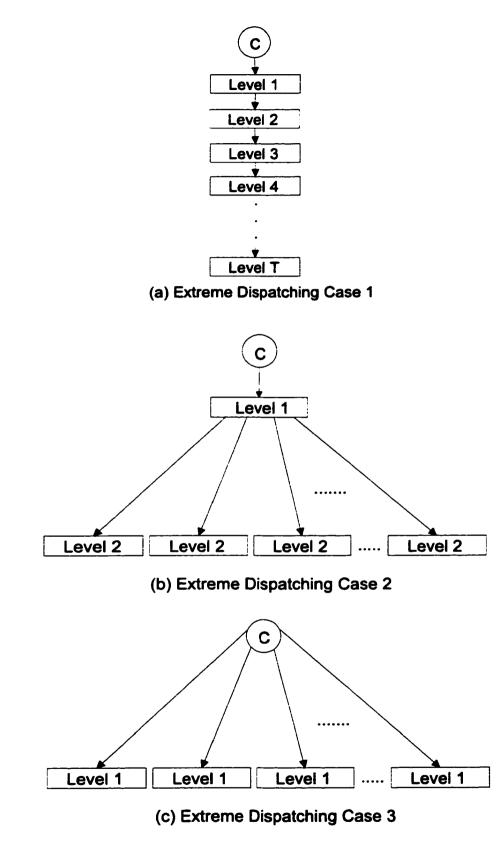

| 4.5  | Extreme Dispatching Patterns for Tiered Detection Algorithm 59         |

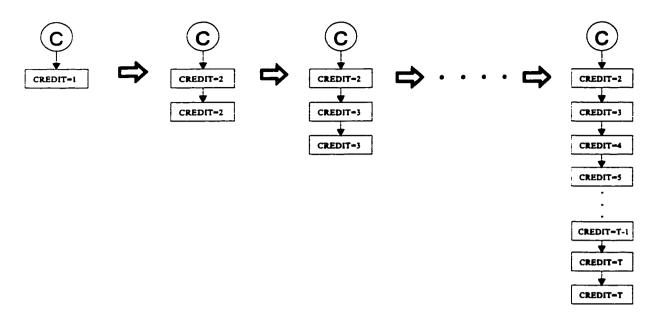

| 4.6  | Extreme Dispatching for Credit Algorithm                               |

| 4.7  | Dispatching for the Worst cases of CV and LTD Algorithms 63            |

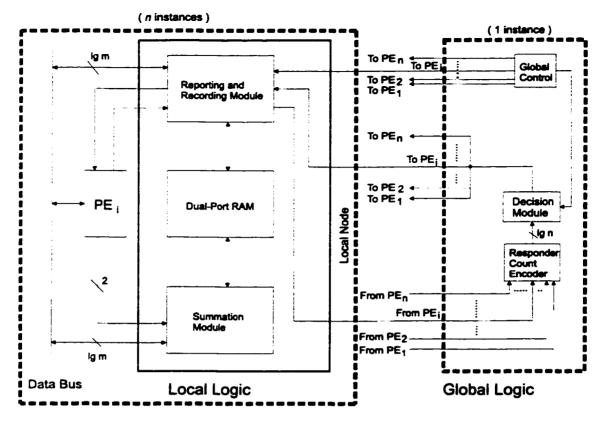

| 5.1  | Basic Layout                                                   |

|------|----------------------------------------------------------------|

| 5.2  | DSBC Algorithm                                                 |

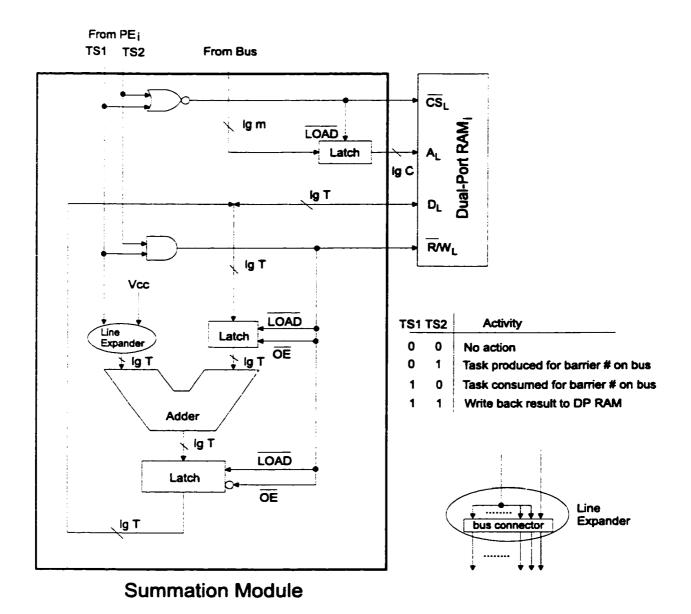

| 5.3  | Summation Module                                               |

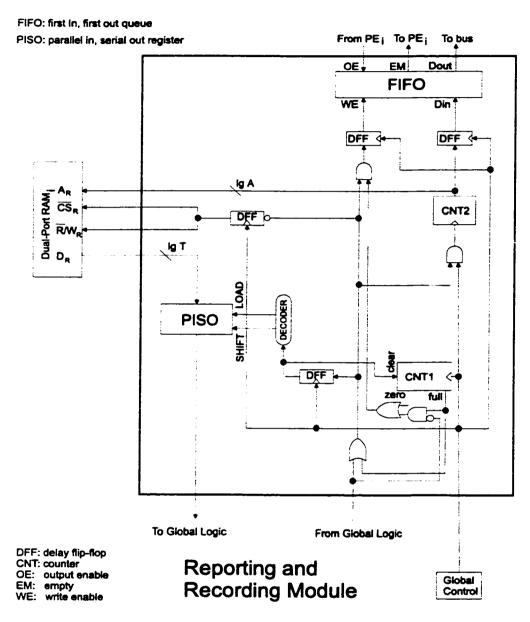

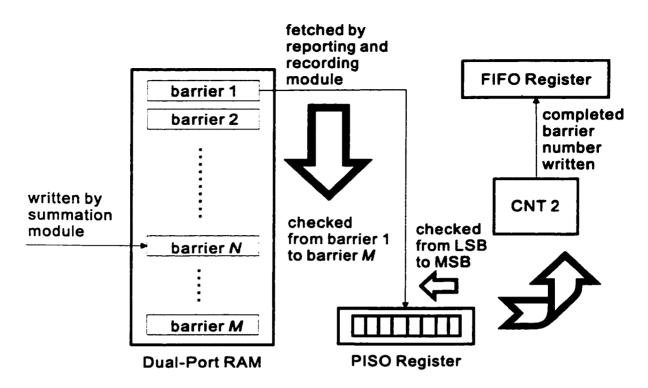

| 5.4  | Reporting and Recording Module                                 |

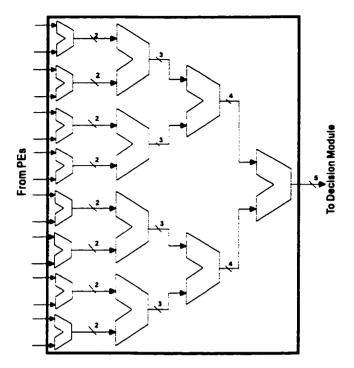

| 5.5  | Responder Count Encoder                                        |

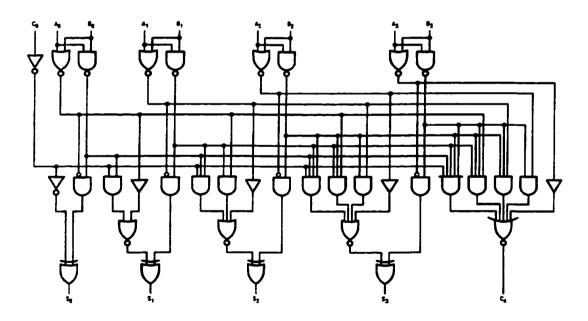

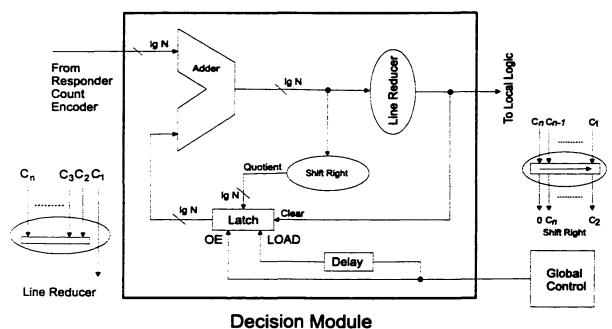

| 5.6  | Decision Module                                                |

| 5.7  | Procedure Applied by DSBC Logic to Detect Completed Barrier 79 |

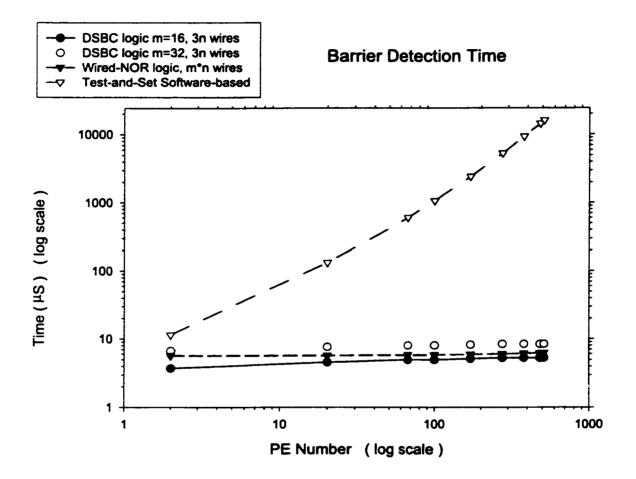

| 5.8  | Detection Time Comparison                                      |

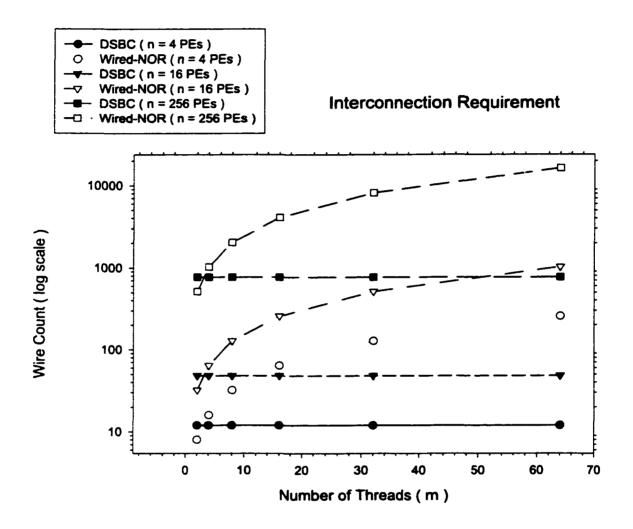

| 5.9  | Interconnection Requirement Comparison                         |

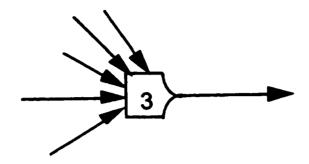

| 5.10 | 5 Input/Threshold 3 gate [35] 88                               |

| 5.11 | Threshold Gate with Weighted Feedback of (Threshold-1) [35] 88 |

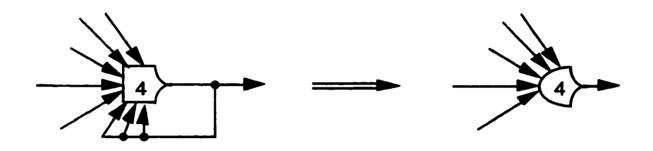

|      | Null Convention Logic Register [35]                            |

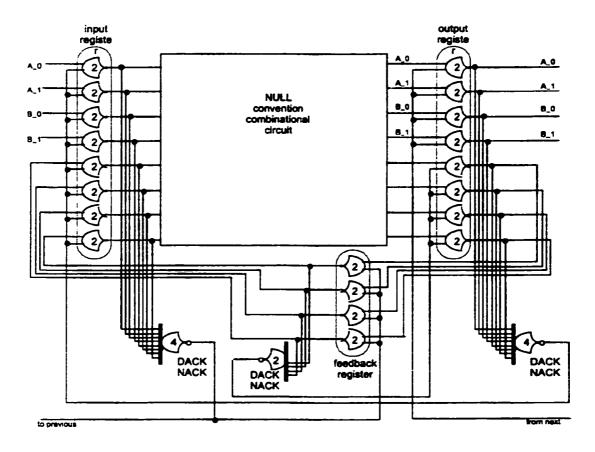

| 5.13 | NCL Combinational Network [35]                                 |

| 5.14 | NCL Sequential Network [35] 91                                 |

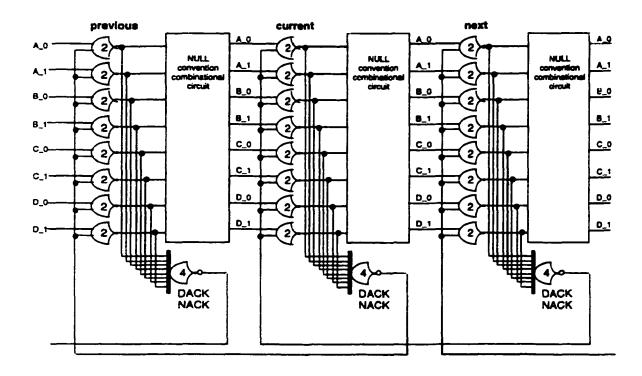

| 5.15 | NCL Version DSBC Logic Basic Layout                            |

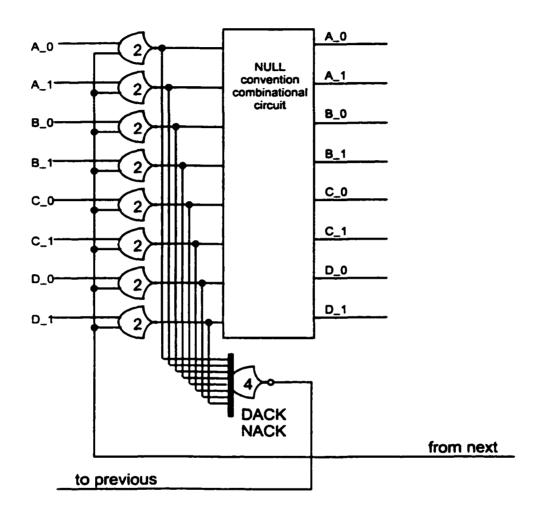

| 5.16 | NCL Version Reporting and Recording Module                     |

| 5.17 | NCL Version Responder Count Encoder                            |

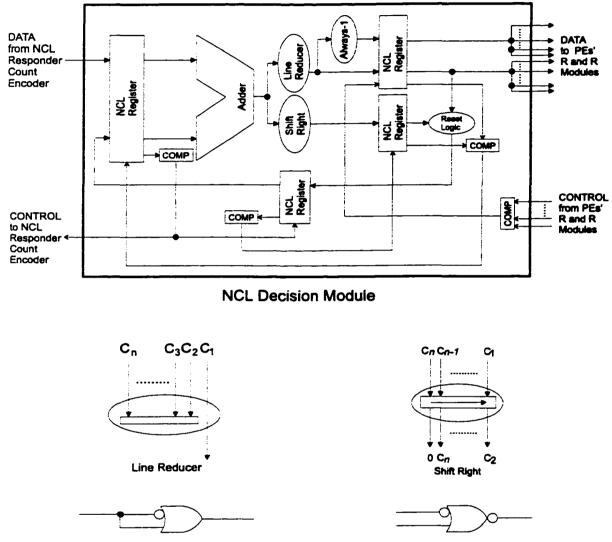

| 5.18 | NCL Version Decision Module                                    |

# **CHAPTER 1**

# INTRODUCTION

Efficient barrier synchronization and termination detection techniques are essential for optimizing throughput in multiple processor architectures. An ensemble of processing elements (PEs) is said to be synchronized, or to have reached a quiescent state [9], upon completion of each interval of concurrent activity. Points at which synchronization occur are referred to as a barriers [20][21][18]. The design objective is to minimize the overhead required to enforce completion of each barrier prior to the resumption of subsequent processing.

## 1.1 The Barrier Synchronization Problem

Figure 1.1 shows a code fragment containing three statements, labeled S1, S2, and S3, which invokes three distinct processes labeled P1, P2, and P3. Let I(S) and O(S) denote the set of input and output variables, respectively, of statement S. Statements

cobegin; S1: x:=P1(a); S2: y:=P2(b); coend; ⇐ "Barrier" (point at which interprocess synchronization must occur) S3: P3(x,y);

Figure 1.1: Parallelizable Code Fragment Requiring Synchronization

1

S1 and S2 have no input, output, nor control dependencies, and hence by Bernstein's conditions [19]:

$$I(S1) \cap O(S2) = I(S2) \cap O(S1) = O(S1) \cap O(S2) = \emptyset$$

An empty intersection implies that S1 and S2 can be executed simultaneously on separate processors. On the other hand, statement S3 can only be executed correctly after both S1 and S2 have terminated since:

$$I(S3) \cap O(S1) = \{x\}$$

and  $I(S3) \cap O(S2) = \{y\}$

The barrier which corresponds to the completion of the concurrent processing, which must occur before S3 is initiated, is indicated by the coend statement shown in Figure 1. The processing tasks between barriers are executed by multiple Processing Elements (PE's) within the machine. PE's may execute these tasks simultaneously without impacting correctness, but only if the barriers are properly enforced. Since some barriers may only involve a subset of the processes or resources in the system, those which actually take part in a specific barrier are delineated as *participating tasks* or *participating PEs*, accordingly.

#### **1.2** Significance of Synchronization and Quiescence Detection

Parallel and distributed processing techniques frequently offer cost-effective ways to boost throughput.[8][52][47] As networking technology matures and environments such as the Internet rapidly expand, distributed computing is an effective method to fully utilize the available resources to increase throughput [3][1][2]. Synchronization is a fundamental issue to both parallel and distributed computation. Its performance effects the overall performance the parallel and distributed multiprocessor systems profoundly since any idle processor in the system cannot proceed to execute the next procedure before the synchronization has been completed. Even if the processors can be reactivated to process tasks of another application to utilize the processing cycles, overheads are incurred. An ineffective termination detection scheme will exchange more messages which congest the communication channels and effect the transmission of messages required by the underlying computation. Therefore the quiescence detection process plays an important role in parallel and distributed computing.

# **1.3** Application-Driven Synchronization Requirements

Characteristics which influence selection of a barrier mechanism include the application's task granularity between barriers, number of simultaneous barriers. and task creation/allocation strategy.

# 1.3.1 Granularity of the Application Tasks

Task granularity refers to the number and relative complexity of the operations within each concurrent process. The coarseness or fineness of granularity determines the interval of productive execution between barriers. As the tasks requiring synchronization become increasingly fine-grained, the relative impact of synchronization overhead on processing throughput becomes magnified. Thus, frequently synchronized applications are less able to tolerate the latency at which barriers are detected and may require hardware solutions to the synchronization problem.

### **1.3.2** Degree of Thread Concurrency

Singly-threaded applications require at most one barrier at any instant while multithreaded applications may take advantage of concurrent barriers which are active simultaneously. For example, in a multi-user environment, each user's job involves tasks contributing towards distinct barriers. Since there are no data dependencies between tasks from different users, these tasks could be executed simultaneously if the synchronization mechanism could distinguish between barrier signals. Likewise, single-user applications may also contain multiple sets of tasks contributing to a different active barrier for each of its threads.

# 1.3.3 Apriori Knowledge of PE Participation

Knowledge of whether a PE will participate in a barrier may not be readily available at compile-time. Applications in which the number of participating tasks and/or their processor binding can be determined prior to execution are said to exhibit *procedural task creation*. On the other hand, applications which dynamically select the PE's which will participate in the barrier and/or generate new processes based on run-time conditions are capable of *adaptive task creation*. Applications requiring synchronization support for adaptive process creation include Remote Procedure Calls, recursive algorithms, and dynamic search strategies.

Additionally, adaptive process creation may create a *launch-in-transit hazard*. This refers to the situation when all processors are idle, yet a message is in transit from one PE to another that will launch a new task or subprocess upon arrival at its destination. While all processors appear to be idle, the barrier is not actually reached. Launch-in-transit messages can be difficult to track, yet their proper accounting is vital for enforcing the barrier and ensuring correctness of program execution. Launch-in-transit hazards can arise on distributed-memory architectures such the iPSC hypercube, nCUBE, and others where the synchronization technique lacks a global snapshot of processor activity.

4

## 1.4 Architecture-Driven Synchronization Requirements

Each phase of the synchronization algorithm must accommodate the primary architectural features of the target machine such as its communication mechanism. level of hardware support for synchronization, and various machine-specific parameters.

#### 1.4.1 Interprocessor Communication Strategy

Since shared-memory architectures provide a common region of the address space which can be accessed by multiple PE's, applicable barrier techniques involve the use of *global synchronization variables*. The design objectives involve minimizing contention for access to these variables. On the other hand, distributed memory machines must exchange *synchronization messages* through the machine's interconnection network. Thus, design objectives for distributed-memory synchronization schemes involve minimizing message traffic, transit times, and computational overhead required to process these messages.

# 1.4.2 Machine-Specific Configuration Parameters

Irregardless of whether a shared or distributed memory model is used. quantities such as the ratio of computation-to-communication speed can be determining factors in the applicability of a barrier technique. For instance, a synchronization algorithm may be applicable to a distributed- memory architecture, but the relative cost of communication on a particular machine may make certain approaches intractable. Similarly, the number of PE's in the machine, PE interrupt support. and spinlock availability will influence which barrier approaches are appropriate.

Figure 1.2: Classification Scheme based on Functionality of Barrier

# 1.4.3 Availability of Barrier Hardware

The use of dedicated hardware to enforce barriers can significantly reduce synchronization latencies. The hardware design issues involve minimizing the logic requirements per PE and reducing interprocessor wiring complexity, while optimizing flexibility. Use of dedicated barrier hardware can be prohibitive except in new machine designs since many commercial systems offer little hardware support and retrofitting may sacrifice the application's portability.

### **1.5** Taxonomy of Termination Detection Techniques

# 1.5.1 Capability Categories

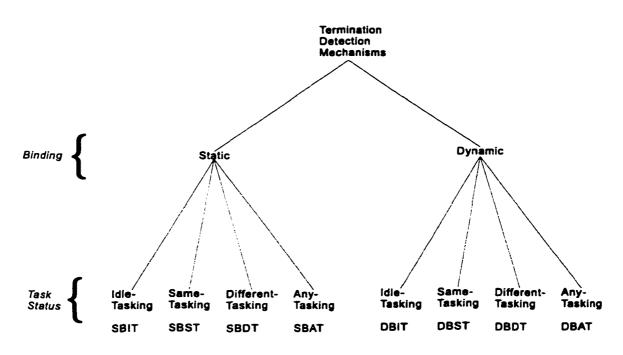

After extensive studying of various barrier synchronization mechanisms, we propose the novel categorization of them as in Figure 1.2 based on their features. First they are grossly classified as *static-binding* and *dynamic-binding* according to the way in which they allocate PEs and schedule processes. Only mechanisms which can both allocate PEs and schedule processes dynamically are categorized as dynamicbinding. Although some approaches schedule processes dynamically, they fulfill the tasks on fixed tree of PEs; hence they are still classified as static-binding. The barrier synchronization mechanisms are further classified as *idle-tasking*, *same-tasking*, *different-tasking*, and *any-tasking* under each binding scheme based on how they behave after they enter the barrier. If all joining PEs cannot be reactivated for other tasks after they enter the barrier, the mechanism is classified as *idle-tasking* capable. If joining PEs can be reactivated for other tasks in the same barrier after they enter the barrier, the mechanism is classified as same-tasking capable. If joining PEs can only be reactivated for other tasks in other barriers after they enter the barrier, the mechanism is classified as different-tasking capable. If joining PEs can be reactivated for other tasks in either the same barrier or other barrier after they enter the barrier, the mechanism is classified as any-tasking capable. Combined with binding calassification, there are eight categories for barrier synchronization mechanisms.

#### 1.5.2 Class Hierarchy

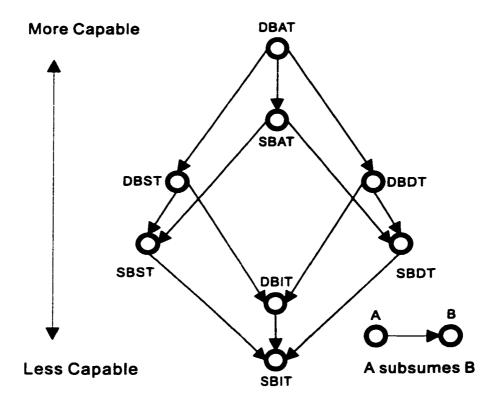

Figure 1.3 shows a hierarchy of capabilities for the barrier classes defined in the previous section. In particular, class A is said to *subsume* class B if the mechanisms in class A can perform the operations of those in class B. For example, a technique in the DBAT class can correctly execute any synchronization operation supported by any other class. Therefore, the DBAT class subsumes all other classes. If one can realize DBAT class capability with a cost and efficiency comparable to any other class, then he will have provided a general technique for the barrier synchronization problem.

Figure 1.3: Hierarchy of Barrier Classes

# 1.6 Organization of the Dissertation

A novel capability taxonomy of termination detection algorithms along with a capability class hierarchy resulting from it are proposed in Chapter 1 to facilitate the analysis of thirteen popular termination detection algorithms which are introduced and investigated in Chapter 2. The classification assists in identifying the capability of existing termination detection techniques and helps to shape the requirements for an optimal algorithm. Next, the optimality of termination detection algorithms is studied and derived in Chapter 3 by refining existing lower bound of message complexity in termination detection algorithms. A new lower bound of termination detection algorithms is proposed as a result of the optimality analysis, which also serves as the ultimate goal of our approaches for new termination detection algorithms. A software approach referred to as the *Tiered Algorithm* is designed and presented in Chapter 4 following integration of our refinements along with the advantageous features extracted from the examination of other efficient termination detection algorithms. Its performance is shown to approach practical efficiency through comparison with three major algorithms which are intended to be optimal in terms of message complexity. An extension of the same fundamental concept is realized by hardware approach in Chapter 5. The advantages of the Distributed-Sum Bit-Comparison Logic are revealed by contrasting its performance with those of a software scheme and another major hardware design. A delay-insensitive version of the DSBC Logic, which eliminates timing concerns, is also developed with NULL Convention Logic technique. In Chapter 6. conclusion is summarized and a direction for future work is outlined.

# **CHAPTER 2**

# **PREVIOUS WORK**

#### 2.1 Overview

The termination detection issue in parallel and distributed computations has been extensively researched in the past and many termination detection algorithms have been proposed, both in software and hardware. Major designs in the literature are introduced and classified according to the capability category proposed in previous Chapter in the following sections. The evolution of termination detection techniques is implicitly covered and sheds a light to the requirements of an optimal termination detection algorithm.

### 2.2 Static-Binding Idle-Tasking Capable Techniques

#### 2.2.1 Butterfly Barrier

The Butterfly Barrier [20] [21] [18] [6] is an approach to barrier synchronization which is free of hot spots and incurs a delay which grows logarithmically with the number of processors. This technique builds upon a two-processor synchronization kernel which is illustrated in Figure 2.1. Statement S1 guarantee that each processor will not continue to S2 until the other processor has completed S4 from the previous

| P1                        | P2                        |

|---------------------------|---------------------------|

| S1: while $(f0 \neq 0)$ ; | S1: while $(f1 \neq 0)$ ; |

| S2: $f0 = 1;$             | S2: $f1 = 1;$             |

| S3: while $(f1 \neq 1)$ ; | S3: while $(f0 \neq 1)$ ; |

| S4: $f1 = 0;$             | S4: $f0 = 0$ ;            |

Figure 2.1: 2-Process Butterfly Barrier

barrier. This prevents a race condition which can occur in the presence of very short code segments or with processors which are subject to program interruption. S2 signals entry of the barrier code to the other processor. In S3, the processor waits until S2 has been executed by the other processor. Finally, S4 is used re-initialize the flags f0 and f1 for the next barrier.

The author proposed using this two-processor Butterfly lock to synchronize three or more processors using the structure shown in Figure 2.2. Multiple instances of the two processor lock are employed to prevent any processor from proceeding beyond the barrier until all processors have reached the barrier. This structure can be readily expanded to synchronize  $2^i$  or more processors where i > 1. If the number of processors is not a power of 2, then it is possible to circumvent this restriction by having processors in the network stand-in for missing processors.

Note that this barrier synchronization technique does not rely on accessing a shared variable common to all processors. Each flag modified by a single process is polled by only one other process. However, it is important to consider the location of the set of synchronization flags used. If all of the flags are stored in a region of memory which requires shared hardware for access (i.e. buffers, busses. memory devices. etc.) then a contention problem may still occur. This barrier detection method is classified as SBIT. The technique is static-binding because it must embed the barrier synchronization codes in each process; that means each process has to be

Figure 2.2: Butterfly Barrier Expanded to Support Multiple Processors

known in advance. It is classified as idle-tasking since all PEs reaching the barrier code shown in Figure 2.1 must wait at S3 for the paired PE to execute S2.

### 2.2.2 U-cube Tree Algorithm

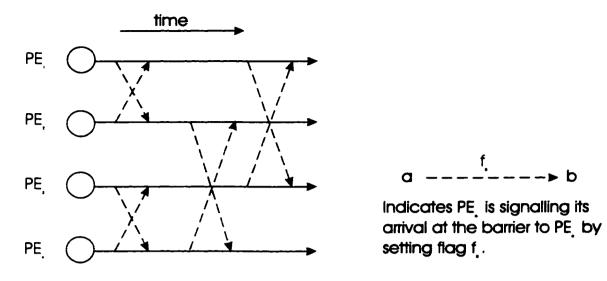

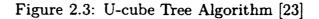

The U-cube Tree Algorithm [23] is designed for the wormhole-routed [39] hypercube multicomputers by taking advantage of the feature that message latency is almost insensitive to the distance between the source and destination nodes in wormhole routing. Therefore it may not be efficient if implemented on other interconnection network. The algorithm uses a barrier processor to do termination detection, which can be a joining PE or a dedicated processor. The algorithm takes part in both the distribution phase. in which the barrier processor either broadcast or multicast the message to all the joining PEs, and the reduction phase, in which the joining PEs report to the barrier processor for termination detection. The algorithm first organizes the joining PEs as a dimension-ordered chain which will be explained shortly. In the distribution phase, the barrier processor unicasts to one of the joining PE first, then every PE which has received a message unicasts the message to one of the PEs which have not received messages yet in the following steps until all joining PEs receive a message. It requires exactly  $k = \lceil \lg(m+1) \rceil$  steps. The reason for using dimensionordered chain is to guarantee that the paths followed by concurrent messages in the U-cube tree do not go through any common channel. The dimension-ordered chain is formed by the three following definitions [23]. Let  $\sigma_{n-1}(x)\sigma_{n-2}(x)\ldots\sigma_0(x)$  represent the binary address of a node.

**Definition 1** The binary relation "dimension order," denoted  $<_d$ , is defined between two nodes x and y as follows:  $x <_d y$  if and only if either x = y or there exists a j such that  $\sigma_j(x) < \sigma_j(y)$  and  $\sigma_i(x) = \sigma_i(y)$  for all  $i, 0 \le i \le 1$ .

**Definition 2** A sequence  $\{d_1, d_2, d_3, \ldots, d_m\}$  is a dimension-ordered chain if and only if all the elements are distinct and the sequence is dimension-ordered, that is, if  $d_i <_d$  $d_j$  for all i, j, such that  $1 \le i \le j \le m$ .

**Definition 3** A sequence  $\{d_1, d_2, d_3, \ldots, d_m\}$  is called a  $d_0$ -relative dimension-ordered chain if and only if  $\{d_0 \bigoplus d_1, d_0 \bigoplus d_2, \ldots, d_0 \bigoplus d_m\}$ , is a dimension-ordered chain.

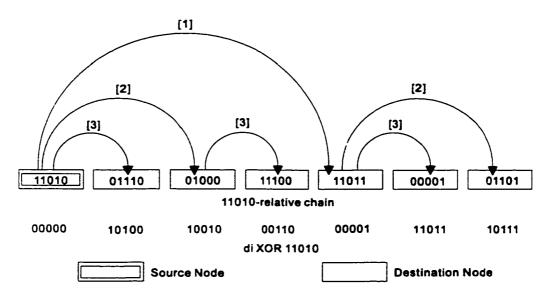

The U-cube Tree Algorithm is shown in Figure 2.3. An example based on (11010)relative dimension-ordered sequence {01110, 01000, 11100, 11011, 00001, 01101} is given in Figure 2.4. In the reduction phase, the algorithm just use a reverse U-cube Tree. This algorithm is classified as SBIT. It is static-binding because it needs to know the joining PEs to arrange the dimension-ordered sequence before it starts. It is idle-tasking since all PEs have to wait for the barrier processor for new messages.

#### Algorithm: The U-cube Tree Algorithm

Input: $d_0$ -relative cube ordered address  $\{d_{left}, d_{left+1}, \dots, d_{right}\}$ , where  $d_{left}$  is the local address. Output: Send  $\lceil \lg(right - left + 1) \rceil$  messages Procedure: begin  $p = \lceil \lg(right - left + 1) \rceil$  messages while  $\{p > 0\}$  do  $center = left + \lceil \frac{right - left + 1}{2} \rceil$ ;  $D = \{d_{center}, d_{center+1}, \dots, d_{right}\}$ ; Send a message to node  $d_{center}$  with the address field D; right = center - 1; p = p - 1; endwhile end:

Figure 2.4: Example for U-cube Tree Algorithm

#### Procedure start;

(\* performed by the root node when it decides to detect termination of the underlying computation \*)

begin

mystate  $\leftarrow$  DT;

for each outgoing network link *ln* do begin color *ln*; Send a *warning* message on *ln* end

end:

Procedure receive\_warning;

(\* performed when a node p. receives a warning message from its neighbor  $q^{*}$ )

#### begin

color the incoming link (q, p); if (mystate  $\langle \rangle$  DT) then begin mystate  $\leftarrow$  DT; for each outgoing link ln do begin color ln; Send a warning message on lnend end

end;

Figure 2.5: Procedures used in CV Algorithm [10]

**Procedure** send\_message(q : neighbor); (\* performed when a node p wants to send a message to its neighbor q \*)

begin

Push TO(q) on the stack; send the actual message to node q

end:

**Procedure** receive\_message(y : neighbor); (\* performed when a node x receives a message from its neighbor neighbor y on the link (y, x) that was colored by  $x^*$ )

begin

receive message from y on the link (y, x)if (link (y, x) has been colored by x) then push FROM(y) on the stack

end:

Figure 2.6: Procedures used in CV Algorithm [10]

## 2.3 Static-Binding Same-Tasking Capable Techniques

## 2.3.1 CV Algorithm

The procedures used in the CV algorithm [10] are given in Figures 2.5 to 2.7. The CV algorithm first organizes all the participating processors as a logical spanning tree of PEs. It can start after the underlying computation starts. When the CV algorithm starts, it first flushes every links in the spanning tree to take care of messages sent before the algorithm starts; then the root node changes its state to DT (detecting termination) and sends a *warning* message to each of its children and color the link at the same time. In turn, the warning messages are passed through links connected to all its child nodes until all the participating nodes are notified of the detecting termination decision. The CV algorithm maintains a stack in each PE to keep track of sending and received activities on each PE. When a node becomes idle, it examines

Procedure stack\_cleanup:

begin

end;

Procedure idle;

(\* performed as soon as the node becomes idle \*)

begin

$stack_cleanup$

end:

**Procedure** receive\_remove\_entry(y : neighbor); (\* performed when a node x receives a remove\_entry message from its neighbor y \*)

begin

scan the stack and delete the first entry of the form TO(y); if idle **then** stack\_cleanup

end;

Figure 2.7: Procedures used in CV Algorithm [10]

its stack from the top. For every received entry, it sends the *remove\_entry* message to the sender and erase the entry from its stack. It repeats this until it encounters a sending entry. This procedure is defined as *stack\_cleanup*. When a node receives a remove\_entry message, it scans its stack and deletes the sending entry related to this message and repeats the stack\_cleanup procedure as previously described if it is in idle status. A node sends a *terminate* message to its parent when it is idle. its stack is empty, each of its incoming links is colored, and it has received the terminate message from each of its children. When the root node meets the requirements to report terminate message, it declares the termination.

The CV algorithm is classified as SBST. It is treated as static-binding because it is performed on a fixed spanning tree of PEs formed before its execution. The CV algorithm, as originally defined, supports only processor reactivation for the same barrier; hence it is classified as same-tasking.

## 2.3.2 LTD Algorithm

The LTD algorithm [12] [13] is an improvement over the CV algorithm. Its algorithm for all PEs is given in Figure 2.8. The two procedures used in the algorithm are given in Figure 2.9. Like the CV algorithm, it organizes participating processors as a spanning tree of PEs first and it can start after the underlying computation starts. When the root decides to start the algorithm, it changes to DT (detecting termination) status and sends a *start* message to each of its children. In turn, its children send start messages to their own children until all participating processors are notified of the root's decision. Each PE maintains four variables, namely  $in_i$ ,  $out_i$ ,  $mode_i$ , and  $parent_i$ , to apply message counting to decide whether all the messages sent by it have been finished. The integer array,  $in_i[1..n]$ , is used to keep track of the messages which are received from PE 1 to n and have not been finished. The number of messages

```

A1: (Upon sending a basic message to p_i)

out_i := out_i + 1;

A2: (Upon receiving a basic message from p_j)

in_i[j] := in_i[j] + 1;

if (parent_i = \text{NULL}) \land (i \neq 1) then parent_i := j;

A3:(Upon deciding to switch to DT mode) /* for p_1 */

or (Upon receiving a START message) /* for p_i, 2 \le i \le n^*/

mode_i := DT;

for each child p_j of p_i do

send a START message to p_i;

end for

if (p_i \text{ is idle}) then

call respond_minor(i):

call respond_major(i);

end for

A4: (Upon receiving a FINISHED(k) from p_j

out_i := out_i - k;

if (mode_i = DT) \land (p_i \text{ is idle}) then call respond_major(i);

A5:(Upon turning idle)

if (mode_i = DT) then

call respond_minor(i);

call respond_major(i);

end if

```

Figure 2.8: Algorithm for  $p_i, 1 \le i \le n$ , in LTD Algorithm [12]

```

Procedure respond\_minor(i : integer)

begin

for each j \neq parent_i with in_i[j] \neq 0 do

send a FINISHED(in_i[j]) to p_j;

in_i[j] := 0;

end for;

end;

```

```

Procedure respond_major(i : integer)

begin

if (out_i = 0) then

if (i = 1) then report termination

else

send a FINISHED(in_i[parent_i]) to parent_i

in_i[parent_i] := 0;

parent_i := NULL;

end if;

end if;

end;

```

Figure 2.9: Procedures used in LTD Algorithm [12]

sent by j to i is stored in  $in_i[j]$ . The integer,  $out_i$ , records the number of unfinished messages sent by PE i itself. The Boolean variable,  $mode_i$ , shows the status of the processor (DT or NDT). The pointer which indicates where the most recent major message came from is stored in  $parent_i$ . A major message is the message which is received when the processor is idle and has finished all the messages which it sent to other processors, otherwise the received message is defined as a minor message. Whenever a node turns idle, it calls procedures *respond\_minor* and *respond\_major* to detect termination. What procedure *respond\_minor* does is to send one FINISH(k)message to each non-parent node which has sent it messages to inform them of the number of messages which it has finished for them, where k means the total number of messages which it has finished for a specific node before turning idle. This is the largest improvement over the CV algorithm. It uses one FINISH(k) message instead

|          | P  | arei | nt fie | ble |    | Chile | d fiel | d  | •    |      |

|----------|----|------|--------|-----|----|-------|--------|----|------|------|

| Group ID | +X | -X   | +Y     | -Y  | +X | -X    | +Y     | -Y | Node | Туре |

| Group ID | +X | -X   | +Y     | -Y  | +X | -X    | +Y     | -Y | Node | Туре |

| Group ID | +X | -X   | +Y     | -Y  | +X | -X    | +Y     | -Y | Node | Туре |

**Status Register Set**

| Child field |          |          |    |    |    |         |

|-------------|----------|----------|----|----|----|---------|

| Group ID    | Ρ        | +X       | -X | +Y | -Y | Message |

| Group ID    | Ρ        | +X       | -X | +Y | -Y | Message |

|             | <u> </u> | <b>1</b> | :  | L  |    |         |

| Group ID    | Ρ        | +X       | -X | +Y | -Y | Message |

**Working Register Set**

Figure 2.10: Status and Working Registers

of k remove\_entry messages as in the CV algorithm to save (k - 1) messages. As for the procedure *respond\_major*. it checks if all the sent messages have been finished and sends one FINISH(k) message to parent node if all the messages sent by it are finished. After the root turns idle and finds out that all the messages it sent out are finished, it concludes the termination. It is classified as SBST with the same rationale for the CV algorithm.

## 2.4 Static-Binding Different-Tasking Capable Techniques

### 2.4.1 Collective Synchronization Tree

The Collective Synchronization (CS) Tree algorithm [29] implements on 2D mesh networks. A CS tree is built on joining PEs before the algorithm begins. The CS

tree is a logic tree which is rooted at the central node of the joining PEs and links all member nodes together. In short, a CS tree is built by dividing the joining PEs into four quadrants according to their positions in the 2D mesh network and finding the central node as the root. Then it initialize the routers to set up the CS tree in hardware. To record the parent-child relationship in the CS tree, the routers use two sets of centralized registers, namely status and em working registers, which are shown in Figure 2.10 [29]. each status register contains two fields, parent and child, and each has four bits (+X, -X, +Y, -Y). A "1" in any bit in a field indicates that the parent or child node can be reached through the corresponding port. The node type indicates the role of the node in the CS tree, which can be the central node, a leaf. an internal node, or an intermediate node. The working status is used to record whether the message from the local processor (P field) or child nodes (child field) has arrived. Both registers for the same barrier are identified by the *Group ID*, hence the CS Tree algorithm can implement on different barriers simultaneously by applying different group ID. The operations of all nodes in the algorithm are summarized in Table 2.1. In general, the leaf nodes reports to their parents after they finish their tasks: the internal and intermediate nodes wait for messages from all their children and the local processor before they report to their parents; the central node declares the completion of the barrier after it receives messages from all its children. The CS Tree algorithm is classified as SBDT. It is static-binding because it must know the joining PEs a-priori to build the CS Tree. It employs different register sets for different barriers hence it has different-tasking ability.

### 2.4.2 Fetch-and-Add

The Fetch-and-Add (F & A) primitive [19] [45] is a hardware feature which allows a PE to indivisibly read and increment a counting variable stored in shared memory.

| Node Type    | Operations                                                                                                                                                                                                      |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Leaf         | <b>RA1:</b> Receive a Rmsg from local processor and forward it through the port specified in SReg[PF].                                                                                                          |  |  |  |

| Internal     | <b>RB1:</b> Receive a Rmsg (perhaps from local processor) and set the bit corresponding to its input port in WReg. If $SReg[CF] \neq WReg[CF]$ or $WReg[P]$ is not set, then discard the message and go to RB1. |  |  |  |

|              | <b>RB2</b> :Forward the message through the port specified in SReg[PF].                                                                                                                                         |  |  |  |

|              | RB3:Reset WReg.                                                                                                                                                                                                 |  |  |  |

| Central      | RC1:Same as RB1.                                                                                                                                                                                                |  |  |  |

| Central      | RC2:Reset WReg and notify local processor.                                                                                                                                                                      |  |  |  |

| Intermediate | <b>RD1:</b> Receive a Rmsg and set the bit corresponding to its input port in WReg[CF]. If $SReg[CF] \neq WReg[CF]$ , then discard the message and go to RD1.                                                   |  |  |  |

|              | RD2:Same as RB2.                                                                                                                                                                                                |  |  |  |

|              | RD3:Reset WReg.                                                                                                                                                                                                 |  |  |  |

Table 2.1: Operations in the Router for CS Tree [29]

```

num\_at\_barrier = F\&A(counter, 1);

(num_at_barrier < num_expected)

if

while(exit_flag == 0);

else

{sequential code};

exit_flag = 1;

```

endif;

Figure 2.11: Fetch and Add Barrier Code

If the number of processes converging on a barrier is known a-priori, a counting variable can be used to detect the barrier. An example of the code executing on the converging processes is shown in Figure 2.11. As each processor reaches the point in its operation where synchronization is required, it increments and tests the counting variable using an F & A instruction. When a process detects that the counting variable has reached the expected final value, the barrier has been reached. Both *counter* and *exit\_flag* are initialized to zero prior to executing the barrier code. Note that the process which detects the barrier (the last converging process to reach the barrier) can execute sequential code, since the *else* portion of the *if* statement can be executed by a process only if all other converging processes are in a busy-wait condition testing the exit\_flag. The use of this primitive for barrier synchronization can result in significant hot spots due to contention for both the counting variable and the exit\_flag. The detection latency encountered when using the F & A primitive is determined by the access time of the counting variable and the test for the terminal count by the last PE reaching the barrier. This synchronization method is SBIT per se because joining PEs must be known in advance and all but the last PE reaching the barrier code shown in Figure 2.11 must wait for the exit\_flag to be set. However concurrent barriers can be accommodated by duplicating the barrier code on multiple sets of PEs, each using a different counting variable. Thus a PE can be reactivated for a different barrier. Therefore we classified it as SBDT to show that most SBIT techniques can be easily upgraded to SBDT techniques.

# 2.5 Static-Binding Any-Tasking Capable Techniques

So far we have not discovered any SBAT mechanism in literature. However, some mechanisms in other category can easily be adapted to SBAT capability. For example, both CV and LTD algorithms can be extended to be SBAT capable by attaching

Figure 2.12: Simple AND Gate Barrier

barrier ID to each message; then multiple barriers can be executed simultaneously without ambiguity.

## 2.6 Dynamic-Binding Idle-Tasking Capable Techniques

### 2.6.1 AND Gate Barrier

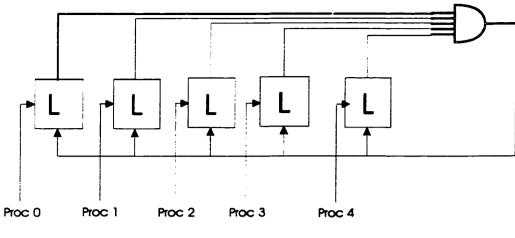

Ghose and Cheng propose a simple AND gate hardware barrier [24] as shown in Figure 2.12. Each processor notifies of its arrival at the barrier by setting a local latch. This figure shows a 5 processor synchronization circuit. The block containing the symbol is a latch set by the processor when the barrier has been reached by the processor. The output of all of the latches are AND-ed together, generating a global reset signal to all latches. It is classified as DBIT. It is dynamic-binding because it does not need to know the participating PEs in advance. It is idle-tasking because every joining PE has to wait for the global reset signal after it has reached the barrier.

Figure 2.13: NAND Tree in TTL\_PAPERS

### 2.6.2 TTL\_PAPERS

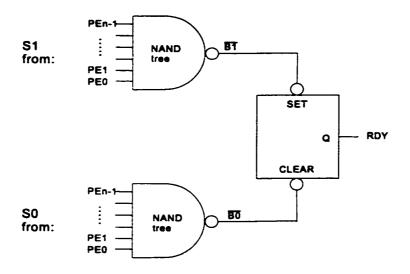

The TTL\_PAPERS [28] [40] [41] is a simple TTL hardware implementation of PA-PERS (Purdue's Adapter for Parallel Execution and Rapid Synchronization) [30]. It is plugged into the parallel ports of all personal computers in the cluster. Conceptually the TTL\_PAPERS employs a AND tree to detect whether every PE has reached the barrier. However there are two serious problems with AND tree in asynchronous barrier. 1. A PE with a small task for the first barrier may reset its signal before all other PEs signal for completion of the first barrier. They end with waiting for a signal which is gone. 2. A PE which finishes the first barrier faster may set the signal high again before other PEs clear their signals for the first barrier. The TTL\_PAPERS adopts the two NAND trees and a one-bit register design as in Figure 2.13 to handle the two problems. To solve the first one, it adds the one-bit register. When all PEs signal completion of a barrier, the output of the first NAND tree set the register to one; then every PE can test RDY to know whether the barrier has been reached. To solve the second problem, it adds a second NAND tree. Any PE sets signal S0 after

| Signaling Condition                                            | Value Submitted |

|----------------------------------------------------------------|-----------------|

| The processor does not want to delete from nor insert into the |                 |

| shared queue.                                                  | 0               |

| The processor inserts an element into the shared queue.        | -1              |

| The processor deletes an element from the shared queue.        | 0               |

| The interface processor fails to delete an element from the    |                 |

| shared queue.                                                  | +1              |

| PE is idle.                                                    | +1              |

Table 2.2: SAV Value Returned by PEs

it clears the signal S1. When all the PEs set its S0, the output of the second NAND tree reset the register. Any PE can enter the next barrier after it senses the RDY is zero. The TTL\_PAPERS is classified as DBIT. The fact that it does not need to know the joining PEs makes it dynamic-binding. However every PE has to be committed to the barrier makes it idle-tasking capable.

# 2.7 Dynamic-Binding Same-Tasking Capable Techniques

### 2.7.1 Simultaneous Access Variable

The Simultaneous Access Variable (SAV) [22] technique is a simultaneous access design which provides idle processor reactivation and termination detection capabilities for the shared-memory architecture. The basic idea is: The SAV algorithm organizes PEs as a binary tree and uses a shared queue to store spawned tasks. The values sent to the SAV by every PE under different situations are tabulated in Table 2.2. Every PE keeps track the accumulated SAV of the subtree which is rooted at itself and reports it to its parent. The SAV acts like a counter which counts the difference of the idle PEs and the tasks inserted into the shared job queue. If the value of SAV is greater than zero, there are more idle PEs than the tasks inserted to the queue; otherwise there are more spawned tasks than available idle PEs. The  $\begin{array}{l} U_l \leftarrow U_r \leftarrow 0; \\ R \leftarrow R_l + R_r; \\ \textbf{case} \\ R_l > 0 \text{ and } R_r > 0; \\ U \leftarrow \min(U_p, R); \\ U_l \leftarrow |\frac{R_l}{R} \times U|; \\ U_r \leftarrow |\frac{R_r}{R} \times U|; \\ R_l > 0 \text{ and } R_r \leq 0; \\ U_l \leftarrow \min(U_p - R_r, R_l); \\ R_l \leq 0 \text{ and } R_r > 0; \\ U_r \leftarrow \min(U_p - R_l, R_r); \\ \textbf{endcase} \\ R \leftarrow R - U_p; \\ \textbf{send } R \text{ to parent}; \\ \textbf{send } U_l \text{ to left child}; \\ \textbf{send } U_r \text{ to right child}; \end{array}$

Figure 2.14: SAV Algorithm [22]

termination is reached when the accumulated SAV at the root equals the number of the PEs in the system. The PEs at odd and even levels execute alternately and the algorithm for each active PE is listed in Figure 2.14. Each PE maintains four sets of registers, each consisting of R and U registers. Three sets of registers are for information received from or intended for the left child, the right child, and parent respectively and they are denoted by the subscripts of l, r, and p respectively. The remaining set is for its own use. When a PE which is a left child sends R to its parent, the parent stores it in  $R_l$ ; otherwise it is stored in  $R_r$ . On the other hand, the value received from the parent node is stored in  $U_p$ . The value of  $U_p$  is the number of tasks sent by its parent which may be consumed in this subtree and  $U_p \ge 0$ . Every PE processes according to cases based on the values of  $R_l$  and  $R_r$ . When  $R_l > 0$  and  $R_{\tau} > 0$ , which means both child subtrees have more idle PEs than spawned tasks, tasks from its parent are shared among two children proportionally. If  $R < U_p$ , only R of  $U_p$  are shared; the rest are used by its parent. If  $R_l > 0$  and  $R_r \leq 0$ , which means left child subtree has more idle PEs and right child subtree has more tasks to be consumed, the excess tasks from the right child subtree and the parent can be dispatched to the left child subtree. The case  $R_l \leq 0$  and  $R_{\tau} > 0$  is symmetric to the previous case. When both child subtrees have more tasks than idle PEs, i.e. when  $R_l < 0$  and  $R_r < 0$ , the excess tasks from both child subtrees together with the tasks from the parent are dispatched to its parent. When  $R \leq 0$  at the root, there are still tasks to be consumed. When R > 0 at the root, there are more idle PEs than the tasks to be consumed. When R at the root equals the number of PEs in the system, which means all PEs are idle, the termination has been reached. The SAV algorithm is classified as DBST. It is dynamic-binding because the joining PEs do not have to be known in advance. It is same-tasking because PEs can only be reactivated for the same barrier.

# 2.7.2 The Counting Algorithm

The Counting Algorithm [31] is a two-phase distributed termination detection algorithm. The pseudo codes for both phases are listed in Figure 2.15. A copy of the algorithm runs on every PE. All participating PEs are organized as a spanning tree. Every PE keeps track of the created and processed tasks locally with the variables  $n_c$  and  $n_p$  respectively and maintains the accumulated counts of the created and processed tasks of the subtree rooted at itself with the variables  $N_c$  and  $N_p$  respectively. In phase 1, each leaf PE sends the idle message with  $N_c$  and  $N_p$  initialized to  $n_c$ and  $n_p$  respectively after it turns idle. The idle message signifies that each PE in the subtree below has been idle at least once since the last idle message; in contrary to the activity message in phase 2, which is merely a report of creation and processing activities. As for the other PEs, they update the local  $N_c$  and  $N_p$  by adding the  $N_c$ and  $N_p$  sent from their children with the idle message. After receiving idle messages from all its children, a PE sends an idle message with  $N_c$  and  $N_p$ , updated with  $n_c$ and  $n_p$  respectively, to its parent when it turns idle. When the root node has received idle messages from all children and turns idle. it compares  $N_c$  and  $N_p$ . If they match. enters phase 2 because there is a very good chance that the termination has been reached. If not, restart phase 1. In phase 2, every PE sends up an activity message containing new values of  $N_c$  and  $N_p$ . These activity messages are assembled in the same way as in the phase 1. When the root has received activity messages from all children, it compares the old and new values of  $N_c$  and  $N_p$ . If they are the same, it means that there has been no new activities. The root declares termination of the barrier; otherwise restarts phase 1. The Counting Algorithm is classified as DBST. It is dynamic-binding because the joining PEs do not have to be known a-priori. It is same-tasking capable because PEs can only be reactivated to the same barrier.

#### Phase 1()

```

{

N_c = 0; N_p = 0;

wait until (RecdMsgsFromChildren());

add to local N_c and N_p the values received from children.

wait until (Idle());/* wait until this PE has no activation messages */

N_c = N_c + n_c; N_p = N_p + n_p;

if (RootSpanTree())

if (N_c \neq N_p)

Broadcast message to begin Phase 1

else

N_c^{old} = N_c; N_p^{old} = N_p

Broadcast message to begin Phase 2

else

Send message with N_c and N_p to Parent in Spanning Tree

}

Phase 2()

Ł

N_c = 0; N_p = 0;

wait until (RecdMsgsFromChildren());

add to local N_c and N_p the values received from children.

wait until (Idle());

N_c = N_c + n_c; N_p = N_p + n_p;

if (RootSpanTree())

if (N_c^{old} == N_c \text{ AND } N_p^{old} == N_p)

Report Quiescence

else

Broadcast message to begin Phase 1

else

```

Send message with  $N_c$  and  $N_p$  to Parent in Spanning Tree } CreateMessage() $\{n_c + +\}$ ProcessMessage() $\{n_p + +\}$

Figure 2.15: Counting Algorithm [31]

31

Figure 2.16: Wired NOR Barrier

# 2.8 Dynamic-Binding Different-Tasking Capable Techniques

### 2.8.1 Wired-NOR Barrier

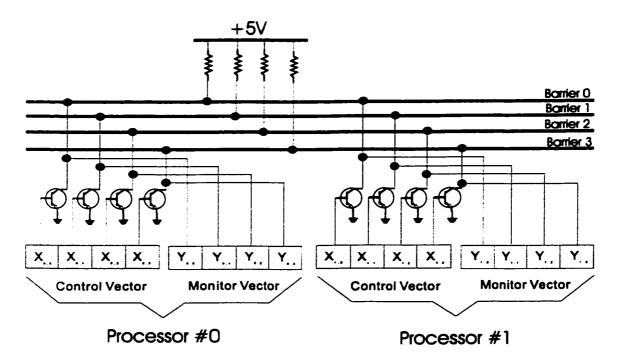

The Wired-NOR Barrier is a distributed and hardwired barrier architecture which supports both intracluster and intercluster synchronization [26] [25]. An example supporting 4 barriers with 2 PEs is shown in Figure 2.16. The description for general case follows. There are *m* barrier wires and each supports an independent barrier at the same time. Physically every barrier wire is connected to *n* PEs, where *n* is the size of the system or cluster. Each PE *i*, where  $1 \le i \le n$ , uses a *control vector*  $X_i =$  $(X_{i,1}, X_{i,2}, \dots, X_{i,m})$  and a *monitor vector*  $Y_i = (Y_{i,1}, Y_{i,2}, \dots, Y_{i,m})$  for synchronization control. These vectors are mapped into the shared memory or distributed to special registers in each processor board. Thus, they are program accessible from each PE. Each barrier wire, labeled as *j* for  $1 \le j \le m$ , is connected to *n* NPN bipolar transistors [50], associated with *n* PEs separately. Changing a view point, every PE contains *m* transistors tied to *m* barrier wires. At each PE *i*, the base of each transistor is connected to a control bit  $X_{i,j}$ ; the collector of the same transistor is monitored by a monitor bit  $Y_{i,j}$ . When a barrier exists, the corresponding barrier wire is pulled up to the high voltage. Any PE sets its corresponding control bit  $X_{i,m}$ when it enters the barrier. That makes the associated transistor closed and pulls down the voltage the barrier wire. A PE resets its corresponding control bit when it finishes its job for the barrier. A barrier line will be pulled high again only when all transistors connected to it are reset low, which will be sensed by the monitor bit. That performs the wired-NOR logic and also means the barrier is terminated. The Wired-NOR barrier architecture is classified as DBDT. It is dynamic-binding because the participating PEs do not have to be known in advance. It is different-tasking because PEs can only be reactivated to different tasks.

#### 2.8.2 Barrier Synchronization Register Hardware

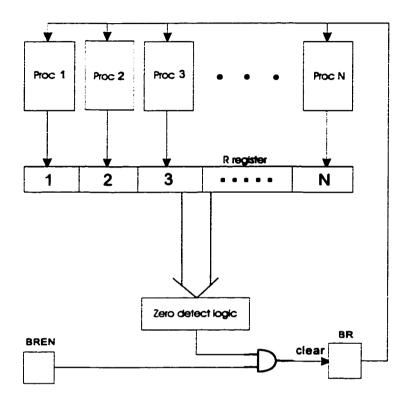

A hardware for supporting barrier synchronization in parallel loops [27] is proposed by Beckmann and Polychonopoulus. The single barrier version supporting N PEs is shown in Figure 2.17. The R register contains a bit for each PE. As a PE completes the loops required to reach the barrier it clears its bit in the R register. The zero detect logic, which is a N-input NOR gate, determines when all bits in the R register are clear. The BR(Barrier Register) is used as a single flag to inform all the PEs of the termination of the barrier. The BREN(Barrier Clear Enable Register), which is ANDed together with the output of the zero detect logic, enables the automatic clear of the BR when all the R bits are 0. The mechanism of this design works as: Initially, BR=1 and R[1..N] and BREN are all 0. Every PE sets its R bit to 1 when it enters the barrier and resets its R bit after it finishes its loops for the barrier.

Figure 2.17: Single Barrier Register Hardware [27]

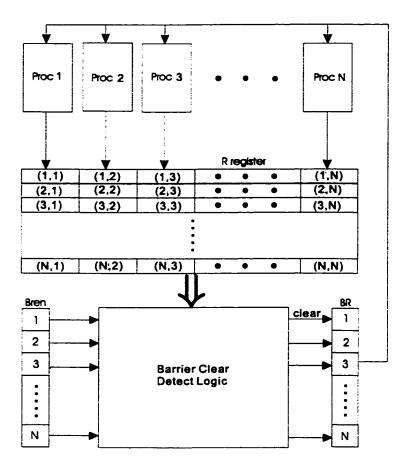

Figure 2.18: Multiple Barrier Register Hardware [27]

The PE dispatched the last iteration sets the BREN to 1 to enable the detecting of termination before executing its loops. After all PEs finish their jobs and reset their corresponding R bits, the BREN and the output of the zero detect logic triggers the clear of the BR, which in turn clears all PEs for next barrier. The multiple barrier version just duplicates the single barrier version and is shown in Figure 2.18. The Barrier Synchronization Register Hardware is classified as DBDT. It is dynamicbinding because it support arbitrary nested loops [27]. It is different-tasking capable because each PE can be reactivated for different tasks.

# 2.9 Dynamic-Binding Any-Tasking Capable Techniques

### 2.9.1 Credit Algorithm

The Credit Algorithm [9] is a global quiescence detection algorithm based on a very simple principle. There are some variants which are not necessarily better than the original design, hence only the original design is described. When the underlying computation begins, the controller which can be on either a dedicated PE or any PE distributes a credit of total value 1 to all processes. These processes either distribute part of their credit share to the new processes spawned by them or return the credit share to the controller when they finish or become *passive* as described in the original paper. The controller declares termination when it regains all the credit. To ensure the credit distribution, the algorithm follows the rules:

- 1. When a process becomes passive it transmits its credit share to the controller.

- When an activating message with credit share C arrives at an active process,

C is transmitted to the controller.

- 3. When an activation message with credit share C arrives at a passive process, C is transferred to the activated process.

- 4. When an active process with credit share C sends an activation message, the process keeps  $\frac{1}{2}C$  and the message gets the other half.

Although not mentioned in the original paper, the Credit Algorithm can easily support multiple barriers by attaching barrier IDs to each credit share. Hence it is classified as DBAT. By the simple principle of credit distribution and the fact that no restrictions exist, obviously the Credit Algorithm is dynamic-binding and any-tasking capable.

### 2.10 Summary

Thirteen major termination detection algorithms are examined in this Chapter. They are classified by the capability category proposed in the previous Chapter. Their individual capability level can be recognized by matching their classification to the hierarchy of termination detection capability class in Figure 1.3. Therefore less capable algorithms can be compared with the more capable algorithms and differences among them can be clearly identified to make substantial improvements.

# **CHAPTER 3**

# OPTIMALITY ANALYSIS OF TERMINATION DETECTION TECHNIQUES

When it comes to find the optimality for termination detection algorithm or analyze their performance, traditionally researchers focus on message complexity. It is because determining the transit time of messages across the network is usually not as practical as the theoretical value. Moreover, messages may not arrive in the order as they were sent out. The concept that increased message traffic causes more performance degradation is correct in this aspect. However, pursuing the least message complexity only does not necessarily ensure the optimal performance as will be shown in the following research. The message delivery architecture and mechanism should also be taken into consideration to provide the optimal overall performance. Especially the messages travel inside local PEs and through the network should be clearly identified to accomplish the optimal performance because there is significant difference in the overhead to transmit both kinds of messages. The notation which will be used in the performance analysis is tabulated in Table 3.1.

| Notation                 | Meaning                                                                                  |

|--------------------------|------------------------------------------------------------------------------------------|

| Epoch                    | duration of processing which occurs between barriers                                     |

| N                        | total number of physical processing elements (PEs) in the parallel machine               |

| N'                       | number of distinct PEs actively processing tasks during an epoch, where $0 \le N' \le N$ |

| E                        | total number of events which happen in an epoch                                          |

| $M_i$                    | number of internal notifications incurred in event $i$                                   |

|                          | total number of logical tasks created during an epoch                                    |

| D                        | maximum depth of task nesting levels during an epoch                                     |

|                          | links between physical processing elements                                               |

| t <sub>send</sub>        | message transit time                                                                     |

| $t_{checkup}^{Protocol}$ | time required for termination criterion checkup of specific protocol                     |

Table 3.1: Notation used in Performance Analysis

### 3.1 Basis

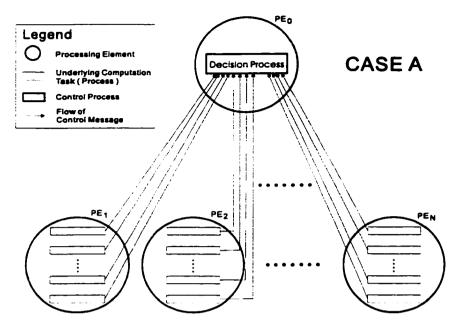

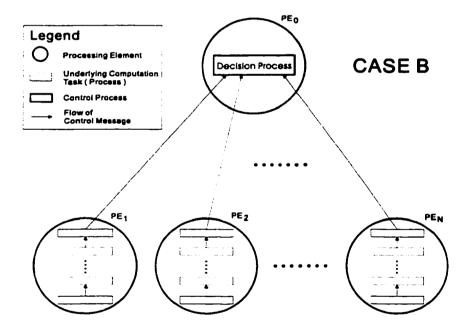

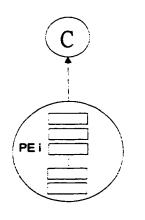

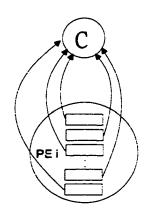

Chandy and Misra established a lower bound of message complexity of T for termination detection algorithms[11]. They built a distributed environment model and used induction to prove that any termination detection algorithm needs to send out at least as many messages as the underlying computation messages to detect the completed barrier. This matches the intuition that every process involved in a barrier in a parallel program needs to send out at least one message to let other processes know its status. Hence T processes initiated by T underlying computation messages need at least T control messages to make other processes understand its status. Theoretically, the optimal value of messages required to detect termination of a barrier in a parallel program with T processes or messages involved is T. That can only happen in a unique case for the dynamic-binding termination detection algorithms as shown in Figure 3.1. In particular, all processes send out one message directly to the centralized control process. However, the time required for detection is expected to be very lengthy and much longer than the theoretical value because of the network traffic caused by so many messages. In practice, it is difficult to achieve the optimal performance bound. Although the same case and an additional case as shown in Figure 3.2 apply to the static-binding termination detection algorithms, the latter will be proved inferior to other case later. Therefore optimality for overall performance will be further explored in the following sections.

# 3.2 Preliminary Analysis

The analysis of Chandy and Misra is based on the individual processes. Therefore the overhead of transmitting a message in their model is uniform. However in realworld parallel and distributed systems, the overhead for delivering an message inside a local node, which is designated as *internal message*, is much less than that of delivering an message out of the local node and across the network, which is designated as *external message*. Hence internal control messages and external control messages should be clearly identified to determine optimal overall performance. As a rule of thumb, opting for as many internal messages, rather than external messages, as possible will achieve more performance gain.